# Building a GameBoy Emulator in Rust

by Baptiste Jacquemot

### About Myself

- French

- Arrived in Switzerland in 2017

- Finished my master at EPFL/ETH in cyber security

- Competitive programmer and CTF player

### The GameBoy

GameBoy 1989

#### GameBoy Color 1998

### Why creating a gameboy emulator?

#### Answer: It's fun!

First year project

- Took 3 months

- No sound, no color, part of the code is already given

This project

- (re)Learn rust

- Do it faster, Go further (run it on bare metal)

### State of the project

#### Done

- MMU, CPU, Joypad, Lcd screen, most common cartridges types

To Do:

- Sound, gameboy color features, other cartridges types

# Where to begin

#### Memory management unit (MMU)

- 16 bits address, 8 bit value

CPU: similar to Zilog z80 and intel 8080.

- 8 8bits registers: A, B, C, D, E, F, H, L

- 216bits registers: SP, PC

|                       | Clock frequency | Release year |

|-----------------------|-----------------|--------------|

| Sharp LR35902<br>core | 4.19MHz         | 1989         |

| Intel 8080            | 3.125 MHz       | 1974         |

https://www.nintendo.co.uk/Support/Game-Boy-Pocket-Color/Product-information/Technical-data/Technic al-data-619585.html

|           | x0                         | x1                         | x2                         | x3                         | x4                          | x5                          | x6                            | x7                         | x8                                | x9                           | xA                         | xВ                         | xC                         | xD                         | xE                            | xF                         |

|-----------|----------------------------|----------------------------|----------------------------|----------------------------|-----------------------------|-----------------------------|-------------------------------|----------------------------|-----------------------------------|------------------------------|----------------------------|----------------------------|----------------------------|----------------------------|-------------------------------|----------------------------|

| 0x        | NOP<br>1 4                 | LD BC, d16<br>3 12         | LD (BC), A<br>1 8          | INC BC<br>1 8              | INC B<br>1 4<br>Z 0 H -     | DEC B<br>1 4<br>Z 1 H -     | LD B, d8<br>2 8               | RLCA<br>14<br>000C         | LD (a16), SP<br>3 20              | ADD HL, BC<br>1 8<br>- 0 H C | LD A, (BC)<br>1 8          | DEC BC                     | INC C<br>1 4<br>Z 0 H -    | DEC C<br>1 4<br>Z 1 H -    | LD C, d8<br>2 8               | RRCA<br>1 4<br>0 0 0 C     |

| <b>1x</b> | STOP d8<br>2 4             | LD DE, d16<br>3 12         | LD (DE), A<br>1 8          | INC DE<br>1 8              | INC D<br>1 4<br>Z 0 H -     | DEC D<br>1 4<br>Z 1 H -     | LD D, d8<br>2 8               | RLA<br>14<br>000C          | JR r8<br>2 12                     | ADD HL, DE<br>1 8<br>- 0 H C | LD A, (DE)<br>1 8          | DEC DE<br>1 8              | INC E<br>1 4<br>Z 0 H -    | DEC E<br>1 4<br>Z 1 H -    | LD E, d8<br>2 8               | RRA<br>1 4<br>0 0 0 C      |

| 2x        | JR NZ, r8<br>2 12/8        | LD HL, d16<br>3 12         | LD (HL+), A<br>1 8         | INC HL<br>1 8              | INC H<br>1 4<br>Z 0 H -     | DEC H<br>1 4<br>Z 1 H -     | LD H, d8<br>2 8               | DAA<br>1 4<br>Z - 0 C      | JR Z, r8<br>2 12/8                | ADD HL, HL<br>1 8<br>- 0 H C | LD A, (HL+)<br>1 8         | DEC HL<br>1 8              | INC L<br>1 4<br>Z 0 H -    | DEC L<br>1 4<br>Z 1 H -    | LD L, d8<br>2 8               | CPL<br>14<br>-11-          |

| 3x        | JR NC, r8<br>2 12/8        | LD SP, d16<br>3 12         | LD (HL-), A<br>1 8         | INC SP<br>1 8              | INC (HL)<br>1 12<br>Z 0 H - | DEC (HL)<br>1 12<br>Z 1 H - | LD (HL), d8<br>2 12           | SCF<br>14<br>-001          | JR C, r8<br>2 12/8                | ADD HL, SP<br>1 8<br>- 0 H C | LD A, (HL-)<br>1 8         | DEC SP<br>1 8              | INC A<br>1 4<br>Z 0 H -    | DEC A<br>1 4<br>Z 1 H -    | LD A, d8<br>2 8               | CCF<br>14<br>-00C          |

| 4x        | LD B, B<br>1 4             | LD B, C<br>1 4             | LD B, D<br>1 4             | LD B, E<br>1 4             | LD B, H<br>1 4              | LD B, L<br>1 4              | LD B, (HL)<br>1 8             | LD B, A<br>1 4             | LD C, B<br>1 4                    | LD C, C<br>1 4               | LD C, D<br>1 4             | LD C, E<br>1 4             | LD C, H<br>1 4             | LD C, L<br>1 4             | LD C, (HL)<br>1 8             | LD C, A<br>1 4             |

| 5x        | LD D, B<br>1 4             | LD D, C<br>1 4             | LD D, D<br>1 4             | LD D, E<br>1 4             | LD D, H<br>1 4              | LD D, L<br>1 4              | LD D, (HL)<br>1 8             | LD D, A<br>1 4             | LD E, B<br>1 4                    | LD E, C<br>1 4               | LD E, D<br>1 4             | LD E, E<br>1 4             | LD E, H<br>1 4             | LD E, L<br>1 4             | LD E, (HL)<br>1 8             | LD E, A<br>1 4             |

| 6x        | LD H, B<br>1 4             | LD H, C<br>1 4             | LD H, D<br>1 4             | LD H, E<br>1 4             | LD H, H<br>1 4              | LD H, L<br>1 4              | LD H, (HL)<br>1 8             | LD H, A<br>1 4             | LD L, B<br>1 4                    | LD L, C<br>1 4               | LD L, D<br>1 4             | LD L, E<br>1 4             | LD L, H<br>1 4             | LD L, L<br>1 4             | LD L, (HL)<br>1 8             | LD L, A<br>1 4             |

| 7x        | LD (HL), B<br>1 8          | LD (HL), C<br>1 8          | LD (HL), D<br>1 8          | LD (HL), E<br>1 8          | LD (HL), H<br>1 8           | LD (HL), L<br>1 8           | HALT<br>1 4                   | LD (HL), A<br>1 8          | LD A, B<br>1 4                    | LD A, C<br>1 4               | LD A, D<br>1 4             | LD A, E<br>1 4             | LD A, H<br>1 4             | LD A, L<br>1 4             | LD A, (HL)<br>1 8             | LD A, A<br>1 4             |

| 8x        | ADD A, B<br>1 4<br>Z 0 H C | ADD A, C<br>1 4<br>Z 0 H C | ADD A, D<br>1 4<br>Z 0 H C | ADD A, E<br>1 4<br>Z 0 H C | ADD A, H<br>1 4<br>Z 0 H C  | ADD A, L<br>1 4<br>Z 0 H C  | ADD A, (HL)<br>1 8<br>Z 0 H C | ADD A, A<br>1 4<br>Z 0 H C | ADC A, B<br>1 4<br>Z 0 H C        | ADC A, C<br>1 4<br>Z 0 H C   | ADC A, D<br>1 4<br>Z 0 H C | ADC A, E<br>1 4<br>Z 0 H C | ADC A, H<br>1 4<br>Z 0 H C | ADCA, L<br>14<br>Z0HC      | ADC A, (HL)<br>1 8<br>Z 0 H C | ADCA,A<br>14<br>Z0HC       |

| 9x        | SUB B<br>1 4<br>Z 1 H C    | SUB C<br>1 4<br>Z 1 H C    | SUB D<br>14<br>Z1HC        | SUB E<br>14<br>Z1HC        | SUB H<br>1 4<br>Z 1 H C     | SUBL<br>14<br>Z1HC          | SUB (HL)<br>1 8<br>Z 1 H C    | SUB A<br>1 4<br>1100       | SBC A, B<br>1 4<br>Z 1 H C        | SBC A, C<br>1 4<br>Z 1 H C   | SBC A, D<br>1 4<br>Z 1 H C | SBCA, E<br>14<br>Z1HC      | SBC A, H<br>1 4<br>Z 1 H C | SBC A, L<br>1 4<br>Z 1 H C | SBC A, (HL)<br>1 8<br>Z 1 H C | SBC A, A<br>1 4<br>Z 1 H - |

| Ax        | AND B<br>1 4<br>Z 0 1 0    | AND C<br>1 4<br>Z 0 1 0    | AND D<br>1 4<br>Z 0 1 0    | AND E<br>1 4<br>Z 0 1 0    | AND H<br>1 4<br>Z 0 1 0     | AND L<br>1 4<br>Z 0 1 0     | AND (HL)<br>1 8<br>Z 0 1 0    | AND A<br>1 4<br>Z 0 1 0    | XOR B<br>1 4<br>Z 0 0 0           | XOR C<br>1 4<br>Z 0 0 0      | XOR D<br>1 4<br>Z 0 0 0    | XOR E<br>1 4<br>Z 0 0 0    | XOR H<br>1 4<br>Z 0 0 0    | XOR L<br>1 4<br>Z 0 0 0    | XOR (HL)<br>1 8<br>Z 0 0 0    | XOR A<br>1 4<br>1000       |

| Вх        | OR B<br>1 4<br>Z 0 0 0     | OR C<br>1 4<br>Z 0 0 0     | OR D<br>1 4<br>Z 0 0 0     | OR E<br>1 4<br>Z 0 0 0     | OR H<br>1 4<br>Z 0 0 0      | OR L<br>1 4<br>Z 0 0 0      | OR (HL)<br>1 8<br>Z 0 0 0     | OR A<br>1 4<br>Z 0 0 0     | CP B<br>1 4<br>Z1 H C             | CP C<br>1 4<br>Z 1 H C       | CP D<br>1 4<br>Z 1 H C     | CP E<br>1 4<br>Z1 H C      | CP H<br>1 4<br>Z 1 H C     | CPL<br>14<br>Z1HC          | CP (HL)<br>1 8<br>Z 1 H C     | CPA<br>14<br>1100          |

| Сх        | RET NZ<br>1 20/8           | POP BC<br>1 12             | JP NZ, a16<br>3 16/12      | JP a16<br>3 16             | CALL NZ, a16<br>3 24/12     | PUSH BC<br>1 16             | ADD A, d8<br>2 8<br>Z 0 H C   | RST 00H<br>1 16            | RET Z<br>1 20/8                   | RET<br>1 16                  | JP Z, a16<br>3 16/12       | PREFIX<br>1 4              | CALL Z, a16<br>3 24/12     | CALL a16<br>3 24           | ADC A, d8<br>2 8<br>Z 0 H C   | RST 08H<br>1 16            |

| Dx        | RET NC<br>1 20/8           | POP DE<br>1 12             | JP NC, a16<br>3 16/12      | -                          | CALL NC, a16<br>3 24/12     | PUSH DE<br>1 16             | SUB d8<br>2 8<br>Z 1 H C      | RST 10H<br>1 16            | RET C<br>1 20/8                   | RETI<br>1 16                 | JP C, a16<br>3 16/12       |                            | CALL C, a16<br>3 24/12     | -                          | SBC A, d8<br>2 8<br>Z 1 H C   | RST 18H<br>1 16            |

| Ex        | LDH (a8), A<br>2 12        | POP HL<br>1 12             | LD (C), A<br>1 8           | -                          | -                           | PUSH HL<br>1 16             | AND d8<br>2 8<br>Z 0 1 0      | RST 20H<br>1 16            | ADD SP, r8<br>2 16<br>0 0 H C     | JP HL<br>1 4                 | LD (a16), A<br>3 16        | -                          | -                          | -                          | XOR d8<br>2 8<br>Z 0 0 0      | RST 28H<br>1 16            |

| Fx        | LDH A, (a8)<br>2 12        | POP AF<br>1 12<br>Z N H C  | LD A, (C)<br>1 8           | DI<br>1 4                  | -                           | PUSH AF                     | OR d8<br>2 8<br>Z 0 0 0       | RST 30H<br>1 16            | LD HL, SP + r8<br>2 12<br>0 0 H C | LD SP, HL<br>1 8             | LD A, (a16)<br>3 16        | El<br>1 4                  | -                          | -                          | CP d8<br>2 8<br>Z 1 H C       | RST 38H<br>1 16            |

#### opcodes (https://gbdev.io/gb-opcodes/optables/)

|    | ×0       | x1       | x2       | x3       | x4       | x5       | x6          | x7       | x8       | x9       | xA       | хB       | xC       | xD       | xE          | xF       |

|----|----------|----------|----------|----------|----------|----------|-------------|----------|----------|----------|----------|----------|----------|----------|-------------|----------|

| 0x | RLC B    | RLC C    | RLC D    | RLC E    | RLC H    | RLC L    | RLC (HL)    | RLC A    | RRC B    | RRC C    | RRC D    | RRC E    | RRC H    | RRC L    | RRC (HL)    | RRC A    |

|    | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      |

|    | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C     | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | 2 0 0 C     | Z 0 0 C  |

| 1x | RL B     | RL C     | RL D     | RL E     | RL H     | RLL      | RL (HL)     | RLA      | RR B     | RR C     | RR D     | RR E     | RR H     | RR L     | RR (HL)     | RR A     |

|    | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 28       | 2 16        | 28       | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      |

|    | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z00C     | Z 0 0 C     | Z00C     | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | 2 0 0 C     | Z 0 0 C  |

| 2x | SLA B    | SLA C    | SLA D    | SLA E    | SLA H    | SLA L    | SLA (HL)    | SLA A    | SRA B    | SRA C    | SRA D    | SRA E    | SRA H    | SRA L    | SRA (HL)    | SRAA     |

|    | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 28       |

|    | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C     | Z 0 0 C  | 2 0 0 C  | 2 0 0 C  | Z 0 0 C  | Z 0 0 C  | 2 0 0 C  | Z 0 0 C  | 2 0 0 C     | 200C     |

| 3x | SWAP B   | SWAP C   | SWAP D   | SWAP E   | SWAP H   | SWAP L   | SWAP (HL)   | SWAP A   | SRL B    | SRL C    | SRL D    | SRL E    | SRL H    | SRL L    | SRL (HL)    | SRLA     |

|    | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 28       |

|    | Z 0 0 0  | Z 0 0 0  | Z 0 0 0  | Z 0 0 0  | Z 0 0 0  | Z 0 0 0  | Z 0 0 0     | Z 0 0 0  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | Z 0 0 C  | 2 0 0 C     | Z00C     |

| 4x | BIT 0, B | BIT 0, C | BIT 0, D | BIT 0, E | BIT 0, H | BIT 0, L | BIT 0, (HL) | BIT 0, A | BIT 1, B | BIT 1, C | BIT 1, D | BIT 1, E | BIT 1, H | BIT 1, L | BIT 1, (HL) | BIT 1, A |

|    | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 12        | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 12        | 2 8      |

|    | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -     | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -     | Z 0 1 -  |

| 5x | BIT 2, B | BIT 2, C | BIT 2, D | BIT 2, E | BIT 2, H | BIT 2, L | BIT 2, (HL) | BIT 2, A | BIT 3, B | BIT 3, C | BIT 3, D | BIT 3, E | BIT 3, H | BIT 3, L | BIT 3, (HL) | BIT 3, A |

|    | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 12        | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 12        | 2 8      |

|    | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -     | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -     | Z 0 1 -  |

| 6x | BIT 4, B | BIT 4, C | BIT 4, D | BIT 4, E | BIT 4, H | BIT 4, L | BIT 4, (HL) | BIT 4, A | BIT 5, B | BIT 5, C | BIT 5, D | BIT 5, E | BIT 5, H | BIT 5, L | BIT 5, (HL) | BIT 5, A |

|    | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 12        | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 12        | 2 8      |

|    | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -     | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -     | Z 0 1 -  |

| 7x | BIT 6, B | BIT 6, C | BIT 6, D | BIT 6, E | BIT 6, H | BIT 6, L | BIT 6, (HL) | BIT 6, A | BIT 7, B | BIT 7, C | BIT 7, D | BIT 7, E | BIT 7, H | BIT 7, L | BIT 7, (HL) | BIT 7, A |

|    | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 12        | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 12        | 2 8      |

|    | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -     | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -  | Z 0 1 -     | Z 0 1 -  |

| 8x | RES 0, B | RES 0, C | RES 0, D | RES 0, E | RES 0, H | RES 0, L | RES 0, (HL) | RES 0, A | RES 1, B | RES 1, C | RES 1, D | RES 1, E | RES 1, H | RES 1, L | RES 1, (HL) | RES 1, A |

|    | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      |

| 9x | RES 2, B | RES 2, C | RES 2, D | RES 2, E | RES 2, H | RES 2, L | RES 2, (HL) | RES 2, A | RES 3, B | RES 3, C | RES 3, D | RES 3, E | RES 3, H | RES 3, L | RES 3, (HL) | RES 3, A |

|    | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      |

| Ax | RES 4, B | RES 4, C | RES 4, D | RES 4, E | RES 4, H | RES 4, L | RES 4, (HL) | RES 4, A | RES 5, B | RES 5, C | RES 5, D | RES 5, E | RES 5, H | RES 5, L | RES 5, (HL) | RES 5, A |

|    | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      |

| Bx | RES 6, B | RES 6, C | RES 6, D | RES 6, E | RES 6, H | RES 6, L | RES 6, (HL) | RES 6, A | RES 7, B | RES 7, C | RES 7, D | RES 7, E | RES 7, H | RES 7, L | RES 7, (HL) | RES 7, A |

|    | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      |

| Сх | SET 0, B | SET 0, C | SET 0, D | SET 0, E | SET 0, H | SET 0, L | SET 0, (HL) | SET 0, A | SET 1, B | SET 1, C | SET 1, D | SET 1, E | SET 1, H | SET 1, L | SET 1, (HL) | SET 1, A |

|    | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      |

| Dx | SET 2, B | SET 2, C | SET 2, D | SET 2, E | SET 2, H | SET 2, L | SET 2, (HL) | SET 2, A | SET 3, B | SET 3, C | SET 3, D | SET 3, E | SET 3, H | SET 3, L | SET 3, (HL) | SET 3, A |

|    | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      |

| Ex | SET 4, B | SET 4, C | SET 4, D | SET 4, E | SET 4, H | SET 4, L | SET 4, (HL) | SET 4, A | SET 5, B | SET 5, C | SET 5, D | SET 5, E | SET 5, H | SET 5, L | SET 5, (HL) | SET 5, A |

|    | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      |

| Fx | SET 6, B | SET 6, C | SET 6, D | SET 6, E | SET 6, H | SET 6, L | SET 6, (HL) | SET 6, A | SET 7, B | SET 7, C | SET 7, D | SET 7, E | SET 7, H | SET 7, L | SET 7, (HL) | SET 7, A |

|    | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 8      | 2 16        | 2 8      |

#### Prefixed opcode (<u>https://gbdev.io/gb-opcodes/optables/</u>)

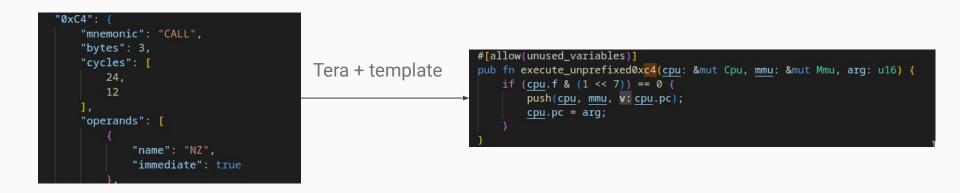

# How to implement the CPU?

- Implement each opcode

- Add a layer of abstraction in the code

- Generate the cpu code

# Debugging

Does the cpu work? 2 steps

- Create some Test / or use tested ROM (blargg test)

- Realise it does not work

Create a debugging tool "gdb" like. Create a disassembler

| <pre>"cycles": [     24,     12 ], "operands": [     {         "name": "NZ",         "immediate": true         Tera + template         OxC3 =&gt; println!("JP {:#04x}", mmu.read16(pos + 1)),         0xC4 =&gt; println!("CALL NZ, {:#04x}", mmu.read16(pos         0xC5 =&gt; println!("PUSH BC"),</pre> |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

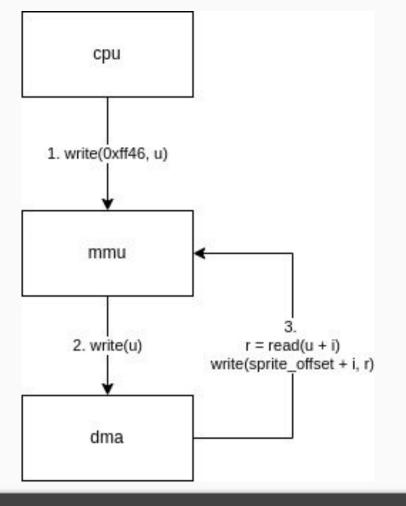

# Direct Memory Access (DMA)

Part of the LCD controller.

Fast copy 160 bytes from anywhere in memory to the sprite memory.

Is triggered by writing to address 0xff46

My intuitive implementation

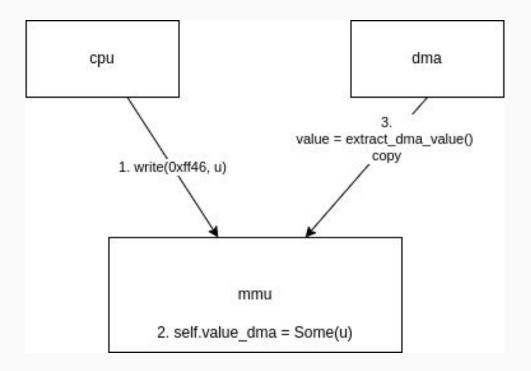

# "At any given time, you can have either one mutable reference or any number of immutable references."

**Rust Rules of References**

https://doc.rust-lang.org/stable/book/ch04-02-references-and-borrowing.html?highlight=mutable#mutable-references

My rust implementation

# Demo Time!

**Red Version**

### Links

My website: <u>bajac.xyz</u>

- The Ultimate GameBoy talk

- Game Boy unofficial wiki

- Game Boy CPU manual

- <u>cs108</u>: The EPFL project in java

## Thanks!

Any Questions?