Connect. Collaborate. Accelerate.

# Business Analysis and Trade-Offs for Chiplet-Based System Design

<u>Marek Hempel</u>, Anu Ramamurthy, Kash Johal, Trent Uehling, James Wong, Irina Sellhusen, Rajesh Pendurkar, Boon Chong Ang, Allan Cantle, Bapi Vinnakota

# Why another Whitepaper on Chiplets?

### **Chiplet Whitepapers**

Most whitepaper only focus

on benefits/challenges

| SIEMENS     → Heterogeneous chipter     WHITE PAPER     Heterogen | Keign and integration: bringing a new twist to SIP design                                                     | <u>å</u>                       |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------|

| chiplet des<br>integration<br>bringing a<br>twist to Sil          |                                                                                                               |                                |

| Design for<br>Processor                                           | Chiplet Technology and<br>the AMD EPYC <sup>™</sup> and Ry<br>Families : Industrial Proc<br>Cite This  PpF    | luct                           |

| 38<br>Cites in<br>Papers                                          | an Beck; Thomas Burd; Kevin Lepak; Ga<br>EPAPER<br>hiplets and Heterogeneous P<br>nanging System Design and A | <b>cādence</b><br>ackaging Are |

### **Cost Calculators**

Full factory cost alone does

not capture all details

|         |                             | Monolithic  |           |

|---------|-----------------------------|-------------|-----------|

|         |                             | Baseline    | Chiplet   |

|         | Die/Chiplet Eff Area (mm2)  | 500         | 175       |

|         | Wafer Size (mm)             | 300         | 300       |

|         | Quantity                    | 1           | 3         |

|         | Wafer Price                 | \$ 10,000   | \$ 10,000 |

| Inputs  | Process Maturity            | Very Mature | Mature    |

|         | Defect Density              | 0.05        | 0.08      |

|         | Wafer sort time (s)         | 20          | 15        |

|         | Wafer Sort Cost             | \$ 1.39     | \$ 1.04   |

|         | Package & Interposer Cost   | \$ 30       | \$ 35     |

|         | Final Package Test Time (s) | 20          | 20        |

|         | Final Package Test Cost     | \$ 1.39     | \$ 1.39   |

|         |                             |             |           |

|         | GDPW                        | 109         | 346       |

| Chiplot | NDPW                        | 85          | 301       |

| Chiplet | Yield (Murphy Model)        | 78.3%       | 87.1%     |

| Outputs | Silicon Cost                | \$ 117.65   | \$ 99.67  |

|         | Packaging and Test          | \$ 32.78    | \$ 37.43  |

|         |                             |             |           |

| System  | Aggregate Silicon Cost      | \$ 117.65   | \$ 99.67  |

|         | Relative Silicon Area       |             | 105%      |

|         | Relative Packaging & Test   |             | 114%      |

| Costs   | Relative Total Cost         |             | 91%       |

|         | Total Unit Cost             | \$ 150.42   | \$ 137.10 |

### **Business Challenges**

• ODSA Business Challenge Talks by 9 companies 2023

| Company          | Presenters        | Date       |

|------------------|-------------------|------------|

| <u>Ventena</u>   | Travis Lanier     | 02/03/2023 |

| <u>Achronix</u>  | Nick Ilyadis      | 02/03/2023 |

| <u>eTopus</u>    | Kash              | 02/10/2023 |

| JCET             | Michael Lui       | 02/10/2023 |

| <u>NXP</u>       | Trent Uehling     | 02/17/2023 |

| ADI              | Marek Hempel      | 02/17/2023 |

| <u>Microchip</u> | Timothy Pezarro   | 03/03/2023 |

| Marvell          | Mark Kuemerle     | 03/10/2023 |

| AMD              | H. Dhavaleswarapu | 03/10/2023 |

# White Paper - Chiplet Business Considerations

### Goal:

- Holistic chiplet business case analysis comparison

- Highlight technical • interdependencies

**Whitepaper Chapters**

Testability

8. Standardization

4. Packaging

7. Marketplace

9. Conclusion

### •Audience:

- Businesspeople

- Product managers

- System architects

### http://tiny.cc/ODSA-Biz-WP-Draft

## Chiplet Architecture

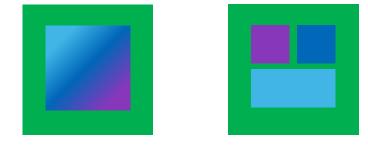

### Homogeneous Design

| ASIC | CPU  |

|------|------|

| 7 nm | 7 nm |

| IO   | CPU  |

| 7 nm | 7 nm |

#### Benefits

- Smaller die 🛛 🗆 better yield

- No reticle limit

build large systems

#### Often used for

- Scalable architectures

- Very large compute systems

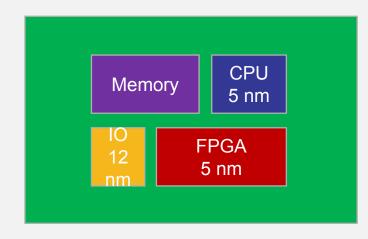

### **Heterogeneous Design**

#### Benefits

- Use mature process node □ lower cost

- Use specialized process

**higher performance**

#### Often used for

- Disaggregation by function

- Splitting analog / digital

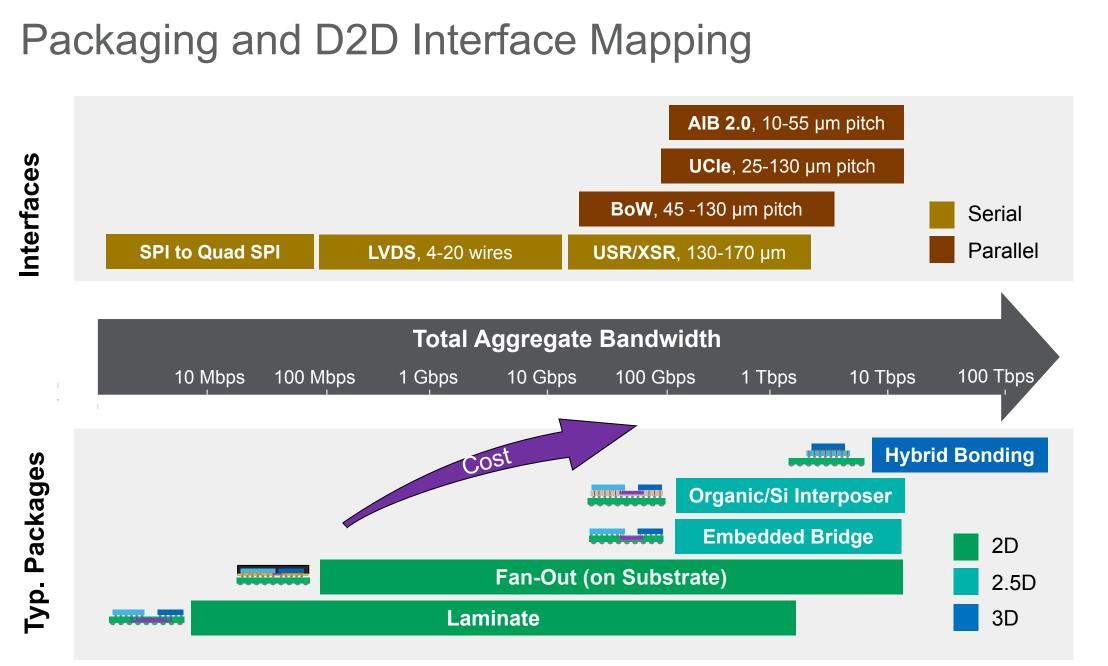

# Die-to-Die Interfaces

| Die-to-Die<br>Interface | Ultra Short Reach<br>SerDes (XSR/USR) | Bunch of Wires<br>(BoW)                         | Advanced Interface<br>Bus (AIB)                      | Universal Chiplet<br>Interface (UCle) |

|-------------------------|---------------------------------------|-------------------------------------------------|------------------------------------------------------|---------------------------------------|

| Adoption                | Industry standard / in<br>production  | ~ 10 companies designing<br>with BoW            | ~ 10x <u>3rd party chiplets,</u><br>Intel's chiplets | ~120 member companies                 |

| Package                 | Laminate                              | Laminate, Fan-Out, Interposer                   | Fan-Out, EMIB, Interposer                            | Laminate, Fan-Out, EMIB<br>Interposer |

| Bump Pitch              | 130-170 μm                            | 45-170 μm                                       | 25 - 55 μm                                           | 10-130 µm                             |

| Lane Rate               | 112 G / 224 G                         | 2 - 32 Gbps                                     |                                                      | 4 - 32 Gbps                           |

| Latency                 | ~10 ns                                | < 2 ns                                          |                                                      | < 2 ns                                |

| Reach                   | < 50 mm                               | < 25 mm                                         | < 25 mm                                              | < 10 mm                               |

| Energy                  | 1-4 pJ/bit                            | 0.3-0.5 pJ/bit                                  | 0.5-0.8 pJ/bit                                       | 0.25-0.5 pJ/bit                       |

| Edge Density            | < 3 Tbps/mm                           | < 4 Tbps/mm                                     | < 1.6 Tbps/mm                                        | < 10 Tbps/mm                          |

| Link Layer              | Not Defined                           | BoW link layer, supporting<br>AXI, CHI          | AXI                                                  | Raw, Streaming, PCIe, CXL             |

| Target<br>Applications  | Optical Networking                    | Disaggregation, e.g Al accelerators, automotive | Aerospace & defense<br>ecosystem                     | Scale & split, system<br>aggregation  |

#### • Performance Metrics

- Bandwidth range (Gbps)

- Beach front (Gbps/mm)

- PHY footprint (mm<sup>2</sup>)

- Energy(pJ/bit)

- Latency (ns)

- Reach (mm)

- Other Metrics

- Package type

- Adoption

- Associated cost

- Maturity

- IP availability

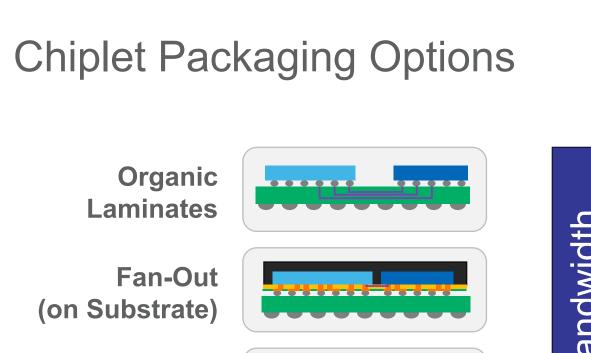

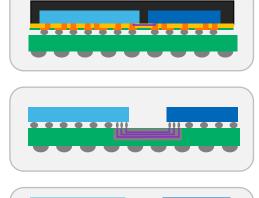

Embedded Si Bridge

Silicon / Organic Interposer

3D Stacking (Hybrid Bonding)

Cost & Bandwidth

Packages need to match their D2D interfaces

- Bump and escape pitch

→ via pad, L/S

- Depths of signal bumps

→ # of layers

- Needed insertion loss

→ dielectric choice

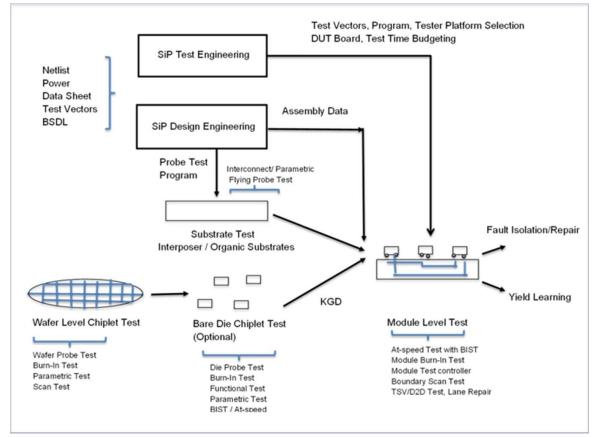

# **Chiplet Testability**

- Why test?

- Lower scrap cost from failing parts

- Design for Test (DFT) techniques

- ATGP, Memory/Logic BIST, Boundary Scan, etc.

- IEEE 1838 3D test architecture

- Test points inserted at various steps, e.g.

- Wafer probe 🗆 KGD

- Substrate test

- Final test / System Level Test

- Test Cost ~ test time \* hourly rate / units

- Rule of thumb: test cost < 20% of die cost

- Don't spend more than scrap cost savings

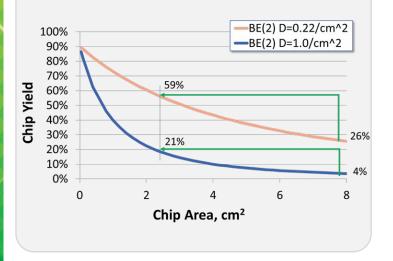

# **Three Financial Benefits of Chiplets**

#### **Yield Advantage**

- Smaller die have higher yield

- Can off-set higher package, test cost for large systems

- See <u>ODSA cost model</u>

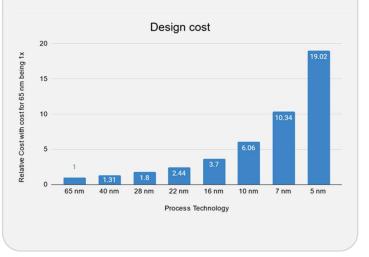

- Newer processes are more expensive to design on

- Shifting some functions to older nodes reduces cost

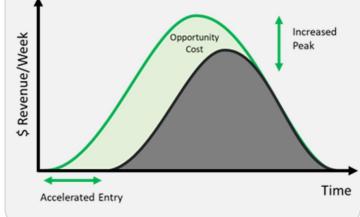

### **Early Entry Advantage**

- Chiplet reuse increases TTM

- This can improve returns by:

- Higher market share

- Longer product life-cycle

- Higher profit margin

# Monolithic vs. Chiplet Cost Trends

| ROI = | (ASP - FFC) x Units |

|-------|---------------------|

|       | NRE                 |

FFC

NRE

|                                            |              | Monolithic<br>Design | Chiplets<br>Design |

|--------------------------------------------|--------------|----------------------|--------------------|

| Non-Recurring<br>Engineering<br>Cost (NRE) | Chip Design  | baseline             | less *             |

|                                            | External IP  | baseline             | similar            |

|                                            | Mask Sets    | baseline             | depends            |

| Full Factory<br>Cost (FFC)                 | Silicon Cost | baseline             | depends            |

|                                            | Probe        | baseline             | more               |

|                                            | Package      | baseline             | more               |

|                                            | Final Test   | baseline             | similar            |

|                                            |              |                      |                    |

# **Open Chiplet Economy And Standardization**

- Open Chiplet Marketplace is not ready yet

- Interoperability testing infrastructure not in place for chiplets

- Bridge chiplets could help with interface link-layer incompatibility

- Supply chain like adv. packaging accessibility needs to improve

- Getting started with chiplet requires investment and know-how

- Standards are key to an Open Chiplet Economy

- Chiplet Design Exchange group spearheaded several contributions

- Standardized chiplet models to ease system-level integration

- Data Exchange format to describe chiplet properties

- Integration workflows for heterogeneous chiplet systems

# Summary

- Previous work hasn't captured a holistic view of chiplet-based design

- Economically viable chiplet-design depends on technology options

- Chiplet product portfolios have lower NRE through reuse, FFC depends

- 3rd party chiplets market still has its challenges but standards help.

**ODSA Business Group**

Compute

Project

Fridays, 9-10 am PT

Zoom Link

**ODSA Mailing List**

**Next Projects & Events Chiplet Business OCP** Chiplet **Challenges Workshop** Marketplace Mar 15<sup>th</sup>,2024

### **DPEN** Compute Project®

# Backup

# Chiplet Business Issues by Count

Business

- 6x Cost benefit vs monolithic, cost overhead

- 3x Product schedule uncertainty, risk

- 2x Up-Front Cost, capability of self-development

- 2x Final Product Responsibility

- 2x Confidential Disclosure

### Marketplace

- 3x Third Party Chiplet Availability

- 2x No open marketplace yet

### Technical

町

- 4x D2D Interface Choice

- 3x Best packaging option std., adv.

- · Ox Ctandardization / ink lawar nowar concetration at a