Open Rack V3 Modbus Communication Specification

Rev: 0.70

09/02/2021

Authors:

Hamid Keyhani David Sun License (OCP CLA Option)

Contributions to this Specification are made under the terms and conditions set forth in Open Compute Project Contribution License Agreement ("OCP CLA") ("Contribution License") by:

#### [Contributor Name(s) or Company name(s)]

You can review the signed copies of the applicable Contributor License(s) for this Specification on the OCP website at http://www.opencompute.org/products/specsanddesign

Usage of this Specification is governed by the terms and conditions set forth in [select one: Open Web Foundation Final Specification Agreement ("OWFa 1.0"), Open Compute Project Hardware License – Permissive ("OCPHL Permissive"), Open Compute Project Hardware License – Copyleft ("OCPHL Reciprocal")] ("Specification License").

You can review the applicable Specification License(s) executed by the above referenced contributors to this Specification on the OCP website at http://www.opencompute.org/participate/legal-documents/

**Note**: The following clarifications, which distinguish technology licensed in the Contribution License and/or Specification License from those technologies merely referenced (but not licensed), were accepted by the Incubation Committee of the OCP:

[insert "None" or a description of the applicable clarifications].

NOTWITHSTANDING THE FOREGOING LICENSES, THIS SPECIFICATION IS PROVIDED BY OCP "AS IS" AND OCP EXPRESSLY DISCLAIMS ANY WARRANTIES (EXPRESS, IMPLIED, OR OTHERWISE), INCLUDING IMPLIED WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, FITNESS FOR A PARTICULAR PURPOSE, OR TITLE, RELATED TO THE SPECIFICATION. NOTICE IS HEREBY GIVEN, THAT OTHER RIGHTS NOT GRANTED AS SET FORTH ABOVE, INCLUDING WITHOUT LIMITATION, RIGHTS OF THIRD PARTIES WHO DID NOT EXECUTE THE ABOVE LICENSES, MAY BE IMPLICATED BY THE IMPLEMENTATION OF OR COMPLIANCE WITH THIS SPECIFICATION. OCP IS NOT RESPONSIBLE FOR IDENTIFYING RIGHTS FOR WHICH A LICENSE MAY BE REQUIRED IN ORDER TO IMPLEMENT THIS SPECIFICATION. THE ENTIRE RISK AS TO IMPLEMENTING OR OTHERWISE USING THE SPECIFICATION IS ASSUMED BY YOU. IN NO EVENT WILL OCP BE LIABLE TO YOU FOR ANY MONETARY DAMAGES WITH RESPECT TO ANY CLAIMS RELATED TO, OR ARISING OUT OF YOUR USE OF THIS SPECIFICATION, INCLUDING BUT NOT LIMITED TO ANY LIABILITY FOR LOST PROFITS OR ANY CONSEQUENTIAL, INCIDENTAL, INDIRECT, SPECIAL OR PUNITIVE DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND EVEN IF OCP HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Open Compute Project • Open Rack V3 Modbus Communication Spec

# **Table of Contents**

| Table of Contents                      | 3  |

|----------------------------------------|----|

| Revision history                       | 4  |

| 1.0 Introduction                       | 5  |

| 2.0 Data Link Layer                    | 5  |

| 2.1 Standard and protocol              | 5  |

| 2.2 MODBUS Transaction state diagram   | 5  |

| 3.0 Hardware Interface                 | 6  |

| 3.1 Addressing                         | 6  |

| 3.2 Message Frame                      | 7  |

| 3.3 MODBUS Functions                   | 8  |

| 3.4 Read Holding Register              | 9  |

| 3.5 Register Mapping                   | 10 |

| 3.6 Two Wire MODBUS implementation     | 10 |

| 4.0 PSU V3 communication block diagram | 11 |

| 5.0 Special Notes                      | 11 |

| 5.1 Variable Modbus Baud Rate          | 11 |

| 5.2 Unix Timestamp                     | 12 |

| 5.3 2's compliment encoding            | 12 |

| Appendix A: PSU Modbus register map    | 13 |

| Appendix B: BBU Modbus register map    | 13 |

# **Revision history**

| Date       | Revisio | History                                                | Author      |

|------------|---------|--------------------------------------------------------|-------------|

|            | n       |                                                        |             |

| 09/26/2020 | 0.1     | First draft for PSU V3                                 | Delta       |

|            |         | Basic to V2/G2 Spec Version 1.9 (6/26/2020)            |             |

| 11/09/2020 | 0.2     | Updated addressing and data rate                       | Hamid and   |

|            |         |                                                        | David S.    |

| 23/02/2021 | 0.3     | 3.1 Addressing: correction of Addressing               | Delta       |

|            |         | 6.0 black box: added PF & iTHD basic to G2             |             |

|            |         | 5.10 Timestamp added basic to G2                       |             |

|            |         | 5.10 Fan RPM Override: added reset condition of 0x122  |             |

|            |         | in Section 5.12 PSU V3 Modbus Register map new MFR     |             |

|            |         | Register 0xDA added                                    |             |

| 15/03/2021 | 0.4     | # Section 5.12 changed Register format of PSU_Output   | Delta/Hamid |

|            |         | Voltage from N=11 to 10                                | & David S.  |

|            |         | # Section 3.3 added Big-Endian Byte order              |             |

| 6/17/2021  | 0.5     | Changed PSU address to 00 (b7 b6) to be different from | Hamid       |

|            |         | V2.                                                    |             |

|            |         | Added address 11 for special devices                   |             |

| 7/30/2021  | 0.6     | Moved register maps to appendix                        | Hamid       |

| 9/2/2021   | 0.7     | Change PSU address to 11 and special device address to | Hamid       |

|            |         | 00.                                                    |             |

### 1.0 Introduction

This manual describes the communication protocol to be used with Rack Monitor and Power Shelf V3.

## 2.0 Data Link Layer

#### 2.1 Standard and protocol

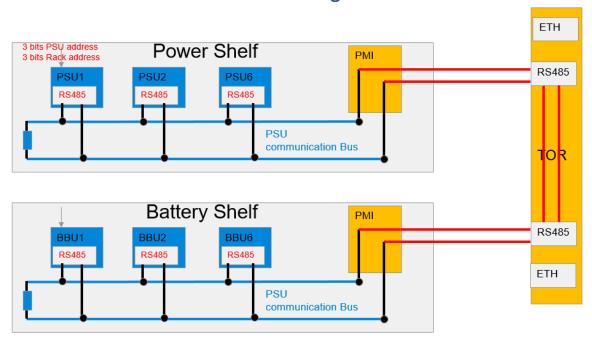

Open Rack V3 utilizes the RS485 standard for communication between the power supplies residing in a 'Power Shelf' and a 'Rack Monitor'.

MODBUS is the serial communication protocol to be used with this standard.

All aspects of the MODBUS protocol are to follow the MODBUS Organization specifications and implementation guides, namely the reference documents below:

- [1]: MODBUS Serial Line Protocol and Implementation Guide V1.02

- [2]: MODBUS Protocol Specification (MODBUS APPLICATION PROTOCOL SPECIFICATIONV1.1b)

There will be exceptions granted if hardware does not allow for use of required transmission. However, the transmission across products and vendors must remain as stated in this document.

The protocol is a half-duplex Master/Slave. The Rack Monitor is always the master and has complete, unidirectional control over the slaves. Power supplies and other devices are considered slaves in this arrangement.

Unicast protocol mode is to be implemented. This means that the master always addresses one node only at a given time. Broadcast mode is not allowed in this communication scheme. There is only one master in the system. Slaves do not initiate communication to the master or other slaves.

#### 2.2 MODBUS Transaction state diagram

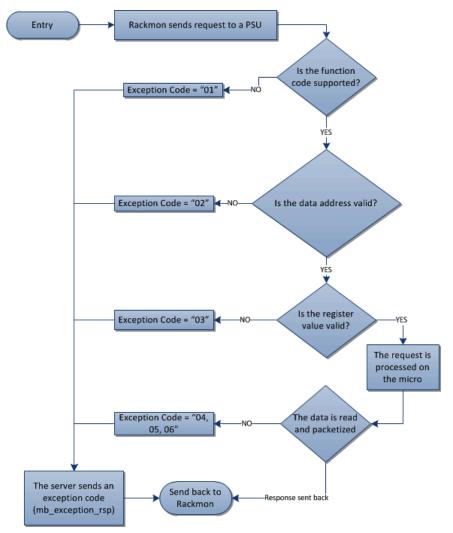

Figure 1 outlines the transaction state diagram between the Master (Rackmon) and slaves along with exception to be thrown where appropriate.

Figure 1 Transaction State diagram

#### 3.0 Hardware Interface

Up to three racks can be connected to one system monitor. In each rack, there can be at most one power shelves; each power shelf can house three Power Supplies and three Battery Backup Units. All slaves have their own unique address.

To accommodate such addressing, without allowing broadcast mode, the following structure is to be used to give each power supply a unique address.

#### 3.1 Addressing

Each power supply will have an address in the following format:

### Open Compute Project • Open Rack V3 Modbus Communication Spec

**Table 1** Power Supply address format

| Fixed | Fixed | Rack_ADD2 | Rack_ADD1 | Rack_ADD0 | PSU_ADD<br>2 | PSU_ADD<br>1 | PSU_ADD<br>0 |

|-------|-------|-----------|-----------|-----------|--------------|--------------|--------------|

| b7    | b6    | b5        | b4        | b3        | b2           | b1           | b0           |

| 1     | 1     | X2        | X1        | X0        | Z2           | Z1           | Z0           |

PSU\_ADDx: hardwired at the shelf

Rack\_ADD1, Rack\_ADD0: Hardwired at TOR

Rack\_ADD2: Hardwired at PMI (pin 6) for daisy-chain purposes.

### Each BBU will have an address in the following format:

Table 2 BBU address format

| Fixed | Fixed | Rack_ADD2 | Rack_ADD1 | Rack_ADD0 | BBU_ADD<br>2 | BBU_ADD<br>1 | BBU_ADD<br>0 |

|-------|-------|-----------|-----------|-----------|--------------|--------------|--------------|

| b7    | b6    | b5        | b4        | b3        | b2           | b1           | b0           |

| 0     | 1     | X2        | X1        | X0        | Z2           | Z1           | Z0           |

BBU\_ADDx: hardwired at the shelf

Rack\_ADD1, Rack\_ADD0: Hardwired at TOR

Rack\_ADD2: Hardwired at PMI (pin 6) for daisy-chain purposes.

#### Special devices (like RPU, etc)

Table 3 special device address format

| Fixed | Fixed | Rack_ADD2 | Rack_ADD1 | Rack_ADD0 | BBU_ADD<br>2 | BBU_ADD<br>1 | BBU_ADD<br>0 |

|-------|-------|-----------|-----------|-----------|--------------|--------------|--------------|

| b7    | b6    | b5        | b4        | b3        | b2           | b1           | b0           |

| 0     | 0     | X2        | X1        | X0        | Z2           | Z1           | Z0           |

<sup>\*\*</sup> don't use address 0x00, which is reserved for broadcasting.

### 3.2 Message Frame

The message frame follows a standard MODBUS RTU frame format:

Table 6 Message Frame

| Start      | Address | Function | Data       | CRC     | End        |

|------------|---------|----------|------------|---------|------------|

| ≥3.5 Bytes | 1 Byte  | 1 Byte   | 0-32 Bytes | 2 Bytes | ≥3.5 Bytes |

Table 7 Message Frame

| Parameter          | Description                                                      |

|--------------------|------------------------------------------------------------------|

| Bit Rate (Default) | Supports 19.2k ~ 115.2k b/s                                      |

|                    | 1 Start Bit                                                      |

|                    | 8 Data Bits (LSB sent first)                                     |

|                    | 1 Parity Bit (Even)                                              |

| Bits per Byte      | 1 Stop Bit                                                       |

| Address            | Slave Address                                                    |

| Function           | Refer to Table 8                                                 |

|                    | Read request: 4 bytes                                            |

|                    | Write request 1-32 bytes                                         |

| Data               | Read/Write request is determined by the number of Bytes received |

| CRC                | Refer to reference 1, section 2.5.1.2                            |

| Start/End          | At least 3.5 Bytes                                               |

| Reply Timeout      | 1sec                                                             |

### **3.3 MODBUS Functions**

A subset of the standard MODBUS functions will be used. All functions that are not defined will return an exception code.

Table 8 Function Table

| Function       |      |                           |      |                                         |

|----------------|------|---------------------------|------|-----------------------------------------|

| Name           | Туре | Comments                  | Code | Notes                                   |

| Read Holding   |      |                           |      |                                         |

| register       | R    | Read register             | 0x03 | Required                                |

| Read input     |      |                           |      |                                         |

| register       | R    | Read register             | 0x04 | Required                                |

| Write Single   |      |                           |      | Required but will fail on all read only |

| Register       | W    | Write register            | 0x06 | registers                               |

| Write multiple |      |                           |      | Optional but will fail if not properly  |

| register       | W    | Write multiple registers  | 0x10 | implemented                             |

| Read File      |      | May be used by vendor for |      | Optional but will fail if not properly  |

| Record         | R    | Firmware update, etc.     | 0x14 | implemented                             |

| Write File<br>Record         | W   | May be used by vendor for Firmware update, etc.  | 0x15                          | Optional but will fail if not properly implemented |

|------------------------------|-----|--------------------------------------------------|-------------------------------|----------------------------------------------------|

| Bit masked<br>Write register | W   | Write only unmasked bits in a register           | 0x16                          | Optional but will fail if not properly implemented |

| R/W multiple                 | R/W | Read a register and write many registers at once | 0x17                          | Optional but will fail if not properly implemented |

| Encapsulated<br>Transport    | NA  | May be used by vendor for Firmware update, etc.  | 0x2B                          | Optional but will fail if not properly implemented |

| Vendor defined functions     | N/A | May be used by vendor for Firmware update, etc.  | 0x41 to<br>0x48,<br>0x64-0x6E | Optional but will fail if not properly implemented |

All PSU Data are define as in Modbus Spec *Modbus\_Application\_Protocol\_V1\_1b3* with Big-Endian Byte order

## 3.4 Read Holding Register

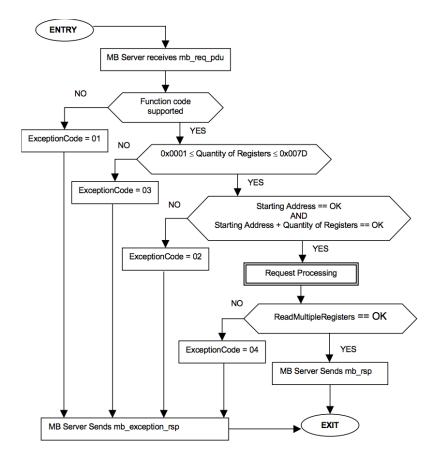

The (0x03) function code is to be implemented per state diagram below; extracted from [2]MODBUS protocol Specification V1.1b, Section 6.3

Figure 4 Read holding Register state diagram

#### 3.5 Register Mapping

The two types of registers holding and input will be mapped to the same memory space. A read of a holding register at address X will return the same result as a read of an input register at address X. Writes will only be allowed to writable registers. All attempts to write to read-only registers will result in a normal exception (Section 7, [2] MODBUS Protocol Specification V1.1b)

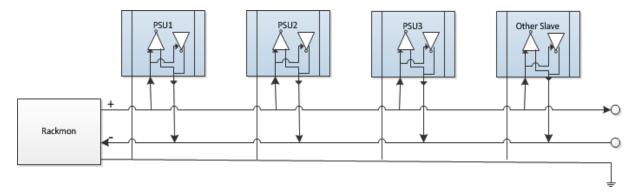

#### 3.6 Two Wire MODBUS implementation

This serial communication is implemented on a two-wire interface in accordance with EIA/TIA-485. In this two-wire implementation only one Master-Slave (driver) pair can transmit.

In addition to the two transmit wires. A reference ground will be available on pin 1.

System is used locally within a rack, the wire length is under 2.5meters.

$120\Omega$  Termination resistor shall be added on the shelf and its position is farthest from shelf output RJ45 connector.

The Master and Slaves will utilize RJ45 connectors and twisted Cat-5 cable to accommodate the two-wire system. Other extra pins on the cable and connector will be used for addressing purposes.

Figure 5 Two wire implementation (TBD)

The pin out is as follows, using the TIA-568-B wire coloring:

**Table 9 RJ45 Connector pin-out**

| Pin | Wire color   | Function |

|-----|--------------|----------|

| 1   | White/Orange | GND      |

| 2   | Orange       | PLS      |

| 3 | White/Green | ВКР         |

|---|-------------|-------------|

| 4 | Blue        | RS485A      |

| 5 | White/Blue  | RS485B      |

| 6 | Green       | RS485_Addr2 |

| 7 | White/Brown | RS485_Addr1 |

| 8 | Brown       | RS485_Addr0 |

# 4.0 PSU V3 communication block diagram

Figure: 1

## In V3 design, the following key features are added.

- 1. PSU power monitoring registers. See details in PSU/BBU register maps.

- 2. PSU/BBU black box through Modbus. See details PSU/BBU register maps.

- 3. System controlling knobs: Variable Modbus baud rate

## **5.0 Special Notes**

#### **5.1 Variable Modbus Baud Rate**

The PSU/BBU shall respond accordingly within 1 second after Rach Monitor successfully writing to corresponding registers.

#### Starting procedure:

Rack Monitor writes the baud rate speed configuration number (1:19200; 2:38400; 3:57600; 4:115200) to the related register.

If Rack Monitor doesn't receive a positive response or no communication response after 10 minutes from any PSUs or BBUs, next communication will be using the default baud rate.

#### Finishing procedure:

PSU or BBU will reply to acknowledge the change and next communication will use the new baud rate speed.

PSU or BBU will go back to the default baud rate when there is no valid MODBUS communication after 10 minutes timeout.

#### Note:

- 1. The baud rate shall be changed in normal operation mode only and bootloader will follow the same baud rate speed which is set in normal operation mode.

- 2. No valid MODBUS communication timeout is 10 minutes.

#### **5.2 Unix Timestamp**

#### Use case:

Rack Monitor to provide PSU/BBU Blackbox wall clock time stamp.

#### Procedure:

Rack Monitor punches wall clock Unix time to PSU/BBU every two minutes.

### 5.3 2's compliment encoding

$Y = X/2^N$

277volts = 17728/2<sup>6</sup>

Where Y is the real world measurement expressed in an integer. 277Volts displayed to the user by the application run on the Master device.

X is the decimal representation of the binary number held in the register. 17728 in binary is 01000101000000. The leftmost bit is the most significant and is 0 therefor it is a positive number.

N is the sign magnitude. This is specified in the table above (N=6 for Input Voltage AC).

**Appendix A: PSU Modbus register map** See attached.

Appendix B: BBU Modbus register map See attached.