Sergio Velásquez

### **MICROPROCESADORES**

Intensivo 2014

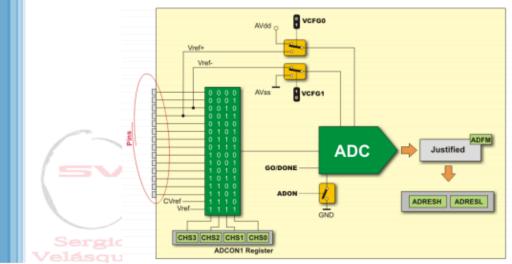

- La Analog-to-Digital Converter (ADC) permite la conversión de una sola terminal y diferenciales señales de entrada analógica a una representación binaria de 12 bits de esa señal.

- Este dispositivo utiliza las entradas analógicas, que son multiplexados en una sola muestra y mantenimiento de circuitos. La salida de la muestra y retención está conectado a la entrada del convertidor.

- El convertidor genera un resultado binario de 12 bits a través de la aproximación sucesiva y almacena el resultado de la conversión en los registros de resultados de ADC (ADRESH: ADRESL registro par). El convertidor A / D permite la conversión de una señal de entrada analógica a una representación binaria de 10 bits de esa señal; y

- Mediante la selección de referencias de voltaje Vref-y Vref +, la resolución o la calidad de la conversión mínima se pueden ajustar para diferentes necesidades.

Sergio Velásquez

- La Analog-to-Digital Converter (ADC) permite la conversión de una sola terminal y diferenciales señales de entrada analógica a una representación binaria de 12 bits de esa señal.

- Este dispositivo utiliza las entradas analógicas, que son multiplexados en una sola muestra y mantenimiento de circuitos. La salida de la muestra y retención está

conectado a la entrada del convertidor.

- El convertidor genera un resultado binario de 12 bits a través de la aproximación sucesiva y almacena el resultado de la conversión en los registros de resultados de ADC (ADRESH: ADRESL registro par). El convertidor A / D permite la conversión de una señal de entrada analógica a una representación binaria de 10 bits de esa señal; y

- Mediante la selección de referencias de voltaje Vref-y

Vref +, la resolución o la calidad de la conversión mínima se pueden ajustar para diferentes necesidades.

- Modos de ADC y Registros

- A pesar de que el uso de convertidor A / D parece ser muy complicado, que es básicamente muy simple, más simple que el uso de temporizadores y módulo de comunicación serie, de todos modos.

- Modos de ADC y Registros

- A pesar de que el uso de convertidor A / D parece ser muy complicado, que es básicamente muy simple, más simple que el uso de temporizadores y módulo de comunicación serie, de todos modos.

- El módulo está bajo el control de los bits de cuatro registros:

- ADRESH Contiene byte alto del resultado de la conversión;

- ADRESL Contiene byte bajo del resultado de la conversión;

- ADCON0 Registro de control 0; y

- Registro de control ADCON1 1

- El módulo está bajo el control de los bits de cuatro registros:

- ADRESH Contiene byte alto del resultado de la conversión;

- ADRESL Contiene byte bajo del resultado de la conversión;

- ADCON0 Registro de control 0; y

- Registro de control ADCON1 1

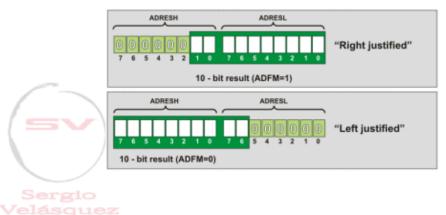

- ADRESH y ADRESL

- Cuando la conversión de un valor analógico en digital, el resultado de la conversión A / D de 10 bits se almacena en estos dos registros. Con el fin de hacer frente a este valor más fácil, puede aparecer en dos formatos justificado a la izquierda y la derecha justificado. El bit ADFM del registro ADCON1 determina el formato del resultado de la conversión (véase la figura 7-2). En el caso de que un convertidor A / D no se utiliza, estos registros pueden ser utilizados como registros de uso general.

- ADRESH y ADRESL

- Cuando la conversión de un valor analógico en digital, el resultado de la conversión A / D de 10 bits se almacena en estos dos registros. Con el fin de hacer frente a este valor más fácil, puede aparecer en dos formatos justificado a la izquierda y la derecha justificado. El bit ADFM del registro ADCON1 determina el formato del resultado de la conversión (véase la figura 7-2). En el

caso de que un convertidor A / D no se utiliza, estos registros pueden ser utilizados como registros de uso general.

• Cuando la conversión de un valor analógico en digital, el resultado de la conversión A / D de 10 bits se almacena en estos dos registros. Con el fin de hacer frente a este valor más fácil, puede aparecer en dos formatos justificado a la izquierda y la derecha justificado. El bit ADFM del registro ADCON1 determina el formato del resultado de la conversión (véase la figura 7-2). En el caso de que un convertidor A / D no se utiliza, estos registros pueden ser utilizados como registros de uso general.

### **ADRESH y ADRESL**

■ Cuando la conversión de un valor analógico en digital, el resultado de la conversión A / D de 10 bits se almacena en estos dos registros. Con el fin de hacer frente a este valor más fácil, puede aparecer en dos formatos justificado a la izquierda y la derecha justificado. El bit ADFM del registro ADCON1 determina el formato del resultado de la conversión (véase la figura 7-2). En el caso de que un convertidor A / D no se utiliza, estos registros pueden ser utilizados como registros de uso

general.

### Requisitos de Adquisición A / D

Para el ADC para satisfacer su precisión especificada, es necesario proporcionar un cierto retardo de tiempo entre la selección de entrada analógica específica y la medición en sí. Este tiempo se denomina "tiempo de adquisición" y depende principalmente de la impedancia de la fuente. Hay una ecuación utilizada para calcular con precisión este tiempo, que en el peor de los casos asciende a aproximadamente 20uS.Brevemente, después de seleccionar (o cambiar) la entrada analógica y antes de iniciar la conversión es necesario para proporcionar al menos retardo de tiempo 20uS para permitir que la precisión de la conversión máxima de ACD.

# Requisitos de Adquisición A / D

Para el ADC para satisfacer su precisión especificada, es necesario proporcionar un cierto retardo de tiempo entre la selección de entrada analógica específica y la medición en sí. Este tiempo se denomina "tiempo de adquisición" y depende principalmente de la impedancia de la fuente. Hay una ecuación utilizada para calcular con precisión este tiempo, que en el peor de los casos asciende a aproximadamente 20uS.Brevemente, después de seleccionar (o cambiar) la entrada analógica y antes de iniciar la conversión es necesario para proporcionar al menos retardo de tiempo 20uS para permitir que la precisión de la conversión máxima de ACD.

#### Período Reloj ADC

Tiempo necesario para completar una conversión de un bit se define como TAD. El TAD requerida debe ser de al menos 1,6 uS. Una conversión completa de 10 bits A / D es un poco más de lo esperado y asciende a 11 períodos de TAD. Sin embargo, ya que tanto la frecuencia de reloj de conversión y la fuente se determinan por el software, una de las combinaciones disponibles de bits ADCS1 y ADCS0 debe ser seleccionado antes de la medición de tensión en algunos comienza entrada analógica. Estos bits se almacenan en el registro ADCONO.

|   | ADC             | ADCS1 | ADCS0 | (FOSC) |        |        |        |

|---|-----------------|-------|-------|--------|--------|--------|--------|

|   | CLOCK<br>SOURCE |       |       | 20 Mhz | 8 Mhz  | 4 Mhz  | 1 Mhz  |

|   | Fosc/2          | 0     | 0     | 100 nS | 250 nS | 500 nS | 2 uS   |

| į | Fosc/8          | 0     | 1     | 400 nS | 1 uS   | 2 uS   | 8 uS   |

|   | Fosc/32         | 1     | 0     | 1.6 uS | 4 uS   | 8 uS   | 32 uS  |

|   | Frc             | 1     | 1     | 2-6 uS | 2-6 uS | 2-6 uS | 2-6 uS |

Cualquier cambio en la frecuencia de reloj del sistema afectará a la frecuencia de reloj ADC, lo que puede afectar negativamente el resultado ADC. Características de frecuencia de dispositivos se muestran en la tabla anterior. Los valores de las celdas sombreadas se encuentran fuera del rango recomendado

### Período Reloj ADC

■ Tiempo necesario para completar una conversión de un bit se define como TAD. El TAD requerida debe ser de al menos 1,6 uS. Una conversión completa de 10 bits A / D es un poco más de lo esperado y asciende a 11 períodos de TAD. Sin embargo, ya que tanto la frecuencia de reloj de conversión y la fuente se determinan por el software, una de las combinaciones disponibles de bits ADCS1 y ADCS0 debe ser seleccionado antes de la medición de tensión en algunos comienza entrada analógica. Estos

bits se almacenan en el registro ADCON0.

#### **ADC CLOCK SOURCE**

(FOSC)

#### 20 Mhz 8 Mhz 4 Mhz 1 Mhz

Fosc / 2 0 0 100 nS 250 nS 500 nS 2 uS Fosc / 8 0 1 400 nS 1 uS 2 uS 8 uS Fosc/32 1 0 1.6 uS 4 uS 8 uS 32 uS Frc 1 1 2-6 uS 2-6 uS 2-6 uS 2-6 uS

Cualquier cambio en la frecuencia de reloj del sistema afectará a la frecuencia de reloj ADC, lo que puede afectar negativamente el resultado ADC. Características de frecuencia de dispositivos se muestran en la tabla anterior. Los valores de las celdas sombreadas se encuentran fuera del rango recomendado

**ADCS1 ADCS0**

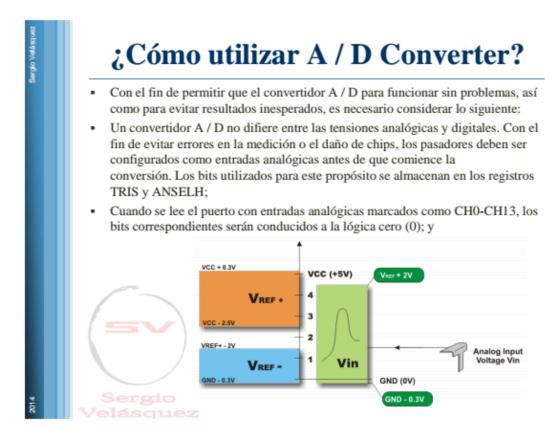

## ¿Cómo utilizar A / D Converter?

- Con el fin de permitir que el convertidor A / D para funcionar sin problemas, así como para evitar resultados inesperados, es necesario considerar lo siguiente:

- Un convertidor A / D no difiere entre las tensiones analógicas y digitales. Con el fin de evitar errores en la medición o el daño de chips, los pasadores deben ser

configurados como entradas analógicas antes de que comience la conversión. Los bits utilizados para este propósito se almacenan en los registros TRIS y ANSELH;

Cuando se lee el puerto con entradas analógicas marcados como CH0-CH13, los bits correspondientes serán conducidos a la lógica cero (0); y