## **Minimal UART CPU System 1.x**

by Carsten Herting (slu4) last update Jul 24th 2022

# Manual Rev. 1.x

Welcome to the Minimal CPU System - let's just call it the 'Minimal'. I've designed this little computer entirely from TTL logic to be as enjoyable and educational as I possibly can. It's made as a learning platform and to facilitate a deep understanding of the basic principles of computers. Despite being deliberately simple, this CPU is powerful enough to "never stop being usable" and more than doubles the processing power of a Commodore C64 or Apple II. It can run some serious software including early video game classics like TETRIS, IEEE 32-bit floating point math, a text editor, a native assembler capable of assembling itself and even a Python-like high-level programming language.

This document provides a comprehensive step-by-step introduction to first-time users of the Minimal and at the same time serves as a reference and programming handbook. See the section 'CPU Architecture' for a brief explanation of how it all works.

Have fun and let me know what you think!

Copyright (c) 2021, 2022 Carsten Herting (slu4)

THIS DOCUMENTATION IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF OR IN CONNECTION WITH THIS DOCUMENTATION OR THE USE OR OTHER DEALINGS IN THIS DOCUMENTATION.

#### **Board Revisions**

There are several revisions of the 'Minimal' publicly available:

### Revision 1.2 (EEPROM PCB Edition)

- o 1.8432MHz clock speed

- o 8KB ROM, 24KB RAM

- o memory-mapped UART I/O

- o not software-compatible to higher revisions

## Revision 1.3 (FLASH PCB Edition)

- o 1.8432MHz clock speed

- o 32KB FLASH SSD, 32KB RAM

- o dedicated UART I/O instructions

- o fully software-compatible to revision 1.5

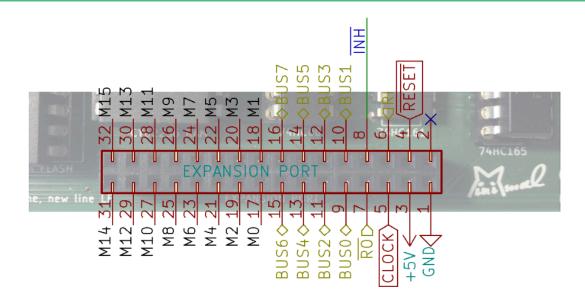

## Revision 1.5 (Expanded PCB Edition)

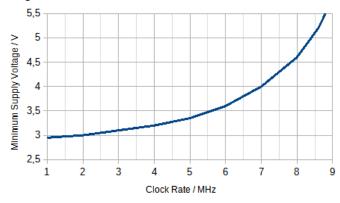

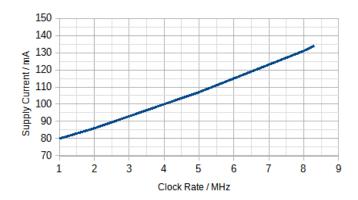

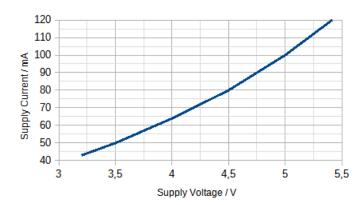

- o selectable clock speed up to 3.6864MHz

- o 512KB FLASH SSD, 32KB RAM

- o dedicated UART I/O instructions

- o expansion port and selectable clock speed

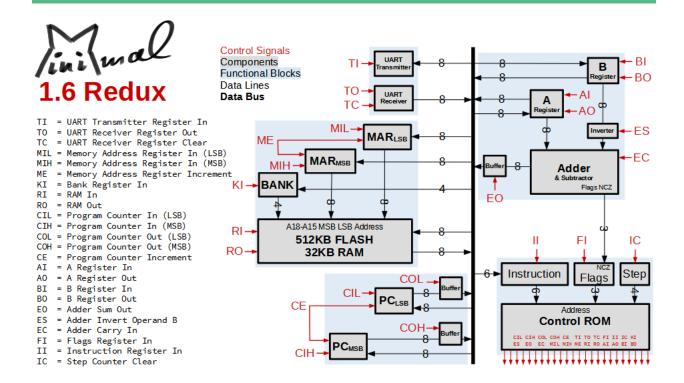

## Redux Breadboard Revision 1.6 (aka Beast Mode Edition)

same as revision 1.5 except for:

- o 8.3MHz maximum clock speed

- o improved microcode efficiency

- o runs all software of revision 1.3 1.5

- o optimized for breadboards and lowest chip count

Earlier breadboard prototypes no longer exist (revisions 0.9 and 1.0). PCB revisions 1.1 and 1.4 represent internal validation steps.

This text applies to board revisions 1.5 and higher, although from 1.3 onwards, all revisions are software-compatible. A cycle-exact emulator of revision 1.5 is available on Windows (see chapter 'Emulator').

## **Building the Hardware**

Step 1. I have documented the development of the 'Minimal CPU System' on my YouTube channel:

www.youtube.com/channel/UCXYQcMpUBT3aaQKfmAVJNow

Humble beginnings:

www.youtube.com/playlist?list=PLY1Qj5cfIcBVRMsr9yxHmvCzMqonI606N

• 'Minimal' is taking shape:

www.youtube.com/playlist?list=PLY1Qj5cfIcBU5SqFe6Uz4Q31\_6VZyZ8h5

• Build information on revision 1.5 (Expanded Edition):

www.youtube.com/watch?v=osVi06VKvA0

Build information on revision 1.6 (Breadboard Redux Edition): https://www.youtube.com/watch?v=Gz1VVOsNn\_8

There is also a discussion board where you can engage with other 'minimalists' to get some help or browse through different builds: <a href="https://minimal-cpu-system.boards.net/">https://minimal-cpu-system.boards.net/</a>

All build information is contained in the Minimal's GitHub repository: <a href="https://github.com/slu4coder/Minimal-UART-CPU-System">https://github.com/slu4coder/Minimal-UART-CPU-System</a>

This is what you'll find:

- KiCAD project files with detailed schematics and PCB layout

- PCB Gerber files and bill of materials (BOM)

- Source code of all programs available for the Minimal These programs can be assembled and uploaded either on real hardware or into the 'Minimal Emulator'.

- Binary images of the FLASH memory (OS, demos and games) and the CPU's control microcode

- Cross-assembler executable (Windows) to write your own programs

- Cross-assembler written in Python www.youtube.com/watch?v=rdKX9hzA21U

- Emulator executable simulating the Minimal cycle-exactly

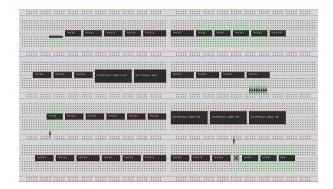

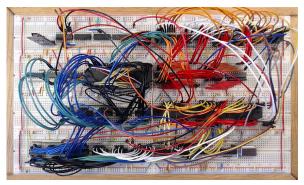

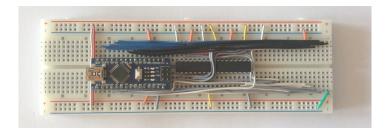

Step 2. Download the GitHub repository. If you want to go for the PCB version, send the Gerber files over to a PCB manufacturer of your liking. Going for the breadboard version you will need 8 good-quality 65-row breadboards as shown below (point-to-point resistance <1 Ohm is recommended), around 240 jumper wires plus some longer connections and lots of smaller bits and pieces of wire.

Step 3. Shop for all the parts needed (see bill of materials). Depending on the region you live in, this may be either very easy or quite complicated. Almost all parts are pretty standard, though.

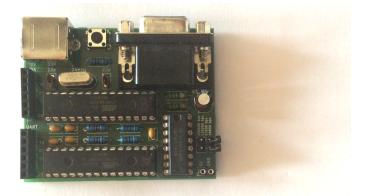

Step 4. Assembly! It usually takes about 2-3 hours of soldering .

Since I have deliberately used old-school through-hole parts and DIL IC packages, soldering can easily be done by hand.

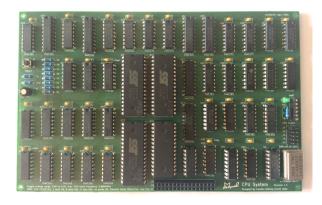

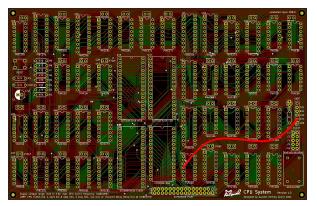

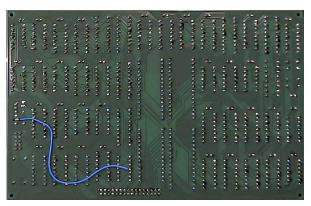

The 74HCxx IC family is susceptible to ESD damage, so it's a good idea to ensure proper grounding of your workspace before you start. The result on PCB should look something like this:

If you go for the breadboard version, plan around 6 hours of build time. Any mistake will be a pain to track down. So carefully double-check every connection.

Step 5. Burn the FLASH images (Control FLASHs and the OS/SSD FLASH). If you do not own a FLASH EEPROM programmer I recommend building my DIY version: <a href="https://www.youtube.com/watch?v=2crXqNlBazq">www.youtube.com/watch?v=2crXqNlBazq</a>

Step 6. Get a 5V output USB-to-serial breakout board. Not all boards share the same pinout. My board here is based upon the IC FT232. From bottom to top the pins are labeled GND, CTS, 5V, TXD, RXD and DTR (not used).

Step 7. Read the section 'Before Power-Up' of this document before connecting the PCB to your PC.

## **Before Power-Up**

Select the Minimal's clock speed divider (applies to revision 1.5 only) by placing a jumper horizontally on exactly one of the rows of the 5x2 pin header on the bottom right of the PCB. If you are using a 3.6864MHz crystal you can use any jumper position. If you are using a 7.3728MHz crystal the smallest divide you can select is 2, since the

maximum CPU clock rate is 3.6864MHz. Let's for now choose a clock speed of 1.8432MHz and call this the default speed.

| 5x2 l | Divi | der | 3.6864MHz Crystal     | 7.3728MHz Crystal     |

|-------|------|-----|-----------------------|-----------------------|

| /1    | 0    | 0   | 3.6864MHz (230400bps) | do not connect        |

| /2    | 0    | 0   | 1.8432MHz (115200bps) | 3.6864MHz (230400bps) |

| /4    | 0    | 0   | 0.9216MHz (57600bps)  | 1.8432MHz (115200bps) |

| /8    | 0    | 0   | 0.4608MHz (28800bps)  | 0.9216MHz (57600bps)  |

| /16   | 0    | 0   | 0.2304MHz (14400bps)  | 0.4608MHz (28800bps)  |

Other oscillator and clock speed combinations are also possible, e. g. a 16MHz oscillator with a 2MHz (/8) system clock selected will run at a serial speed of 125kbps. You can even use a manual clock. I recommend socketing the oscillator for maximum flexibility.

WARNING: "Hot-plugging" the Minimal or ICs of the Minimal can cause unwanted write operations to the FLASH IC, potentially leading to data loss, making a re-programming of the FLASH IC necessary.

Always disconnect your USB-to-serial breakout board from the USB port before plugging it into the Minimal's UART socket. Make sure that the GND and 5V lines connect correctly. Verify that the UART TXD (transmit) line will cross-connect to the breakout board's RXD (receive) line and vice versa. Only then connect the USB plug to power (usually a USB port on your PC).

If you plan to connect to the Minimal UART socket with jumper wires, always make sure to connect GND \*before\* connecting any other lines.

## **Serial Port Configuration**

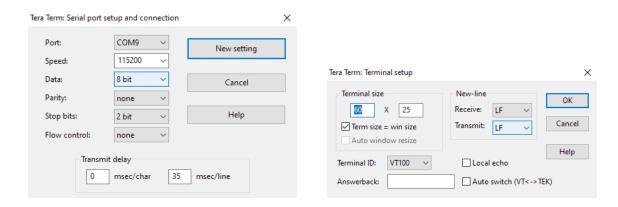

After power-up, the LED should be on. Now is the time to configure the serial port of your PC. This configuration will look a bit different in each terminal emulation but generally we need to set the following:

- o Set the baud rate to 1/16th of the CPU clock speed you have selected. Since we have chosen 1.8432MHz, this is 115200bps.

- o Select 1 start bit, 8 data bits, 2 stop bits, no parity bits, no flow control, local echo off.

- o Set the 'new line character' to be LF (0x0a) like in UNIX.

- o Set a transmit delay of 35ms/line to ensure that Minimal will have enough time to process each input line. The delay varies with clock speed (3.6864MHz: 17ms, 230.4kHz: 95ms) and also with your host system's load. Just experiment a bit.

- o Set the terminal emulation to 60 x 25 characters and chose a

proper font. I like this C64-style TrueType terminal font: https://style64.org/c64-truetype.

In 'TeraTerm' on my Windows machine, this will look like this:

NOTE: With a minor modification the Minimal also supports RTS/CTS flow control. See the appendix for more information.

## **Boot Monitor**

Now press the RESET button in the upper left corner of the PCB. The Minimal should greet you with the following start screen:

```

+-----+

| MINIMAL CPU SYSTEM 1.5.3 by C. Herting |

| 512KB SSD - 32KB RAM - Type m for menu |

+-----+

8000 _

```

You are now inside the boot monitor. Typing 'm <ENTER>' displays the menu options:

```

HEX [r] Set A [run]

[A].B Show [A]..B [q]

:C[ D] Store C[D] at A..

v A B C Fill A..B with C

k A B C Copy A..B to C..

i A DisAsm A.. [q]

s A B F Save A..B as file F

l file Load file

z file Zap file

n 0..f Set SSD bank

t Show SSD content

w Wipe SSD bank

```

Let's go through them by using examples. By typing any 2-byte HEX address followed by <ENTER> you can change the address the monitor is displaying at the start of the input line. The OS only accepts lower-case letters.

By pressing 'r <ENTER>' the monitor will jump to that location and execute whatever program is located there. Let's try that by typing:

f000 <ENTER>

r <ENTER>

You should again see the start screen since 0xf000 is the start of the operating system in RAM. Bring back the menu with m. You can display the memory content by using the '.' symbol:

.f0ff <ENTER>

will display the memory content starting from the current address (which we have set to 0xf000) until 0xf0ff. You can take a look at larger sections, too. After each page, the OS waits for a keystroke before displaying the next page. You can quit by pressing 'q'. Try

0000.ffff <ENTER>

to display the whole memory content starting at address 0x0000. Let's display the memory area at 0x8000 by typing:

8000.801f <ENTER>

This should show something similar (but not identical) to this:

8000 ab 9f e6 6a 28 f7 b6 0a 65 ae 8e f5 73 43 d7 b2 8010 d2 dd ab c6 8f d7 26 f3 8f 0e 08 62 9f 2d c0 ee 8000

since after power-up the RAM is usually filled with random garbage. Let's fill the first 16 bytes with zeros by using the 'fill' command 'v':

v 8000 800f 0 <ENTER> 8000.801f <ENTER>

which will now display

8000

You can fill larger memory areas, too. Just be a bit careful until you know the memory layout. There is a copy command 'k' as well. Let's copy the second row starting from 0x8010 to the first row starting at 0x8000 by typing

k 8010 801f 8000 <ENTER> 8000.801f <ENTER>

which will output the result

8000 d2 dd ab c6 8f d7 26 f3 8f 0e 08 62 9f 2d c0 ee 8010 d2 dd ab c6 8f d7 26 f3 8f 0e 08 62 9f 2d c0 ee 8000

as expected. Let's try to disassemble something. Since the only program in memory right now is the OS itself at 0xf000, let's type

i f000 <ENTER>

which shows us

f000 JPA f015 f003 JPA f03c f006 JPA f327 f009 JPA f347 f00c JPA f376 f00f JPA f8bb f012 JPA f91b f015 LDI fe f017 STA ffff

and so on. Press 'q' if you have seen enough. Until now, we haven't actually changed any memory content. Let's store some data by using the ':' command:

8000: 0 1 2 3 4 5 6 7 8 9 a b c d e f <ENTER>

Taking a look at that memory again with '8000.800f <ENTER>' shows

8000 00 01 02 03 04 05 06 07 08 09 0a 0b 0c 0d 0e 0f 8000

We can use that feature to input mnemonics, too. Try the following:

```

8000: INP BEQ 00 80 OUT JPA 00 80 <ENTER> 8000 r <ENTER>

```

Congratulations! You have just written your first assembler program on the Minimal. It is reading the UART, printing out any keystrokes immediately to the screen. Try typing something!

```

Hello World! ajshkjdahskdjhaskdjhaskd

```

Okay, we can't get back to the monitor since our program is running in an endless loop. Simply press RESET. You don't have to enter longer programs by hand of course! Just copy and paste the following assembled program into your serial terminal:

```

8000

:0e fe 16 ff ff 0e 13 35 fd 0e 80

:35 fc 38 22 80 14 05 80 48 65 6c

:6c 6f 2c 20 57 6f 72 6c 64 21 0a

:00 34 ff 16 44 80 34 fe 16 45 80

:1d 44 80 11 00 3b 43 80 02 00 00

:00 00 00 00 00 00 2e 44 80 14 2c

:80 39 00 00

8000

```

and enter 'r' for run and you should see this:

```

Hello, World!

Hello, World!

Hello, World!

Hello, World!

Hello, World!

```

You can use this method to upload any (even very large) programs from your host computer into the RAM of the Minimal.

## **Memory Layout**

The address space of the Minimal is 16 bits wide and reaches 64KB at 0x0000-0xffff. This address space is expanded to 512KB of FLASH memory, which can be accessed in 16 chunks of 32KB called banks. The active bank is controlled by the 4-bit bank register.

```

0x0000 - 0x7fff 32KB of active FLASH SSD bank

0x0000 - 0x0033 Bank 0: OS boot loader and dummy file header

```

```

0 \times 0034 - 0 \times 0fff

Bank 0: OS image, gets copied to RAM upon RESET

0 \times 1000 - 0 \times 7 fff

Bank 0: free

0x8000 - 0xffff

32KB of RAM

0xe000 - 0xefff

used temporarily by the SSD file system

0xf000 - 0xfeff

MinOS operating system

0xfeb0 - 0xfec8

MinOS variables

0xfec9 - 0xfeff

MinOS line input buffer

0xff00 - 0xffff

256 bytes of CPU stack

0xffff

LSB of stack pointer (SP)

```

On bank 0 the first 4KB (0x0000-0x0fff) hold a write-protected and self-loading image of the operating system MinOS. The rest of bank 0 and all other SSD banks can be used for your programs and data.

Upon pressing RESET, the program counter and bank register are set to zero. The code starting at 0x0000 on bank 0 - the OS bootloader if you will - copies the OS image into the RAM area 0xf000-0xfeff and then jumps to 0xf000 into the boot monitor which in turn presents its start screen.

Please also keep in mind that several of Minimal's native software development tools, e. g. the text editor and assembler, make use of additional memory areas. See section 'Native Tool Chain' for more information.

## **SSD File System**

Although it is possible to access the FLASH memory area directly with read and write operations as detailed in the datasheet of the SST39SF040 FLASH, the operating system features a minimalistic file system that transforms the FLASH EEPROM into a viable SSD drive which greatly facilitates storing and retrieving your data by offering the following basic functionality:

#### SAVE

To save a block of memory to the currently selected SSD bank, type:

```

s <firstaddr> <lastaddr> <filename> ENTER

```

<firstaddr> and <lastaddr> denote the memory hex addresses of the

first and last byte to store and <filename> can be a string with a

maximum length of 19 characters. The start address <first> of the data

is stored as part of the file as detailed in the section 'file

format'.

#### LOAD

To load a saved block of memory back into RAM, just type:

1 <filename> ENTER

Note that the operating system only searches for the specified filename within the currently selected SSD bank.

### ZAP (DELETE)

In order to delete an existing file, type:

z <filename> ENTER

In case there exist two or more files of the same filename, it is always the oldest file that is deleted.

## TABLE OF CONTENT (DIRECTORY)

To show the content of the currently selected SSD bank, type:

t ENTER

#### WIPE (FORMAT)

In case you want to format the currently selected SSD bank, type:

w ENTER

All data stored on this SSD bank will be erased.

#### File Format

Data is stored as a 'file' by prepending a file header containing the following additional information to the data:

| 20 bytes | <filename></filename> | zero-terminated string               |

|----------|-----------------------|--------------------------------------|

| 2 bytes  | <address></address>   | destination address of <data></data> |

| 2 bytes  | <n></n>               | byte size of <data></data>           |

| N bytes  | <data></data>         | data section                         |

#### **Properties**

Within one SSD bank, it is possible to have multiple files with identical names. The file system acts like an upward-growing stack where the last-written file resides on the top of the stack. Deletion on the other hand always searches for the *oldest* occurrence of a given filename and only deletes this version.

When a file is deleted from the SSD, other files at higher addresses are moved down within the active SSD bank to close the gap. To

accomplish this, the file system uses the RAM area 0xe000-0xefff as a temporary data buffer.

## **Assembler Programming**

Writing your programs "close to the metal" will yield the fastest code. And it really helps develop a deep understanding of the inner workings of a CPU. Depositing byte values or mnemonics at memory locations - as we have seen above - already allows you to input short programs. It is much more convenient however, to let an assembler translate your program into machine code.

Currently there are two cross-platform assemblers and even a native assembler available for the Minimal. The use of the native assembler is described in the section 'Native Tool Chain'. It supports the same syntax as the cross-platform versions.

Both cross-assemblers are simple command line tools running on your host PC that let you specify a filename of your source code and that output machine code to the console. That code will be in a format matching the 'set address' and 'deposit' commands of the OS that you can then cut & paste to the Minimal via a terminal emulation. The Minimal will "think" that you are just typing very quickly.

## **Assembler Syntax**

The assembler 'asm.exe' is written in C++ and runs on Windows whereas 'asm.py' runs platform-independently in any Python interpreter. To assemble a file, just type

asm <file> or python asm.py <file>.

The supported basic syntax is identical for both assembers but 'asm.exe' offers an additional #include functionality and a command line option for printing out symbol tables. Type asm -h or asm for more information. The following statements must be placed at the start of a line:

#org 0x80ff sets the program counter address to 0x80ff

#include file includes a file prior to assembling (asm.exe only)

#begin begins emitting the opcode (default)

#end ends emitting opcode (but the PC is still advanced)

label: defines a label as the start address of a line

The following statements may be placed within a line in any order:

| MNEMONIC                                                                      | emits the opcode of a mnemonic written in upper-case    |

|-------------------------------------------------------------------------------|---------------------------------------------------------|

| label                                                                         | emits the LSB and MSB of the address label              |

| <label< td=""><td>least significant byte (LSB) of address label</td></label<> | least significant byte (LSB) of address label           |

| >label                                                                        | most significant byte (MSB) of address label            |

| label+off                                                                     | emits the LSB and MSB of the address label+off          |

| label-off                                                                     | emits the LSB and MSB of the address label-off          |

|                                                                               | <off> can be any decimal number between 0 and 99.</off> |

| 0x8fff                                                                        | 16-bit hex word (will be decoded to LSB MSB)            |

| 0x8f                                                                          | 8-bit hex byte (negative numbers in 2's complement)     |

| -123 or 123                                                                   | 8-bit signed decimal byte                               |

| 'a'                                                                           | equivalent to 65 or 0x41                                |

| 'hello'                                                                       | byte string in memory (0x68 0x65 0x6c 0x6c 0x6f)        |

| 1,2,3 or 1 2 3                                                                | defines multiple bytes in memory                        |

| ; blablabla                                                                   | comment                                                 |

Labels and mnemonics are case-sensitive. Mnemonics are only accepted in upper-case. Use lower-case for hex numbers. Mathematical expressions and definitions of constants beyond the limited functionality described above are not supported.

#### **Instruction Set Overview**

Here you find a list of the available instruction types and their different address modes. Please note that not every address mode is available for every instruction type.

Legend: dark gray = not applicable, light gray = not implemented

| Description            | Accumulator<br>No Operand | Accumulator<br>Immediate |     |     | Byte at<br>Abs Address | Word at<br>Abs Address | Stack at<br>SP + Offset |

|------------------------|---------------------------|--------------------------|-----|-----|------------------------|------------------------|-------------------------|

| Load A from            |                           | LDI                      | LDA | LDR |                        |                        | LDS                     |

| Store A to             |                           |                          | STA | STR |                        |                        | STS                     |

| Clear                  |                           |                          |     |     | CLB                    | CLW                    |                         |

| Negate                 | NEG                       |                          |     |     | NEB                    | NEW                    |                         |

| Increment              | INC                       |                          |     |     | INB                    | INW                    |                         |

| Decrement              | DEC                       |                          |     |     | DEB                    | DEW                    |                         |

| Add                    |                           | ADI                      | ADA | ADR | ADB                    | ADW                    |                         |

| Subtract               |                           | SBI                      | SBA | SBR | SBB                    | SBW                    |                         |

| Compare                |                           | CPI                      | СРА | CPR |                        |                        |                         |

| Add with Carry In      |                           | ACI                      | ACA | ACR | ACB                    | ACW                    |                         |

| Subtract with Carry In |                           | SCI                      | SCA | SCR | SCB                    | SCW                    |                         |

|                        |     | l            |           |             |             |             |

|------------------------|-----|--------------|-----------|-------------|-------------|-------------|

| Jump to                |     | JPA          | JPR       |             |             |             |

| Jump to Subroutine     |     | JPS          |           |             |             |             |

| Return from Subroutine | RTS |              |           |             |             |             |

| No Operation / Wait    | NOP |              |           |             |             |             |

| Terminal Input         | INP |              |           |             |             |             |

| Set FLASH bank *       | BNK |              |           |             |             |             |

| Output A to Terminal   | OUT |              |           |             |             |             |

| Clear Carry In Flag    | CLC |              |           |             |             |             |

| Set Carry In Flag      | SEC |              |           | Accumulator | Accumulator | Accumulator |

| Logical Shift Left     | LSL | Descr        | iption    | No Operand  | Immediate   | Abs Address |

| Rotate Shift Left      | ROL | Branch on No | n-Zero    |             |             | BNE         |

| Logical Shift Right    | LSR | Branch on Ze | ro        |             |             | BEQ         |

| Rotate Shift Right     | ROR | Branch on Ca | rry Clear |             |             | всс         |

| Arithmetic Shift Right | ASR | Branch on Ca | rry Set   |             |             | BCS         |

| Push on Stack          | PHS | Branch on Pl | us        |             |             | BPL         |

| Pull from Stack        | PLS | Branch on Mi | nus       |             |             | BMI         |

<sup>\*</sup> has no effect on revision 1.3 (32KB FLASH Edition)

## **Instruction Set 1.3 - 1.5**

Software written for revision 1.3 - 1.5 will run on higher revisions.

Legend: A=accumulator, R=result, M=most significant byte, ?=undefined, -=unchanged

| Ins  | struct | ion | Description               | Target | 0peran | d    | Accumulator | F | lag | s | Clock  |

|------|--------|-----|---------------------------|--------|--------|------|-------------|---|-----|---|--------|

| Name | DEC    | HEX |                           |        | Туре   | Size | Change      | N | С   | Z | Cycles |

| NOP  | 0      | 0   | No Operation              | none   | none   | 0    | -           | - | -   | - | 16     |

| BNK  | 1      | 1   | Set FLASH bank *          | bank   | Α      | 0    | -           | - | -   | - | 4      |

| OUT  | 2      | 2   | UART Output               | UART   | Α      | 0    | -           | 1 | 0   | 0 | 4      |

| CLC  | 3      | 3   | Clear Carry In Flag       | none   | none   | 0    | -           | 1 | 0   | 0 | 5      |

| SEC  | 4      | 4   | Set Carry In Flag         | none   | none   | 0    | -           | 0 | 1   | 1 | 5      |

| LSL  | 5      | 5   | Logical Shift Left (=ASL) | Α      | none   | 0    | R           | R | R   | R | 5      |

| ROL  | 6      | 6   | Rotate Shift Left         | Α      | none   | 0    | R           | R | R   | R | 5      |

| LSR  | 7      | 7   | Logical Shift Right       | Α      | none   | 0    | R           | R | R   | R | 13     |

| ROR  | 8      | 8   | Rotate Shift Right        | Α      | none   | 0    | R           | R | R   | R | 12     |

| ASR  | 9      | 9   | Arithmetic Shift Right    | Α      | none   | 0    | R           | R | R   | R | 15     |

| INP  | 10     | 0A  | UART Input incl. CPI 0xff | Α      | none   | 0    | R           | R | R   | R | 6      |

| NEG  | 11     | 0B  | Negate                    | Α      | none   | 0    | R           | R | ?   | R | 6      |

| INC  | 12     | 9C  | Increment                 | Α      | none   | 0    | R           | R | R   | R | 5      |

| DEC  | 13     | 0D  | Decrement                 | Α      | none   | 0    | R           | R | R   | R | 5      |

| LDI       14       0E       Load from       A       immediate       1       R       -         ADI       15       0F       Add       A       immediate       1       R       R         SBI       16       10       Subtract       A       immediate       1       R       R         CPI       17       11       Compare       A       immediate       1       -       R         ACI       18       12       Add with Carry In       A       immediate       1       R       R         SCI       19       13       Subtract with Carry In       A       immediate       1       R       R         JPA       20       14       Jump to       PC       abs addr       2       -       -         LDA       21       15       Load from       A       abs addr       2       R       -         STA       22       16       Store A to       byte @ abs addr       2       -       -         ADA       23       17       Add       A       abs addr       2       R       R         SBA       24       18       Subtract       A       abs add | - R R R R R | - R R R R   | 4<br>5<br>5<br>5<br>5<br>5 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|----------------------------|

| SBI       16       10       Subtract       A       immediate       1       R       R         CPI       17       11       Compare       A       immediate       1       -       R         ACI       18       12       Add with Carry In       A       immediate       1       R       R         SCI       19       13       Subtract with Carry In       A       immediate       1       R       R         JPA       20       14       Jump to       PC       abs addr       2       -       -         LDA       21       15       Load from       A       abs addr       2       R       -         STA       22       16       Store A to       byte @ abs addr       2       -       -         ADA       23       17       Add       A       abs addr       2       R       R         SBA       24       18       Subtract       A       abs addr       2       R       R                                                                                                                                                              | R R R       | R<br>R<br>R | 5<br>5<br>5<br>5           |

| CPI         17         11         Compare         A         immediate         1         -         R           ACI         18         12         Add with Carry In         A         immediate         1         R         R           SCI         19         13         Subtract with Carry In         A         immediate         1         R         R           JPA         20         14         Jump to         PC         abs addr         2         -         -           LDA         21         15         Load from         A         abs addr         2         R         -           STA         22         16         Store A to         byte @ abs addr         2         -         -           ADA         23         17         Add         A         abs addr         2         R         R           SBA         24         18         Subtract         A         abs addr         2         R         R                                                                                                               | R R         | R<br>R<br>R | 5<br>5<br>5                |

| ACI       18       12       Add with Carry In       A       immediate       1       R       R         SCI       19       13       Subtract with Carry In       A       immediate       1       R       R         JPA       20       14       Jump to       PC       abs addr       2       -       -         LDA       21       15       Load from       A       abs addr       2       R       -         STA       22       16       Store A to       byte @       abs addr       2       -       -         ADA       23       17       Add       A       abs addr       2       R       R         SBA       24       18       Subtract       A       abs addr       2       R       R                                                                                                                                                                                                                                                                                                                                                 | R R         | R<br>R      | 5                          |

| SCI         19         13         Subtract with Carry In         A         immediate         1         R         R           JPA         20         14         Jump to         PC         abs addr         2         -         -           LDA         21         15         Load from         A         abs addr         2         R         -           STA         22         16         Store A to         byte @ abs addr         2         -         -           ADA         23         17         Add         A         abs addr         2         R         R           SBA         24         18         Subtract         A         abs addr         2         R         R                                                                                                                                                                                                                                                                                                                                                     | R           | R<br>-      | 5                          |

| JPA         20         14         Jump to         PC         abs addr         2         -         -           LDA         21         15         Load from         A         abs addr         2         R         -           STA         22         16         Store A to         byte @ abs addr         2         -         -           ADA         23         17         Add         A         abs addr         2         R         R           SBA         24         18         Subtract         A         abs addr         2         R         R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -           | -           |                            |

| LDA       21       15       Load from       A       abs addr       2       R       -         STA       22       16       Store A to       byte @ abs addr       2       -       -         ADA       23       17       Add       A       abs addr       2       R       R         SBA       24       18       Subtract       A       abs addr       2       R       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -           | ⊢           | 6                          |

| STA         22         16         Store A to         byte @ abs addr 2          -           ADA         23         17         Add         A abs addr 2         R R         R           SBA         24         18         Subtract         A abs addr 2         R R         R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -           | -           |                            |

| ADA         23         17         Add         A         abs addr         2         R         R           SBA         24         18         Subtract         A         abs addr         2         R         R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ╁           |             | 7                          |

| SBA 24 18 Subtract A abs addr 2 R R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R           | -           | 8                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             | R           | 8                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R           | R           | 8                          |

| CPA         25         19         Compare         A         abs addr         2         -         R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R           | R           | 8                          |

| ACA 26 1A Add with Carry In A abs addr 2 R R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R           | R           | 8                          |

| SCA   27   1B   Subtract with Carry In   A   abs addr   2   R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R           | R           | 8                          |

| JPR   28   1C   Jump to   PC   rel addr   2   -   -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -           | -           | 9                          |

| LDR 29 1D Load from A reladdr 2 R -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -           | -           | 10                         |

| STR 30 1E Store A to byte @ rel addr 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -           | -           | 10                         |

| ADR 31 1F Add A reladdr 2 R R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R           | R           | 11                         |

| SBR 32 20 Subtract A reladdr 2 R R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R           | R           | 11                         |

| CPR         33         21         Compare         A         rel addr         2         -         R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R           | R           | 11                         |

| ACR 34 22 Add with Carry In A rel addr 2 R R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R           | R           | 11                         |

| SCR 35 23 Subtract with Carry In A rel addr 2 R R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R           | R           | 11                         |

| CLB3624Clearbyte @ abs addr2R0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1           | 0           | 8                          |

| NEB3725Negatebyte @ abs addr2R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ?           | R           | 10                         |

| INB 38 26 Increment byte @ abs addr 2 R R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R           | R           | 10                         |

| DEB3927Decrementbyte @ abs addr2R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R           | R           | 10                         |

| ADB         40         28         Add         byte @ abs addr         2         -         R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R           | R           | 9                          |

| SBB 41 29 Subtract byte @ abs addr 2 - R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R           | R           | 10                         |

| ACB 42 2A Add with Carry In byte @ abs addr 2 - R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R           | R           | 11                         |

| SCB 43 2B Subtract with Carry In byte @ abs addr 2 - R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R           | R           | 11                         |

| CLW         44         2C         Clear         word @ abs addr         2         -         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1           | 0           | 10                         |

| NEW452DNegateword @ abs addr2?M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ?           | М           | 13                         |

| INW 46 2E Increment word @ abs addr 2 ? M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | М           | М           | 13                         |

| DEW 47 2F Decrement word @ abs addr 2 ? M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | М           | М           | 13                         |

| ADW         48         30         Add         word @ abs addr         2         ?         M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | М           | М           | 12                         |

| SBW         49         31         Subtract         word @ abs addr         2         ?         M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | М           | М           | 13                         |

| ACW 50 32 Add with Carry In word @ abs addr 2 ? M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | М           | М           | 13                         |

| SCW | 51 | 33 | Subtract with Carry In | word @ | abs addr | 2 | ? | М | М | М | 14    |

|-----|----|----|------------------------|--------|----------|---|---|---|---|---|-------|

| LDS | 52 | 34 | Load from Stack        | Α      | offset   | 1 | R | ? | ? | ? | 9     |

| STS | 53 | 35 | Store A on Stack       | stack  | offset   | 1 | - | ? | ? | ? | 16    |

| PHS | 54 | 36 | Push on Stack          | stack  | none     | 0 | - | ? | ? | ? | 12    |

| PLS | 55 | 37 | Pull from Stack        | Α      | none     | 0 | R | ? | ? | ? | 10    |

| JPS | 56 | 38 | Jump to Subroutine     | PC     | abs addr | 2 | ? | ? | ? | ? | 16    |

| RTS | 57 | 39 | Return from Subroutine | PC     | none     | 0 | ? | ? | ? | ? | 14    |

| BNE | 58 | 3A | Branch on Non-Zero     | PC     | abs addr | 2 | - | - | - | 1 | 5/6** |

| BEQ | 59 | 3B | Branch on Zero         | PC     | abs addr | 2 | - | - | - | 1 | 5/6** |

| ВСС | 60 | 3C | Branch on Carry Clear  | PC     | abs addr | 2 | - | - | - | 1 | 5/6** |

| BCS | 61 | 3D | Branch on Carry Set    | PC     | abs addr | 2 | - | - | - | - | 5/6** |

| BPL | 62 | 3E | Branch on Plus         | PC     | abs addr | 2 | - | - | - | 1 | 5/6** |

| BMI | 63 | 3F | Branch on Minus        | PC     | abs addr | 2 | - | - | - | - | 5/6** |

<sup>\*</sup> has no effect on board revisions prior to 1.5

## **Instruction Set 1.6**

This table shows the detailed properties of each instruction of revision 1.6. Improvements with respect to revision 1.3 - 1.5 are small but noticeable and are highlighted below in cyan. Software explicitly exploiting these changes will not run on earlier revisions.

Legend: A=accumulator, R=result, M=most significant byte, ?=undefined, -=unchanged

| Ins  | struct | ion | Description               | Target | 0peran | d    | Accumulator | F | lag | s | Clock  |

|------|--------|-----|---------------------------|--------|--------|------|-------------|---|-----|---|--------|

| Name | DEC    | HEX |                           |        | Туре   | Size | Change      | N | С   | Z | Cycles |

| NOP  | 0      | 0   | No Operation              | none   | none   | 0    | -           | ı | ı   | ı | 16     |

| BNK  | 1      | 1   | Set FLASH bank *          | bank   | Α      | 0    | -           | ı | ı   | ı | 4      |

| OUT  | 2      | 2   | UART Output               | UART   | Α      | 0    | -           | 1 | 0   | 0 | 4      |

| CLC  | 3      | 3   | Clear Carry In Flag       | none   | none   | 0    | -           | 1 | 0   | 0 | 5      |

| SEC  | 4      | 4   | Set Carry In Flag         | none   | none   | 0    | -           | 0 | 1   | 1 | 5      |

| LSL  | 5      | 5   | Logical Shift Left (=ASL) | Α      | none   | 0    | R           | R | R   | R | 5      |

| ROL  | 6      | 6   | Rotate Shift Left         | Α      | none   | 0    | R           | R | R   | R | 5      |

| LSR  | 7      | 7   | Logical Shift Right       | Α      | none   | 0    | R           | R | R   | R | 13     |

| ROR  | 8      | 8   | Rotate Shift Right        | Α      | none   | 0    | R           | R | R   | R | 12     |

| ASR  | 9      | 9   | Arithmetic Shift Right    | Α      | none   | 0    | R           | R | R   | R | 15     |

| INP  | 10     | 0A  | UART Input and CPI 0xff   | Α      | none   | 0    | R           | R | R   | R | 6      |

| NEG  | 11     | 0B  | Negate                    | Α      | none   | 0    | R           | R | ?   | R | 6      |

| INC  | 12     | 9C  | Increment                 | Α      | none   | 0    | R           | R | R   | R | 5      |

| DEC  | 13     | 0D  | Decrement                 | Α      | none   | 0    | R           | R | R   | R | 5      |

<sup>\*\* 6</sup> cycles if branching

| LDI         14         0E         Load from         A         immediate         1         R         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R                                         | 4<br>5<br>5<br>5<br>5<br>5<br>7<br>7<br>8<br>8<br>8<br>8<br>8<br>8 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| SBI         16         10         Subtract         A         immediate         1         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R                                          | 5<br>5<br>5<br>5<br>7<br>7<br>8<br>8<br>8<br>8<br>8<br>8           |