## Anatomia do Cl 74xxy595 - Como funciona o Cl 74xxy595.

Shift Registers (Registradores por deslocamento) 1 entrada serial e 8 saídas paralelas.

Fonte: https://www.nxp.com/documents/data\_sheet/74HC\_HCT595.pdf

Vou procurar ser o mais simples possível nesta anatomia. Tentarei usar termos comuns nas explicações.

### **Aplicações**

Serial-to-parallel data conversion; Remote control holding register.

#### Características:

8-bit serial input; 8-bit serial or parallel output; Storage register with 3-state outputs; Shift register with direct clear; 100 MHz (typical) shift out frequency.

#### Alimentação:

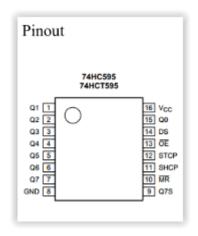

O CI 74HC595 é fabricado para CMOS. Voltagens de + 2 V até +6 V. E o 74HCT595: TTL. Voltagens de + 4,5 V até +5,5 V. Gnd pino 8 VCC pino 16

## **NOMES DAS LINHAS (PINOS)**

| DS   | entrada de dados serial              | Q0 | dado de saida paralela 0 |

|------|--------------------------------------|----|--------------------------|

| SHCP | entrada de clock do shift register   | Q1 | dado de saida paralela 1 |

| MR   | master reset (zera tudo se for 0)    | Q2 | dado de saida paralela 2 |

| STCP | entrada de clock do storage register | Q3 | dado de saida paralela 3 |

| OE         | comando de saida (ativa dados se for 0) | Q4 | dado de saida paralela 4 |

|------------|-----------------------------------------|----|--------------------------|

| Q7S        | descarte do ultimo dado serial          |    | Q5 dado de saida         |

| paralela 5 |                                         |    |                          |

|            |                                         | Q6 | dado de saida paralela 6 |

|            |                                         | Q7 | dado de saida paralela 7 |

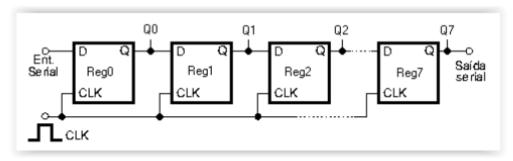

Este CI, como o nome diz, é um deslocador de registrador.

Ele desloca um bit recebido na entrada para cada registrador em cada pulso de um clock. Esta função é a transformação de serie em paralelo.

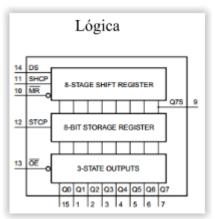

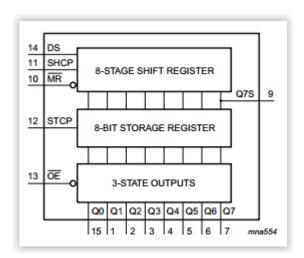

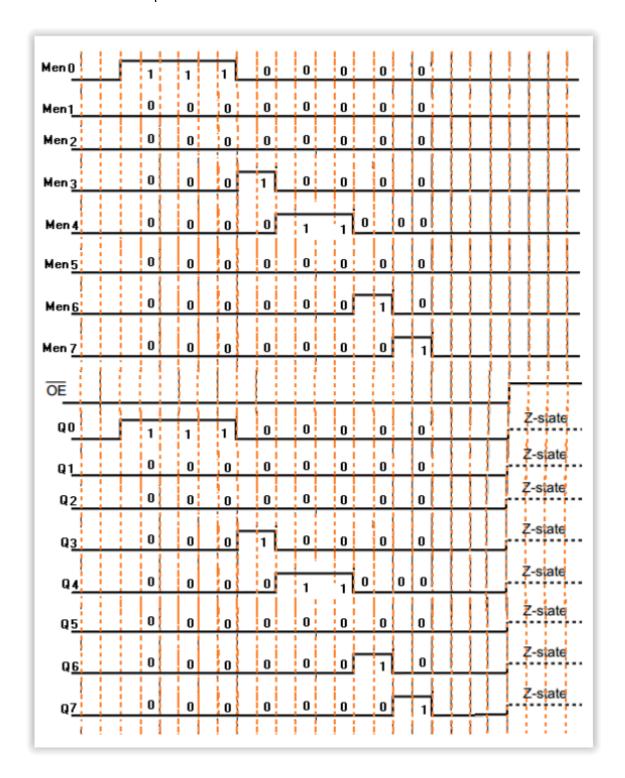

Como podemos ver na lógica ele é dividido em 3 partes:

O estágio de deslocamento ==> 8-STAGE SHIFT REGISTER

O estágio de memorização ==> 8-STAGE STORAGE REGISTER

A saída ==> 3-STATE SHIFT REGISTER

# Característica dos estágios.

### Estágio de deslocamento

Este estágio tem a capacidade de deslocar 8 bits, tem uma entrada (Pino 14 DS) e uma saída (Pino 9 Q7S).

Tem também 2 linhas (Pinos 10 MR e pino11 SHCP) de controle.

A linha MR (reset), ao ser colocada em nível baixo (0V), coloca todas saídas dos registradores em nível baixo (0V,Gnd). Em nível alto (+5V), não afeta o funcionamento dos registradores. A linha SHCP é o clock que movimenta o deslocamento dos registradores.

Este estágio tem ainda 8 bits de saída internas que fornecem dados para o próximo estágio. O estágio de memorização.

#### Estágio de memorização.

Este estágio tem capacidade de guardar 8 bits de dados recebidos do estágio anterior. O estágio de deslocamento.

(Ele não tem nenhuma saída externa.) Tem somente uma linha de controle. (Pino 12 STCP). Este estágio tem ainda 8 bits internos de saída que fornecem dados para o próximo estagio.

A saída.

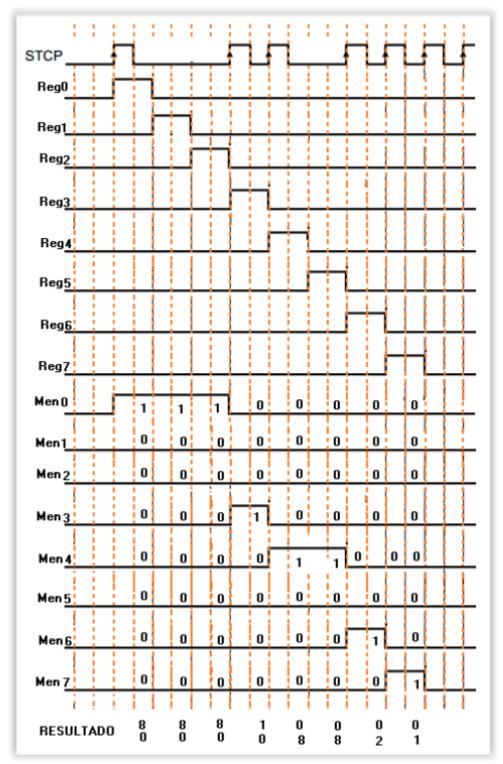

#### A saída.

Este estágio tem capacidade de dar saída externa a 8 bits de dados recebidos do estágio anterior.

Estágio de memorização.

Tem somente uma linha de controle. (Pino 13 OE).

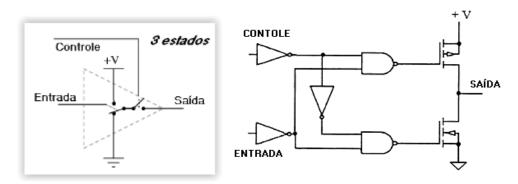

Esta saída pode ter 3 estados diferentes. Nível alto (+5V), nível baixo (0V, Gnd) e alta impedância (Z-state).

Seguem desenhos de como funciona uma saída de 3 estados.

Se a linha de controle estiver em 0V, a saída fica em nível de alta impedância, ou seja é como se a saída estivesse desligada de qualquer contato com o circuito seguinte, como mostra a figura.

Mas se a linha de controle estiver em +5V, a saída terá o valor da entrada, +5V ou 0V(Gnd).

#### **FUNCIONAMENTO GERAL.**

#### Estágio de deslocamento.

Primeiro, faremos um reset geral colocando a linha MR em 0V, e depois voltando para +5V. A cada subida do pulso de clock, ( 0V para +5V), todos bits dos registradores serão deslocados assim:

Ao ocorrer um pulso de subida do clock, o bit 7 vai para saída, bit 6 para bit 7, bit 5 para bit 6 ...... bit 0 para bit 1 e DS para bit 0.

Como houve um reset anterior, somente o bit 0 pode ter um valor diferente de 0, e ele terá o valor que estava na entrada no momento que o clock subiu, ou 0V ou +5V.

Estas saídas dos registradores, exceto Q7S, são internas ao CI, e não estarão disponíveis ao projetista.

Abaixo uma carta de tempo mostrando a situação descrita.

Como disse anteriormente, somente a saída Q7S pode ser acessada pelo projetista. A cada ciclo do clock, o byte formado pelas saídas dos registradores terá um valor. (RESULTADO)

Agora vamos ver como funciona o segundo estágio.

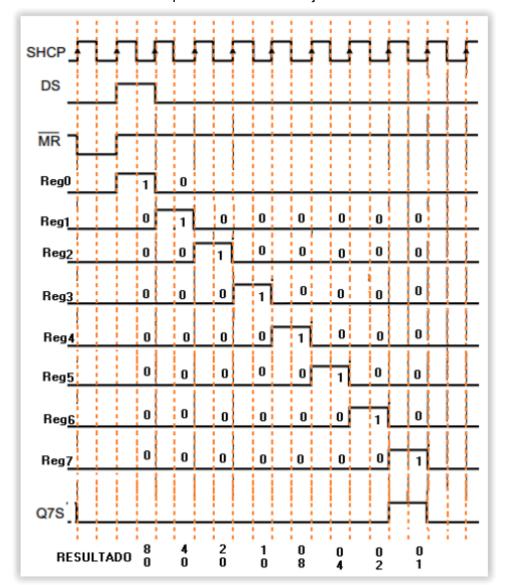

## Estágio de memorização.

Este estágio tem como entrada as saídas dos registradores e consegue memorizar o valor destas saídas.

Para que os valores destas memórias reflitam os valores das saídas dos registradores, é necessário que a linha STCP (Pino 12) fique em nível alto (+5V).

Se esta linha estiver em 0V, os valores nas memórias permanecem inalterados mesmo com mudança na entrada.

No momento de subida do clock, cada bit de memória ficará com o mesmo valor da saída do bit relativo do registrador.

A carta de tempo abaixo mostra este funcionamento.

A linha STCP, que transfere o valor dos registradores para as memórias, normalmente tem um ciclo constante para manter os dados na seqüência quando se está "desserializando" o byte. Mas nada impede de ser usado da forma que está na carta de tempo acima.

Claro que desta forma o valor do byte final estará diferente daquele que entrou em serie.

Usei esta sequência de pulsos no STCP para dar maior entendimento de como esta linha transfere os valores nos registradores para as memórias.

Na linha da carta de tempo com nome RESULTADO, aparecem os valores que estarão presente nas memórias em cada pulso de clock.

As saídas das memórias também não são diretamente acessadas pelo projetista.

#### A saída.

Esta é a parte do CI que permite que o projetista tenha acesso aos dados presentes nas memória,

mas este acesso só será possível se a linha (OE) estiver em nível 0V.

Se ela estive em +5V, as saídas ficam em alta impedância, (Z-state) conforme descrito no inicio.

Abaixo carta de tempo mostrando as saídas de Q0 até Q7.

Links para outras informações sobre deslocamento de registradores (Shift regs).

http://www.newtoncbraga.com.br/index.php/eletronica-digital/102-licao-11-como-funcionam-os-registradores-de-deslocamento-shift-registers

https://learn.adafruit.com/adafruit-arduino-lesson-4-eight-leds/the-74hc595-shift-register