www.parallax.com/P2 · sales@parallax.com · support@parallax.com · +1 888-512-1024

# Propeller 2 P2X8C4M64P Hardware Manual (Draft)

This draft is approximately 75% of the anticipated material. It is released open to commenting and feedback from the Propeller 2 community. The latest draft is posted to the documentation section of <u>parallax.com/P2</u>.

#### **COPYRIGHTS AND TRADEMARKS**

This documentation is copyright © 2021 by Parallax Inc. By downloading or obtaining a printed copy of this documentation or software you agree that it is to be used with, or with products containing, the Parallax Propeller 2 P2X8C4M64P microcontroller. Any other uses are not permitted and may represent a violation of Parallax copyrights, legally punishable according to Federal copyright or intellectual property laws. Any duplication of this documentation for commercial uses is expressly prohibited by Parallax Inc. Duplication for educational use is permitted, subject to the following Conditions of Duplication: Parallax Inc. grants the user a conditional right to download, duplicate, and distribute this text without Parallax's permission. This right is based on the following conditions: the text, or any portion thereof, may not be duplicated for commercial use; it may be duplicated only for educational purposes when used solely in conjunction with Parallax products, and the user may recover from the student only the cost of duplication.

Parallax, Propeller Spin, and the Parallax logos are trademarks of Parallax Inc. If you decide to use any trademarks of Parallax Inc. on your web page or in printed material, you must state that (trademark) is a trademark of Parallax Inc." upon the first appearance of the trademark name in each printed document or web page. Other brand and product names herein are trademarks or registered trademarks of their respective holders.

#### DISCLAIMER OF LIABILITY

Parallax, Inc. makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Parallax, Inc. assume any liability arising out of the application or use of any product, and specifically disclaims any and all liability, including without limitation consequential or incidental damages even if Parallax, Inc. has been advised of the possibility of such damages.

#### INTERNET DISCUSSION LISTS

We maintain active web-based discussion forums for people interested in Parallax Propeller products, at forums.parallax.com.

#### **ERRATA**

While great effort is made to assure the accuracy of our texts, errors may still exist. If you find an error, please let us know by commenting/suggesting on live documentation, or by sending an email to editor@parallax.com. We continually strive to improve all of our educational materials and documentation, and frequently revise our texts. Occasionally, an errata sheet with a list of known errors and corrections for a given text will be posted to our website, www.parallax.com. Please check the individual product page's free downloads for an errata file.

#### SUPPORTED HARDWARE AND FIRMWARE

This manual is valid with the following hardware and firmware versions:

| Hardware   | Firmware |

|------------|----------|

| P2X8C4M64P | Rev B/C  |

#### **CREDITS**

Authorship: Jeff Martin • Format & Editing: Stephanie Lindsay • Technical Graphics: Michael Mulholland With many thanks to everyone in the Propeller Community and staff at Parallax Inc.

# **TABLE OF CONTENTS**

| PREFACE                            |    |  |

|------------------------------------|----|--|

| CONVENTIONS                        | 7  |  |

| OVERVIEW                           | 8  |  |

| Specifications                     | 9  |  |

| Package Description                | 10 |  |

| Hardware Connections               | 11 |  |

| Operation                          | 12 |  |

| Boot Up                            | 12 |  |

| Runtime                            | 12 |  |

| Shutdown                           | 13 |  |

| Rebooting                          | 13 |  |

| System Clock                       | 14 |  |

| Memory                             | 14 |  |

| COGS (PROCESSORS)                  | 14 |  |

| Cog Memory                         | 16 |  |

| Register RAM                       | 16 |  |

| General Purpose Registers          | 16 |  |

| Dual-Purpose Registers             | 16 |  |

| Special-Purpose Registers          | 17 |  |

| Lookup RAM                         | 17 |  |

| Scratch Space                      | 17 |  |

| Paired-Cog Communication Mechanism | 17 |  |

| Instruction Pipeline               | 18 |  |

| Instruction Stages                 | 18 |  |

| Pipeline                           | 19 |  |

| Wait (Pipeline Stall)              | 19 |  |

| Branch (Pipeline Flush)            | 20 |  |

| Execution                          | 21 |  |

| Register Execution                 | 21 |  |

| Lookup Execution                   | 21 |  |

| Hub Execution                      | 21 |  |

|                                    |    |  |

|    | Starting And Stopping Cogs                                  | 22 |

|----|-------------------------------------------------------------|----|

|    | Cog Attention                                               | 22 |

|    | System Counter                                              | 23 |

|    | Pseudo-Random Number Generator                              | 23 |

| HU | В                                                           | 24 |

|    | Hub RAM                                                     | 24 |

|    | Random Access                                               | 25 |

|    | Sequential Access                                           | 25 |

|    | Protected RAM                                               | 26 |

|    | System Clock Configuration                                  | 26 |

|    | PLL Example                                                 | 28 |

|    | Locks (Semaphores)                                          | 28 |

|    | Lock Usage                                                  | 29 |

|    | CORDIC Solver                                               | 29 |

|    | Multiply                                                    | 30 |

|    | Divide                                                      | 30 |

|    | Square Root                                                 | 30 |

|    | Rotation                                                    | 30 |

|    | Cartesian to Polar                                          | 31 |

|    | Polar to Cartesian                                          | 31 |

|    | Integer to Logarithm                                        | 31 |

|    | Logarithm to Integer                                        | 31 |

| SM | IART I/O PINS                                               | 32 |

|    | I/O Pin Circuit                                             | 32 |

|    | Direction and State                                         | 33 |

|    | Pin Modes                                                   | 33 |

|    | Equivalent Schematics for Each Unique I/O Pin Configuration | 37 |

|    | I/O Pin Timing                                              | 43 |

|    | Smart Modes                                                 | 44 |

|    | Smart Pin Off; Default (%00000)                             | 47 |

|    | Long Repository (%00001%00011 and not DAC_MODE)             | 47 |

| DAC Noise (%00001 and DAC_MODE)                                                         | 47 |

|-----------------------------------------------------------------------------------------|----|

| DAC 16-Bit With Noise Dither (%00010 and DAC_MODE)                                      | 47 |

| DAC 16-Bit With PWM dither (%00011 and DAC_MODE)                                        | 47 |

| Pulse/Cycle Output (%00100)                                                             | 48 |

| Transition Output (%00101)                                                              | 48 |

| NCO Frequency (%00110)                                                                  | 48 |

| NCO Duty (%00111)                                                                       | 48 |

| PWM Triangle (%01000)                                                                   | 48 |

| PWM Sawtooth (%01001)                                                                   | 49 |

| PWM Switch-Mode Power Supply With Voltage And Current Feedback (%01010)                 | 49 |

| A/B-Input Quadrature Encoder (%01011)                                                   | 50 |

| Count A-Input Positive Edges When B-Input Is High (%01100)                              | 50 |

| Count A-Input Positive Edges; Increment w/B-Input = 1, Decrement w/B-Input = 0 (%01101) | 50 |

| Count A-Input Positive Edges (%01110 AND !Y[0])                                         | 50 |

| Increment w/A-Input Positive Edge, Decrement w/B-Input Positive Edge (%01110 AND Y[0])  | 50 |

| Count A-Input Highs (%01111 AND !Y[0])                                                  | 51 |

| Increment w/A-Input High, Decrement w/B-Input High (%01111 AND Y[0])                    | 51 |

| Time A-Input States (%10000)                                                            | 51 |

| Time A-Input High States (%10001)                                                       | 51 |

| Time X A-Input Highs/Rises/Edges (%10010 AND !Y[2])                                     | 51 |

| Timeout on X Clocks Of Missing A-Input High/Rise/Edge (%10010 AND Y[2])                 | 52 |

| Count Time For X Periods (%10011)                                                       | 52 |

| Count State For X Periods (%10100)                                                      | 52 |

| Count Time For Periods In X+ Clock Cycles (%10101)                                      | 52 |

| Count States For Periods In X+ Clock Cycles (%10110)                                    | 52 |

| Count Periods For Periods In X+ Clock Cycles (%10111)                                   | 52 |

| ADC Sample/Filter/Capture, Internally Clocked (%11000)                                  | 53 |

| ADC Sample/Filter/Capture, Externally Clocked (%11001)                                  | 53 |

| About SINC2 and SINC3 filtering                                                         | 54 |

| SINC2 Sampling Mode (%00)                                                               | 54 |

| SINC2 Filtering Mode (%01)                                                              | 55 |

| SINC3 Filtering Mode (%10)                                                              | 55 |

| Bitstream Capturing Mode (%11)                                                          | 56 |

|                                                                                         |    |

| ADC Scope With Trigger (%11010)            | 56 |  |  |

|--------------------------------------------|----|--|--|

| SCOPE Data Pipe                            | 57 |  |  |

| USB Host/Device (%11011)                   | 58 |  |  |

| Synchronous Serial Transmit (%11100)       | 59 |  |  |

| Synchronous Serial Receive (%11101)        | 60 |  |  |

| Asynchronous Serial Transmit (%11110)      | 60 |  |  |

| Asynchronous Serial Receive (%11111)       | 61 |  |  |

| HOST COMMUNICATION                         | 61 |  |  |

| Download Propeller Application             | 61 |  |  |

| Multiprogramming                           | 62 |  |  |

| Loader Parsing Notes                       | 63 |  |  |

| Prop_Chk                                   | 63 |  |  |

| Prop_Clk                                   | 63 |  |  |

| Prop_Hex                                   | 64 |  |  |

| Prop_Txt                                   | 65 |  |  |

| Interactive Mode                           | 65 |  |  |

| P2 Monitor                                 | 66 |  |  |

| TAQOZ                                      | 66 |  |  |

| PROPELLER 2 RESERVED WORDS (SPIN2 + PASM2) | 67 |  |  |

| GENERAL PURPOSE I/O PIN EXCEPTIONS         | 69 |  |  |

| CHANGE LOG                                 | 70 |  |  |

| PARALLAX INCORPORATED                      |    |  |  |

## **PREFACE**

Thank you for exploring the Propeller microcontroller! Here you will learn about the second member in the Propeller family - the Propeller 2 (P2X8C4M64P)

The Propeller 2 is the culmination of countless ideas, wishes, suggestions, and intense work by Parallax's Chip Gracey and the dedicated Propeller Community of engineers and makers. It is perhaps the most openly-designed microcontroller; constantly revised and discussed on the public Propeller forums, with interim designs released as FPGA-runnable images and direct community efforts making it all the way to final silicon available today.

This manual is an in-depth description of the concepts, features, and hardware of the Propeller 2 multicore microcontroller. It serves as a reference beyond that of the Propeller 2 Datasheet. Wherever code is needed to demonstrate a hardware feature, this manual will only use PASM2 (the core language). Other languages like Spin2 and C have similar capabilities - refer to the desired language documentation as needed.

For additional documentation and resources, including programming tools, visit www.parallax.com/P2. The latest version of this manual, along with links to a commentable Google Doc version, are available from the Documentation section. In addition, there are links to more in-depth references for the Propeller 2 and its Spin2 and PASM2 languages, which may include commentable Google Docs.

## CONVENTIONS

- % indicates a binary number (containing the digits 0 and 1, and underscore "\_" characters)

- ex: %0101 and %11000111

- \$ indicates a hexadecimal number (containing the digits 0-9, A-F, and underscore "\_" characters)

- ex: \$2AF and \$0D816

- x indicates a group of symbols where the x-part can vary

- ex: INx means both INA and INB

- ex: RDxxxx / WRxxx means RDBYTE, RDWORD, etc. and WRBYTE, WRWORD, etc.

-- or --

x - indicates a don't care bit in a binary number (a bit that can be 0 or 1 without affecting the execution context nor the explanation)

ex: %x\_1\_xxx0 and %xxxx10

## **OVERVIEW**

The Propeller microcontroller family provides high-speed processing for embedded systems while maintaining low current consumption and a small physical footprint. The Propeller provides flexibility and power through its multiple processors (called cogs) that perform simultaneous, independent or cooperative tasks, all while being easy to learn and utilize.

The Propeller 2 frees application developers from common complexities of embedded systems programming:

- Application design is flexible. Every processor (cog) has the same capabilities; no special-use cases.

- Most I/O pins have the same strengths; there are few location limits. Prototype with convenience, then produce with convenience, swapping pin responsibilities at-will with ease.

- Asynchronous events are easy to handle. Assign a dedicated cog to handle such an event, leaving other

cog(s) free to perform synchronous or independent processes, or split a cog's responsibilities between

synchronous tasks and asynchronous events using interrupts.

- Propeller Assembly language features conditional execution, optional result writing, loop-optimized timing, and runtime-selectable instruction skipping to provide fast, consistent timing and tight, multipurpose code that is capable of jitter-free event handling.

The Propeller 2 (P2X8C4M64P) microcontroller architecture consists of 8 identical 32-bit processors (cogs), each with their own RAM, which connect to a common hub and I/O pins. The hub provides 512 KB of shared RAM, a CORDIC math solver, and housekeeping facilities. The architecture includes 64 smart I/O pins, each capable of many autonomous analog and digital functions.

The Propeller 2's assembly language (PASM2) features per-instruction conditional execution, special looping mechanisms, and pattern-based instruction skipping to encourage fast, compact code.

The Propeller 2's high-level language (Spin2) provides fast, interpreted code that builds upon the power of the hardware and PASM2. The Spin2 language naturally encourages structured, yet terse constructs organized as methods grouped within reusable objects. Spin2 objects include other existing objects to extend their own functionality through the reuse of proven, open-source code.

Propeller 2 Applications, when developed using Spin2 and/or PASM2, integrate one or more objects into a complete program. Applications perform their duty by executing designated assignments within at least one cog (or across as many as eight); starting and stopping multiple cogs, utilizing raw I/O and Smart I/O, digital and analog signaling, streamers, and other built-in hardware as-needed to get the job done. This is how Parallax tools construct and use Propeller 2 Applications— there are other options made available by Propeller Community members featuring different languages, concepts, tools, and build techniques. Parallax lists other options in the Programming Tools section of the <u>Propeller 2 website</u>.

Each cog sits dormant until called into action—referred to as "launching a cog"—at which point the cog executes its given code independently from, and in parallel alongside, other active cogs. If needed, cogs may share information and coordinate actions together, either indirectly via shared <a href="Hub RAM">Hub RAM</a>, locks, or <a href="I/O pins">I/O pins</a>, or directly via paired <a href="Lookup RAM">Lookup RAM</a> or <a href="Cog attention">Cog attention</a> signals. Cogs may monitor and control I/O pins directly or can choose to employ smart modes (automated state machines) for sophisticated signalling. Each cog has independent access to every I/O pin at all times, though the cog collective ultimately decides the direction and state of each.

The Hub provides coordinated access to Hub RAM, the CORDIC math solver, and system management and configuration features. It serves a traffic management role, ensuring that any given unique element of any exclusive resource is not accessed simultaneously by multiple cogs. In most cases, cogs must wait their turn (once every eight clock cycles) to read or modify a shared element; however, even faster access to Hub RAM and the CORDIC solver are possible using a special feature.

# **Specifications**

|                            | Propeller 2 Specifications                                                            |  |  |  |

|----------------------------|---------------------------------------------------------------------------------------|--|--|--|

| Feature Specification      |                                                                                       |  |  |  |

| Model                      | P2X8C4M64P                                                                            |  |  |  |

| Power                      | 1.8 V Core, 3.3 V I/O                                                                 |  |  |  |

| Internal Oscillator        | ~24 MHz or ~20 kHz                                                                    |  |  |  |

| External Clock             | 10 - 20 MHz crystal (P2 Clock PLL enabled) or 0 to 180 MHz (nominal) clock oscillator |  |  |  |

| Nominal System Clock Speed | 180 MHz @ 105 °C                                                                      |  |  |  |

| Number of clock modes      | 6 + PLL ÷/× & 2 OSC load options                                                      |  |  |  |

| Cogs (cores)               | 8 identical                                                                           |  |  |  |

| Internal execution speed   | 0 to 720 MIPS (90 MIPS/cog) @ 180 MHz                                                 |  |  |  |

| Cog RAM                    | 512 longs (Register RAM) + 512 longs (Lookup RAM)                                     |  |  |  |

| Hub RAM                    | 512 KB (byte/word/long-addressable)                                                   |  |  |  |

| ROM                        | 16 KB (Bootloader, P2 Monitor debug interface, and TAQOZ (Forth) command interface)   |  |  |  |

| I/O Pins                   | 64; each featuring digital and analog signalling plus internal smart circuits         |  |  |  |

| Max current per I/O        | +/- 30mA                                                                              |  |  |  |

| Inter-cog communication    | Hub RAM, Lookup RAM, Attention Signal, or External I/O                                |  |  |  |

| Assembly language (PASM2)  | 358 instructions                                                                      |  |  |  |

| Interpreted languages      | Spin2 (Propeller Tool), TAQOZ (built-in), MicroPython, or Forth via community tools   |  |  |  |

| Compiled languages         | Spin (FlexGUI community Tool), BASIC, C/C++ (community tools)                         |  |  |  |

| PASM2 execution memory     | Register RAM + Lookup RAM + Hub RAM                                                   |  |  |  |

| Spin2 execution memory     | Hub RAM                                                                               |  |  |  |

For feature highlights, see also the <u>Propeller 2 website</u> and P2 Datasheet for feature highlights.

# **Package Description**

The P2X8C4M64P microcontroller is an exposed-pad TQFP-100 package. It contains 8 cogs, 512 KB of Hub RAM, and 64 Smart I/O pins. Refer to the P2 Datasheet for package dimensions.

| Part Number Legend |                     |                         |                   |  |  |

|--------------------|---------------------|-------------------------|-------------------|--|--|

| P2X 8C 4M 64P      |                     |                         |                   |  |  |

| Propeller 2        | 8 cogs (processors) | 4 Mbit Hub RAM (512 KB) | 64 smart I/O pins |  |  |

|                    | Pin Descriptions |                               |                                                                                                                                                                                                                                                                               |  |  |

|--------------------|------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name           | Direction        | Direction V (typ) Description |                                                                                                                                                                                                                                                                               |  |  |

| GND<br>[not shown] | -                | 0                             | Ground for core and smart pins; [not shown here] internally connected to underside exposed pad. Connect to ground plane for thermal dissipation.                                                                                                                              |  |  |

| TEST               | I                | 0                             | Tied to ground                                                                                                                                                                                                                                                                |  |  |

| VDD                | -                | 1.8                           | Core power                                                                                                                                                                                                                                                                    |  |  |

| P0-63              | I/O              | 0 to 3.3                      | Smart pins; P58-P63 serve in the boot process, then general purpose after.                                                                                                                                                                                                    |  |  |

| Vxxyy              | -                | 3.3                           | Power for smart pins in groups of 4: Pxx through Pyy                                                                                                                                                                                                                          |  |  |

| хо                 | 0                | -                             | Crystal Output. Provides feedback for an external crystal, or may be left disconnected depending on CLK Register settings. No external resistors or capacitors are required.                                                                                                  |  |  |

| ΧI                 | I                | -                             | Crystal Input. Can be connected to output of crystal/oscillator pack (with XO left disconnected), or to one leg of crystal (with XO connected to the other leg of crystal or resonator) depending on CLK Register settings. No external resistors or capacitors are required. |  |  |

| RESN               | I                | 0                             | Reset (active low). When low, resets the Propeller: all cogs disabled and I/O pins floating. Propeller restarts 3 ms after RESn transitions from low to high. Connect to a resistor to pull up to 3.3 V.                                                                      |  |  |

The Propeller 2's I/O pins (P0-P63) are general purpose; however, some exceptions may apply to certain applications. See <u>General Purpose I/O Pin Exceptions</u> for more information.

## **Hardware Connections**

Parallax offers pre-built P2 boards where vital connections are already made for you. Examples include the P2 Edge Module (#P2-EC) and P2 Mini Breakout Board (#64019) pictured here.

Schematics are available for download from the respective product pages. Visit the <u>Propeller 2 > Hardware</u> section of the Parallax online store for development tools. For additional P2 connection details including boot options, see the P2 Datasheet in the Documentation section.

# **Operation**

There are three states that characterize the Propeller 2 general operation: Boot Up, Runtime, and Shutdown. Each is conceptually distinct, though their behaviors may overlap.

## **Boot Up**

Upon any power-up, reset (RESn) pin low-to-high, or software reset event:

- 1. The Propeller 2 delays for 3 ms, engages the fast clock, then loads up Cog 0 with the ROM-resident Bootloader within 2 ms.

- 2. The Bootloader executes, checks the Boot Pattern on pins P59-P61, and performs the prescribed boot process which may include:

- o interacting with, or receiving a Propeller application from, a host (ex: PC) over serial,

- o fast booting from a connected SPI-based flash chip, or

- o booting from a connected SD card.

|                  | Boot Pattern                                                                                     |   |                                                                                                         |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------|---|---------------------------------------------------------------------------------------------------------|--|--|--|

| Set by           | Set by floating connection 'f', pull-up resistor '⊕', or pull-down resistor ' Don't care is '×'. |   |                                                                                                         |  |  |  |

| P61 <sup>1</sup> | P61 <sup>1</sup> P60 <sup>1</sup> P59 <sup>1</sup> Procedure                                     |   |                                                                                                         |  |  |  |

| f                | f                                                                                                | f | Program from serial within 60 s window                                                                  |  |  |  |

| ×                | ×                                                                                                | Û | Program from serial within 60 s window; no flash or microSD card boot                                   |  |  |  |

| 仓                | ×                                                                                                | f | Program from serial within 100 ms or boot from flash. If fails, program from serial within 60 s window. |  |  |  |

| Û                | ×                                                                                                | Φ | Fast boot from flash; no serial. If it fails, shutdown.                                                 |  |  |  |

| <b>f</b> / ₽     | ੂੰ2                                                                                              | f | Boot from microSD card. If fails, program from serial within 60 s window.                               |  |  |  |

| <b>f</b> / 🕫     | <b>⊕</b> 2                                                                                       | Φ | Boot from microSD card. If it fails, shutdown.                                                          |  |  |  |

<sup>&</sup>lt;sup>1</sup> Development boards with switchable settings may show P61 as "FLASH," P60 omitted, and P59 as " $\Delta$ " and " $\nabla$ "

The following connections must be made when a host system, flash memory and/or microSD Card memory is intended for programming or boot up purposes:

| Host Serial and Boot Memory Connections |          |           |           |           |           |          |

|-----------------------------------------|----------|-----------|-----------|-----------|-----------|----------|

| Туре                                    | P63 (in) | P62 (out) | P61 (out) | P60 (out) | P59 (out) | P58 (in) |

| Host Serial                             | TX (out) | RX (in)   |           |           |           |          |

| Flash SPI                               |          |           | CSn (in)  | CLK (in)  | DI (in)   | DO (out) |

| SD SPI                                  |          |           | CLK (in)  | CSn (in)  | DI (in)   | DO (out) |

#### **Runtime**

In typical operation (above), the Propeller 2 will boot up and run a user's pre-written application in Cog 0. At this point, all further activity is defined by the application where there is complete control over internal clock speed, I/O pin usage and behavior, mix of cogs running, and more. At runtime, Propeller applications have the flexibility to

<sup>&</sup>lt;sup>2</sup> Built into microSD card

execute full-speed at all times or to carefully manage processing speed, system functions, and current consumption dynamically—they can even willfully shut down partially or completely.

If the boot process didn't result in running a user application, the loader may still operate for some time, waiting for host communication. Most boot patterns on pins P59-P61 feature a serial communication window, allowing the boot process to talk to a host computer over pins P62 and P63. This communication window is used to load new applications or to run interactive sessions with the Propeller 2's built-in systems. See <a href="Host Communication">Host Communication</a> for more details.

#### **Shutdown**

Most applications run continuously until power is shut off, though there are cases that are considered to be a *powered shutdown* state. During powered shutdowns, no cogs are running and all I/O pins become high-impedance inputs. Powered shutdown occurs when the power supply remains stable while one of the following happens:

- 1. the RESn pin goes low, or

- 2. the boot process fails to load an application or connect to a host, or

- 3. the user application terminates the last running cog, or

- 4. the user application requests a reboot (momentary shutdown.

A powered shutdown state may last indefinitely in all but the last case. Boot up begins again when the RESn pin transitions from low to high (case 1), when the Propeller 2 is power-cycled (case 2 and #3), or after an application requests reboot (case 4).

If the boot process is about to shut down the Propeller 2, it first switches to the RCSLOW (~20 kHz) clock, then terminates cog 0 (the only cog that was running), for the lowest powered shutdown state. User applications may not switch to the slowest clock source before terminating the last cog, thus they will have a higher powered shutdown current draw.

Note that Smart I/O operates independent of the cogs and continues while its associated DIR bit is high; however, with all the cogs terminated, all I/O pin DIR bits are naturally low (i.e. set to input) which puts every Smart I/O into its reset state.

#### Rebooting

While normally powered, the Propeller 2 reboots if it receives a low pulse on the RESn pin or executes a **HUBSET** #\$1000\_0000 instruction. Both reset methods, external (via RESn pin) and internal (via **HUBSET**), behave the same; however, the internal reset is not detectable externally using the RESn pin.

#### **Shared Resources**

The interaction between each cog and the Hub is vital for sharing resources in the Propeller 2. At any given time, the Hub gives a specific cog momentary exclusive access to certain shared resources such as a region of Hub RAM and system configuration settings. This happens for each cog in a "round robin" fashion—timing is consistent regardless of how many cogs are running. Cogs can choose to use or ignore those resources depending on their current needs; often processing internally (in Cog RAM) in parallel and only accessing exclusive resources in bursts.

There are two types of shared resources in the Propeller 2: 1) common, and 2) exclusive. Common resources can be accessed at any time by any number of cogs; they include Smart I/O Pins, the System Counter, and the Pseudo-Random Number Generator results. Exclusive resources can also be accessed by each cog, but only by one cog at a time; they include Hub RAM, the CORDIC solver, Lock bits and the seeder functionality for the Pseudo-Random Number Generator. The Hub helps govern access to exclusive elements by granting each cog a turn to use it, one at a time, facilitating atomic operations without any contention. For cases involving multiple

elements (ex: a block of Hub RAM locations) where an atomic operation is not intrinsically possible, lock bits can be used to cooperatively share access between cogs. See the <u>Hub</u> section for more information.

# **System Clock**

The System Clock is the central clock source for nearly every component of the Propeller 2. All cogs and I/O pins perform their next step upon the next System Clock's clock edge. The System Clock itself is driven from one of three selectable sources: 1) the Internal RC Oscillator, 2) the Phase-Locked Loop (PLL), or 3) the Crystal Oscillator (an internal circuit that operates an external crystal or receives an external oscillator signal). The PLL uses the Crystal Oscillator as its reference clock input. The System Clock source is selected by the CLK register setting, which is configurable both at compile time and at run time.

The System Clock speed chosen for any Propeller application is of vital importance to timing calculations in code. If coded properly via the clock setting constants (\_clkfreq, \_xinfreq, \_xtlfreq, \_rcslow, or \_rcfast) the compiled clock mode is reflected in clkfreq\_ and clkmode\_. When set via the HUBSET or ASMCLK instructions, the run time CLKFREQ and CLKMODE values reflect the current System Clock speed.

See System Clock Configuration for more information.

# Memory

The Propeller 2 has three memory regions: Register RAM, Lookup RAM, and Hub RAM. Each cog has its own Register RAM and Lookup RAM (collectively called Cog RAM), while the Hub RAM is shared by all cogs.

| Propeller 2 (P2X8C4M64P) RAM Memory Configuration |         |         |                        |                                             |                              |

|---------------------------------------------------|---------|---------|------------------------|---------------------------------------------|------------------------------|

| Region                                            | Depth   | Width   | Address Range<br>(Hex) | PASM Instruction D/S<br>Address Range (Hex) | PC<br>Increment <sup>1</sup> |

| Cog "Register" RAM                                | 512     | 32 bits | \$00000\$001FF         | \$000\$1FF                                  | 1                            |

| Cog "Lookup" RAM                                  | 512     | 32 bits | \$00200\$003FF         | \$000\$1FF                                  | 1                            |

| Hub RAM                                           | 524,288 | 8 bits  | \$00400\$7FFFF         | \$00000\$7FFFF                              | 4                            |

<sup>&</sup>lt;sup>1</sup> PC is the Program Counter for PASM execution; incrementing relative to width to retrieve 32-bit instructions.

# **COGS (PROCESSORS)**

The Propeller 2 contains eight (8) processors, called cogs, numbered 0 to 7. Each cog contains the same components, including a Processor block, Cog RAM, Event Tracker, Cog Attention strobes, Streamer, Colorspace Converter, Pixel Mixer, DAC Channels, an I/O Output Register, and an I/O Direction Register. Each cog is designed exactly the same and can run tasks independently from the others.

All eight cogs are driven from the same clock source, the <u>System Clock</u>, so they each maintain the same time reference and all active cogs execute instructions simultaneously. They also all have access to the same <u>shared resources</u>, like I/O pins, Hub RAM, the System Counter, and CORDIC math solver.

Cogs can be started and stopped at-will, performing independent or cooperative tasks simultaneously. Regardless of the nature of their use, the Propeller application developer has full control over how and when each cog is employed; there is no compiler-driven or operating system-driven splitting of tasks between multiple cogs. This empowers the developer to deliver absolutely deterministic timing, power consumption, and response to the embedded application.

# **Cog Memory**

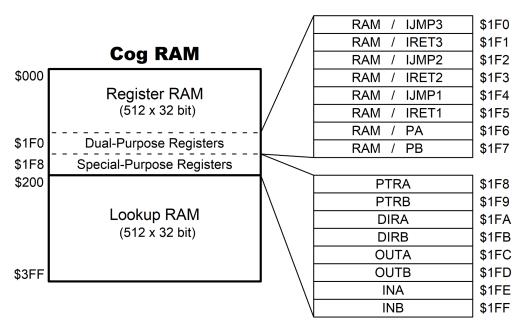

Each cog has its own internal RAM that it uses to execute code and to store and manipulate data independent of every other cog. This internal RAM is organized into two contiguous blocks of 512 longs (512 x 32), called Register RAM and Lookup RAM, each with special attributes. See RAM Memory Configuration.

Note that \$1FE (INA) and \$1FF (INB) are also the debug interrupt call address and return address, respectively.

#### Register RAM

Each cog's primary 512 x 32-bit dual-port Register RAM (Reg RAM for short) provides for code execution, fast direct register access, and special use. It is read and written as longs (4 bytes) and contains general purpose, dual-purpose, and special-purpose registers.

#### **General Purpose Registers**

Register RAM locations \$000 through \$1EF are general-purpose registers for code and data usage.

#### **Dual-Purpose Registers**

Register RAM locations \$1F0 through \$1F7 may either be used as general-purpose registers, or may be used as special-purpose registers if their associated functions are enabled.

| Address                                            | Name                                                                                   | Purpose                                                                                                                                                                                               |

|----------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$1F0<br>\$1F1<br>\$1F2<br>\$1F3<br>\$1F4<br>\$1F5 | RAM / IJMP3<br>RAM / IRET3<br>RAM / IJMP2<br>RAM / IRET2<br>RAM / IJMP1<br>RAM / IRET1 | Interrupt call address for INT3 Interrupt return address for INT3 Interrupt call address for INT2 Interrupt return address for INT2 Interrupt call address for INT1 Interrupt return address for INT1 |

| \$1F6<br>\$1F7                                     | RAM / PA<br>RAM / PB                                                                   | CALLD-imm return, CALLPA parameter, or LOC address CALLD-imm return, CALLPB parameter, or LOC address                                                                                                 |

#### **Special-Purpose Registers**

RAM registers \$1F8 through \$1FF give mapped access to eight special-purpose functions. In general, when specifying an address between \$1F8 and \$1FF, the PASM2 instruction accesses a special-purpose register, not just the underlying RAM.

| Address | Name             | Purpose                   |

|---------|------------------|---------------------------|

| \$1F8   | PTRA             | Pointer A to Hub RAM      |

| \$1F9   | PTRB             | Pointer B to Hub RAM      |

| \$1FA   | DIRA             | Output enables for P31P0  |

| \$1FB   | DIRB             | Output enables for P63P32 |

| \$1FC   | OUTA             | Output states for P31P0   |

| \$1FD   | OUTB             | Output states for P63P32  |

| \$1FE   | INA <sup>1</sup> | Input states for P31P0    |

| \$1FF   | INB <sup>2</sup> | Input states for P63P32   |

<sup>&</sup>lt;sup>1</sup>Also debug interrupt call address

## Lookup RAM

Each cog's secondary 512 x 32-bit dual-port Lookup RAM (LUT RAM for short) is read and written as longs (4 bytes). It is useful for:

- Scratch space

- Streamer access

- Bytecode execution lookup table

- Smart pin data source

- Paired-Cog communication mechanism

- Code execution

#### **Scratch Space**

In contrast to Register RAM, the cog cannot directly reference Lookup RAM locations in the majority of its PASM instructions. Instead, the desired location(s) must be read or written between Lookup RAM and Register RAM using the RDLUT and WRLUT instructions, respectively. This is synonymous with other hardware architecture's scratch storage using "LOAD" and "STORE" instructions. When using the RDLUT and WRLUT instructions, the Lookup RAM's locations \$200..\$3FF are addressable as \$000..\$1FF.

#### **Paired-Cog Communication Mechanism**

Adjacent cogs whose ID numbers differ by only the LSB (cogs 0 and 1, 2 and 3, etc.) can each allow their Lookup RAMs to be written by the other cog via its local Lookup RAM writes. This allows adjacent cogs to share data very quickly through their Lookup RAMs.

Warning: Lookup RAM writes from the adjacent cog are implemented on the Lookup RAM's 2nd port. The 2nd port is also shared by the streamer in DDS/LUT modes. If an external write occurs on the same clock as a streamer read, the external write gets priority. It is not intended that external writes would be enabled at the same time the streamer is in DDS/LUT mode.

To use this feature, start two adjacent cogs using a special mechanism of the COGINIT instruction, enable the feature with the SETLUTS instruction, and if needed, facilitate handshaking between cogs using the SETSE1..4 instructions.

<sup>&</sup>lt;sup>2</sup>Also debug interrupt return address

# **Instruction Pipeline**

To optimize execution speed, cogs employ a pipelined execution architecture for PASM2. The nature of the pipeline is summarized by these attributes:

- There are five stages of processing per instruction, performed in a minimum of five clock cycles

- Instructions are overlapped to effectively execute in as little as two clock cycles when the pipeline is full

- Branch instructions cause the pipeline to be flushed; the first instruction following the branch will take at least five clock cycles (13 or 14 if branching to a hub address) since the pipeline is refilling

- Any instruction that is conditionally cancelled will not execute but will still take effectively two clocks (or at least five clocks, if following a branch) to pass through the pipeline

- If an instruction must wait for a resource, all the following instructions in the pipeline also wait

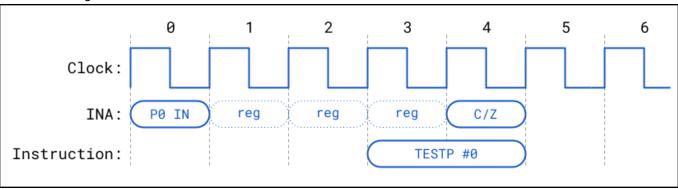

## Instruction Stages

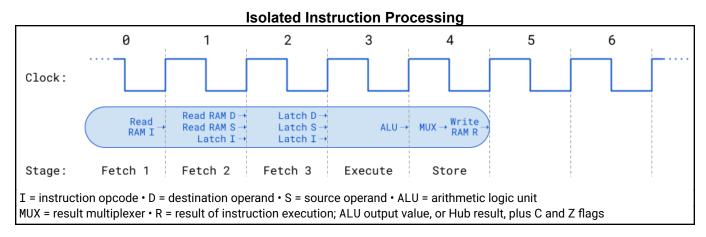

To understand the pipeline, first consider the process of executing a single PASM2 instruction. An instruction's five stages of processing are illustrated below. Every PASM2 instruction is processed this way—five stages taking at least five clock cycles total. Each stage is completed upon the rising edge of the following clock signal.

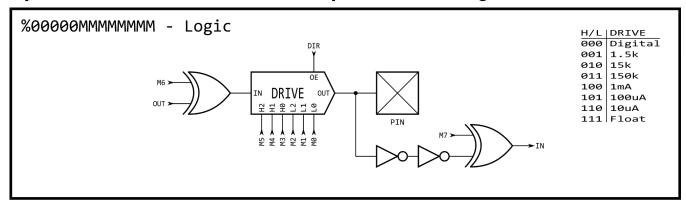

The first three stages (Fetches) involve reading the 32-bit PASM2 instruction (I) opcode from RAM, latching (saving) the instruction opcode for decoding, and reading/latching the instruction's source (S) and destination (D) values (32-bits each). The final two stages (Execute and Store) perform the instruction's intent by using the arithmetic logic unit (ALU) and writing the resulting 32-bit value and the carry and zero flags if required. At that point (five clock cycles in this case) the instruction is fully executed.

- The MUX gathers all possible results (from the ALU, Hub RAM, etc.) and delivers only what is appropriate for the Write RAM R operation

- The final result value is written and the carry and zero flags are either written or discarded, depending on the specific instruction and given effects (WC / WZ / WCZ)

- As needed for proper processing, an instruction may wait (one or more extra clock cycles are inserted, without any stage advancement) immediately before the final stage

## **Pipeline**

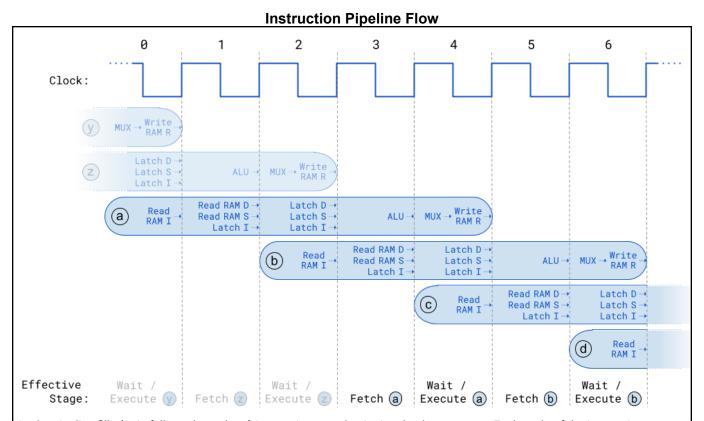

In the pipeline, instructions are overlapped by three stages, resulting in an effective two-stage execution per instruction known as Fetch and Execute (or Wait). Compare the single instruction illustration above with the multi-instruction pipeline flow below— the instruction above appears in the next illustration with the prefix "a" while others use prefixes "b", "c", etc. This seven-cycle slice of time is processing six contiguous instructions.

As the pipeline fills (or is full, as shown here) instructions overlap in time by three stages. Each cycle of the instruction pipeline simultaneously processes different stages of two or three contiguous instructions. Here, instruction a is read (in the first cycle) at the same moment its two previous instructions (y and z) write results and latch for later ALU operation, respectively.

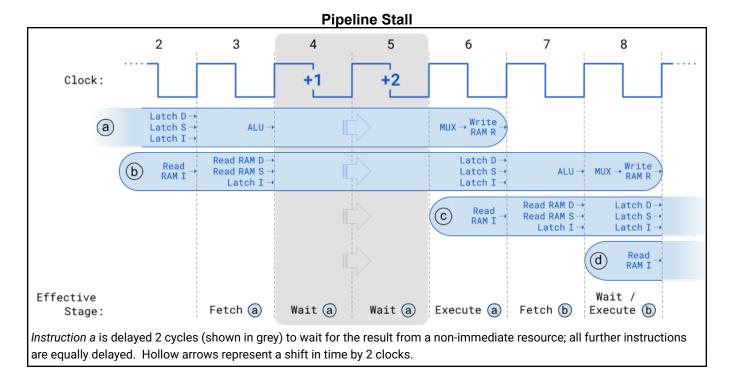

## Wait (Pipeline Stall)

When an instruction requires a resource that is not yet available (such as Hub RAM), the whole pipeline delays for additional cycles ahead of the instruction's execute stage. These extra cycles align the target instruction's MUX-update to the delayed resource's moment-of-result while performing no operation in any other instruction. When the resource is ready, processing continues again for all instructions in the pipeline. For example, if instruction a needs to wait 2 extra cycles to execute properly, the pipeline flow (above) would be stretched starting at cycle 4; appearing like this:

Instead of Execute a in cycle 4, two Wait cycles occur, delaying the Write operation (until the MUX has valid results) as well as the latching and reading operations of instructions b, c, and d.

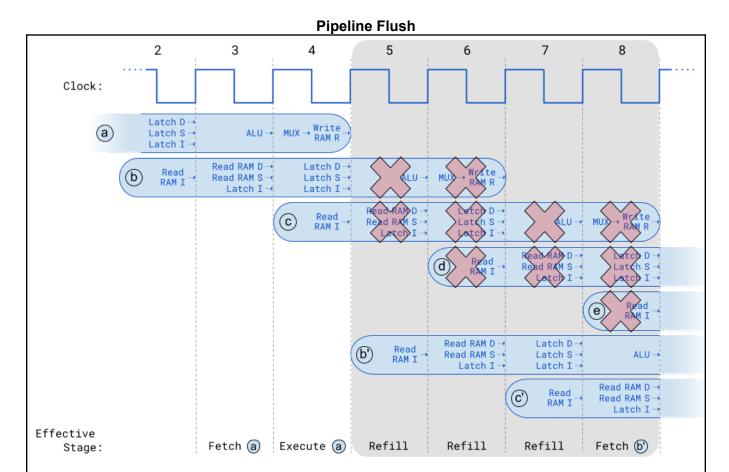

## **Branch (Pipeline Flush)**

Branch instructions potentially change the path of code execution. A "branch" instruction may be one of a few static operations (such as JMP or CALL) or among many dynamic operations (such as a conditionally-executed JMP or CALL, or a modify/test-and-branch instruction like DJZ or TJNZ). When processing a branch instruction, one of two things will happen.

- 1. Branch not taken? Execution continues as normal with the instruction following the branch instruction

- 2. Branch is taken? Execution is diverted (the program counter is immediately changed to point to the branch's target destination), all remaining instruction stages are flushed from the pipeline, and new instructions from the destination begin to refill the pipeline

Due to the pipeline flush and the need to refill it, the instruction following an executed branch will take at least five clock cycles to execute (13 or 14 if branching to a hub address).

In the illustration below, instruction a is a "branch taken." Immediately after the Execute a stage — all remaining stages from the next four contiguous instructions are flushed (each marked by a red 'X') and new instructions refill those empty pipeline positions.

Instruction a is an executed branch— changing the program counter at the end of cycle 4, flushing further instruction stages from the pipeline (shown in grey), and refilling the pipeline with instructions from the new (branched to) location. Instructions b through e (which physically followed instruction a) are effectively "cancelled" from the pipeline and replaced by instructions b' and c' from the new code location.

## **Execution**

Cogs use 20-bit addresses for their program counters (PC); the upper bit is a "don't care" bit - this affords an execution space of up to 512 KB. Depending on the value of a cog's PC, an instruction will be fetched from either its Register RAM, its Lookup RAM, or the Hub RAM. See RAM Memory Configuration.

#### Register Execution

When the PC is in the range of \$00000 to \$001FF, the cog fetches instructions from Cog Register RAM. This is referred to as "cog execution mode." There are no special considerations when branching to a cog register address.

## **Lookup Execution**

When the PC is in the range of \$00200 to \$003FF, the cog fetches instructions from Cog Lookup RAM. This is referred to as "lut execution mode." There are no special considerations when branching to a cog lookup address.

#### **Hub Execution**

When the PC is in the range of \$00400 to \$7FFFF, the cog fetches instructions from Hub RAM. This is referred to as "hub execution mode." Special considerations are involved with hub execution.

- The PC rolling beyond \$003FF will not initiate hub execution (it will just wrap back to \$00000); a branch must occur to get from register or lookup execution to hub execution.

- 2. Branching to a hub address takes a minimum of 13 clock cycles. If the instruction being branched to is not long-aligned, one additional clock cycle is required.

3. When executing from Hub RAM, the cog employs the FIFO hardware to spool up instructions so that a stream of instructions will be available for continuous execution. This means the FIFO cannot be used for anything else. So, during hub execution these instructions cannot be used:

RDFAST / WRFAST / FBLOCK

RFBYTE / RFWORD / RFLONG / RFVAR / RFVARS

WFBYTE / WFWORD / WFLONG

XINIT / XZERO / XCONT - when the streamer mode engages the FIFO

It is not possible to execute code from hub addresses \$00000 through \$003FF, as the cog will instead read instructions from the cog's Register RAM or Lookup RAM as indicated above.

# **Starting And Stopping Cogs**

Any cog can start or stop any other cog, or restart or stop itself. Each cog has a unique ID which can be used to start or stop it. It is also possible to start free (stopped or never started) cogs, without needing to know their IDs. This way, applications can simply start free cogs, as needed, and as those cogs retire by stopping themselves or getting stopped by others, they return to the pool of free cogs to become available again for restarting.

To start a free cog:

COGINIT id, addr WC '(id=\$30) start a free cog at addr, C=0 and id=Cog ID if okay

To (re)start a specific cog:

COGINIT #1, #\$100 load and start cog 1 from hub address \$100

To start a cog, passing in a pointer or 32-bit value:

SETQ ptra\_val 'ptra\_val will go into target cog's PTRA register

COGINIT #%0\_1\_0000, addr load and start a free cog at addr

To retrieve this cog's ID:

COGID myID 'my cog ID is written to myID

To stop this cog:

COGID myID 'get my ID COGSTOP myID 'halt myself

# Cog Attention

Each cog can request the attention of other cogs by using the **COGATN** instruction. One or more of the D operand's lower 8 bits may be set high (1) to signal the corresponding cog or cogs.

COGATN #00001100 'Get attention of cogs 2 and 3

For each high bit, the matching cog sees an *attention* event for **POLLATN / WAITATN / JATN / JNATN** and for interrupt use. The attention strobe outputs from all cogs are OR'd together to form a composite set of 8 strobes from which each cog receives its particular strobe.

Examples:

| POLLATN | WC   | 'has attention been requested?           |

|---------|------|------------------------------------------|

| WAITATN |      | 'wait for attention request              |

| JATN    | addr | 'jump to addr if attention requested     |

| JNATN   | addr | 'iump to addr if attention not requested |

In the intended use case, the cog receiving an attention request knows which other cog is strobing it and how to respond. In cases where multiple cogs may request the attention of a single cog, some messaging structure may need to be implemented in Hub RAM to differentiate requests.

# **System Counter**

The System Counter (CT) is a 64-bit free-running counter that increments upon every clock cycle. It is a shared resource, accessible by all cogs at any time, serving as the official time reference for many instructions and events. It is often used for brief, relative time measurements; however, since it is cleared to zero upon every power-up/reset, it is also a *system up time* reference.

To read the current System Counter value:

|    | GETCT        | Χ |    | 'read lower 32-bits of system counter into X register |

|----|--------------|---|----|-------------------------------------------------------|

| or |              |   |    |                                                       |

|    | GETCT        | Χ | WC | 'read upper 32-bits of system counter into X register |

|    | <b>GETCT</b> | Υ |    | 'read lower 32-bits of system counter into Y register |

Note: to get the full 64-bit System Counter value, it is important to read the upper 32-bits first (as shown above) and immediately read the lower 32-bits second. This sequence employs a special mechanism that avoids phase issues; CT's lower 32-bits are returned exactly as they were back at the moment in which the upper 32-bits had been read.

For event handling, there are three hidden registers dedicated to System Counter timing and events: CT1, CT2, and CT3. These represent a target moment in time (future CT value), settable via the ADDCTx instructions and used (read) internally by many event instructions.

To mark a moment in time to wait for, use GETCT with ADDCTx (1, 2, or 3) and WAITCTx (1, 2, or 3):

| GETCT   | X      | 'get current CT                     |

|---------|--------|-------------------------------------|

| ADDCT1  | x,#500 | 'make target CT1 (500 cycles later) |

| WAITCT1 |        | 'wait for CT to pass CT1 target     |

This can easily be extended to create a 500-cycle activity-loop instead.

The event-timing instructions that utilize the System Counter are: ADDCTx, POLLCTx, WAITCTx, JCTx, and JNCTx. In addition, by using a SETQ right before any WAITxxx instruction, a *timeout* is created to abort the *wait* in case the target event never arrives.

# **Pseudo-Random Number Generator**

The Propeller 2 features a pseudo-random number generator (PRNG) based on the Xoroshiro128\*\* algorithm. Note that the "\*\*" is part of the name, indicating the exact variation of the Xoroshiro128 algorithm used.

The Xoroshiro128\*\* PRNG iterates on every clock cycle, generating 64 fresh bits which get spread among all cogs and smart pins. From this 64-bit pool, upon every clock cycle, each cog receives a unique set of 32 different bits

(in a scrambled arrangement with some bits inverted) and each smart pin receives a similarly-unique set of 8 different bits. Cogs can read their current 32-bit *pseudo-random* value using the **GETRND** instruction and directly apply them using the **BITRND** and **DRVRND** instructions. Smart pins utilize their 8 bits as noise sources for DAC dithering and noise output.

After reset, the bootloader seeds the Xoroshiro128\*\* PRNG fifty times, each time with 31 bits of thermal noise gleaned from pin 63 while in ADC calibration mode. This establishes a very random seed which the PRNG iterates from, thereafter. There is no need to do this again, but here is how you would do it if 'x' contained a seed value:

SETB x,#31 'set the MSB of x to make a PRNG seed command HUBSET x 'seed 32 bits of the Xoroshiro128\*\* state

Note: using HUBSET, with D's MSB set, will seed the 128-bit PRNG. This will write all bits of D into 32 bits of the PRNG, affecting 1/4th of its total state. The required high MSB bit in D ensures that the overall state will not go to zero. Because the PRNG's 128 state bits rotate, shift, and XOR against each other, they are thoroughly spread around within a few clocks, so seeding from a fixed set of 32 bits should not pose a limitation on seeding quality.

Note there is also another pseudo-random number feature, accessed via the X0R032 instruction; however it doesn't use the X0roshiro128\*\* PRNG— instead, it iterates a register value to make a relatively good PRNG sequence under software control.

## HUB

While common shared resources, such as I/O Pins, are simultaneously accessible by every cog, exclusive shared resources, such as an individual Hub RAM location, can not be simultaneously accessed without causing problems. The Hub governs access to exclusive resources, giving each cog a turn to safely perform an atomic operation on that resource. On the Propeller 2 (P2X8C4M64P), a given cog receives such access once every eight clock cycles. This moment of access is known as the Hub Access Window.

Atomic operations are elemental in nature (indivisible); each performed in one step with guaranteed isolation from other operations happening at the same time. In any given Hub Access Window, a cog can perform a single atomic operation on a single entity, such as writing a value to one Hub RAM location or setting the system clock speed.

The time-sliced nature of the Hub Access Window applies to every exclusive resource and results in a kind of speed limit for accessing them— each cog must wait its turn among the collective of cogs. Luckily, there are some natural use cases where the Propeller 2 provides optimized access as well; namely, sequential location access of Hub RAM and successive CORDIC math engine use.

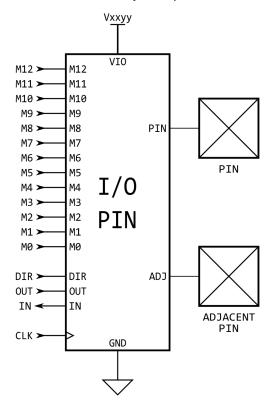

#### Hub RAM

Hub RAM consists of long elements (32-bits wide) that can be read and written as bytes, words, and longs, in little-endian format. Each cog has access to the entire Hub RAM, though any given RAM location must be used in an orderly, time-sliced fashion. Hub addresses are always byte-oriented and there are no special alignment rules for words and longs in Hub RAM. Cogs can read and write bytes, words, and longs at any hub address, as well as execute instruction longs from any hub address starting at \$400 (see <a href="Hub Execution"><u>Hub Execution</u></a>).

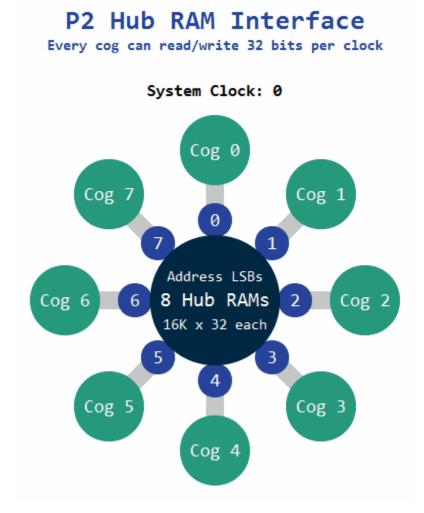

On the Propeller 2 (P2X8C4M64P), the Hub RAM is split into eight slices that are multiplexed among all cogs. Each RAM slice holds every 8th long of the composite Hub RAM. Upon every clock cycle, each cog can access the *next* RAM slice, allowing all cogs simultaneous access to some part of Hub RAM. The Hub RAM Interface diagram illustrates this process conceptually as the collective of RAM slices rotates around, each facing a new cog every clock cycle.

For any target Hub RAM location, the lower 3 bits of its address determines the slice ID (0 through 7) that it resides within. If that slice doesn't happen to be aligned with the cog at the moment it is executing the memory read/write instruction (RDxxxx / WRxxxx), the cog will automatically wait for that slice to come around.

#### Random Access

Random accesses of Hub RAM (i.e. using non-contiguous locations) must always align to the Hub Access Window of the RAM slice in question. This means each individual random access (RDxxxx / WRxxxx instruction) may take as many as 16 clock cycles to complete. It is safe for any number of cogs to begin a random access read or write operation on any clock cycle— the Hub will automatically delay each of them individually until they line up with their target addresses' Hub Access Window.

#### **Sequential Access**

By default, sequential access of Hub RAM operates the same as with random access; however, when using either the cog's Hub FIFO interface or fast block move feature, subsequent addresses in the series are available immediately when called for.

Each cog has a Hub FIFO interface which can be set for Hub-RAM-read or Hub-RAM-write operation. This interface allows the cog to either sequentially read or sequentially write the Hub RAM in units of bytes, words, or longs, at any rate up to full speed; one long (32-bits) per clock. Regardless of the transfer frequency or the word size, the FIFO will ensure that the cog's reads or writes are all properly conducted from/to the composite Hub RAM.

Fast block moves can also read/write a sequential series of values (longs only) at one per clock cycle. Either the cog's Reg RAM or LUT RAM may be used as the destination/source. This is achieved by preceding a RDLONG /

**WRLONG / WMLONG** instruction with a **SETQ** or **SETQ2** instruction to specify the number of longs to move using Reg RAM or LUT RAM, respectively.

#### Protected RAM

Upon startup/reset, the internal 16 KB ROM contents are copied to the last 16 KB of Hub RAM to bring that code image into addressable memory space. At that point, the ROM code image is accessible in Hub RAM at \$7C000-\$7FFFF and also outside the 512 KB range, at \$FC000-\$FFFFF. It is readable and writable in both locations (changes in one also appear in the other), though it can be write-protected using the HUBSET instruction. When write-protection is enabled, the image in RAM at \$7C000-\$7FFFF is hidden (becomes all zeros) and is in-tact but read-only for the running user application in the range \$FC000-\$FFFFF. The debug mechanism (code that runs during a debug interrupt) uses this area to perform its tasks and is the only code that can continue to read and write that memory despite the engaged write-protection.

# **System Clock Configuration**

The system clock is the time base for all internal components and can be configured for several modes.

- Direct from internal slow clock (RCSLOW); a ~20 kHz oscillator is intended for low-power operation

- Direct from internal fast clock (RCFAST); a 20 MHz+ oscillator designed for minimum 20 MHz operation

- Direct from XI pin; driven externally via a clock oscillator or a crystal oscillator (w/crystal-feedback on XO)

- Enhanced from XI pin; driven externally via a clock oscillator or a crystal oscillator (w/crystal-feedback on XO) and the XI signal internally modified by the PLL (phase-locked loop), often to accelerate the frequency

If the XI and XO pins (eXternal Input/Output) are used for clocking via an attached 10 – 20 MHz crystal oscillator, internal loading caps can also be enabled on XI and XO for crystal impedance matching.

If the XI pin is used as a clock input or crystal oscillator input, its frequency can be modified through the internal phase-locked loop (PLL). The PLL divides the XI pin frequency from 1 to 64, then multiplies the resulting frequency from 1 to 1024 in the voltage-controlled oscillator (VCO). The VCO frequency can either be used directly (i.e. divided by 1) or divided down by any *even* value from 2 to 30 to get the final PLL clock frequency which becomes the system clock frequency.

The system clock is configured by the running Propeller 2 application using the HUBSET instruction in the following format. The four LSBs are all that are needed to switch among clock sources and select all but the PLL settings.

HUBSET ##%0000\_000E\_DDDD\_DDMM\_MMMM\_PPPP\_CCSS 'set clock mode

The bit fields (E, D, M, P, C, and S) are described in the following tables.

| PLL Setting | Value | Effect                           | Notes                                                                                                                                                                                                                                                                    |

|-------------|-------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| %E          | 0/1   | PLL off/on                       | XI input must be enabled by %CC. Allow 10 ms for crystal+PLL to stabilize before switching over to PLL clock source.                                                                                                                                                     |

| %DDDDDD     | 063   | 164 division of XI pin frequency | This divided XI frequency feeds into the phase-frequency comparator's 'reference' input.                                                                                                                                                                                 |

| %МММММММММ  | 01023 | 11024 division of VCO frequency  | This divided VCO frequency feeds into the phase-frequency comparator's 'feedback' input. This frequency division has the effect of <i>multiplying</i> the divided XI frequency (per %DDDDDD) inside the VCO. The VCO frequency should be kept within 100 MHz to 350 MHz. |

| %PPPP | 0  | VCO / 2<br>VCO / 4 | This divided VCO frequency is selectable as the system clock when SS = %11. |

|-------|----|--------------------|-----------------------------------------------------------------------------|

|       | 2  | VCO / 6            | GIOCK WHICH GG = 7011.                                                      |

|       | 3  | VCO / 8            |                                                                             |

|       | 4  | VCO / 10           |                                                                             |

|       | 5  | VCO / 12           |                                                                             |

|       | 6  | VCO / 14           |                                                                             |

|       | 7  | VCO / 16           |                                                                             |

|       | 8  | VCO / 18           |                                                                             |

|       | 9  | VCO / 20           |                                                                             |

|       | 10 | VCO / 22           |                                                                             |

|       | 11 | VCO / 24           |                                                                             |

|       | 12 | VCO / 26           |                                                                             |

|       | 13 | VCO / 28           |                                                                             |

|       | 14 | VCO / 30           |                                                                             |

|       | 15 | VCO / 1            |                                                                             |

| %CC | XI status | XO status     | XI / XO impedance | XI / XO loading caps |

|-----|-----------|---------------|-------------------|----------------------|

| %00 | ignored   | float         | Hi-Z              | OFF                  |

| %01 | input     | 600-ohm drive | 1M-ohm            | OFF                  |

| %10 | input     | 600-ohm drive | 1M-ohm            | 15pF per pin         |

| %11 | input     | 600-ohm drive | 1M-ohm            | 30pF per pin         |

| %SS | Clock Source | Notes                                                                              |  |

|-----|--------------|------------------------------------------------------------------------------------|--|

| %11 | PLL          | CC != %00 and E=1, allow 10ms for crystal+PLL to stabilize before switching to PLL |  |

| %10 | XI           | CC != %00, allow 5ms for crystal to stabilize before switching to XI pin           |  |

| %01 | RCSLOW       | ~20 kHz, can be switched to at any time, low-power                                 |  |

| %00 | RCFAST       | 20 MHz+1, can be switched to at any time, used on boot up                          |  |

<sup>&</sup>lt;sup>1</sup> Designed to run a least 20 MHz, worst case, to accommodate 2 MBaud serial loading during boot

**WARNING**: Incorrectly switching away from the PLL setting (%SS = %11) can cause a glitch which will hang the clock circuit. To safely switch, always start by switching to an internal oscillator using either **HUBSET** #\$F0 (for RCFAST) or **HUBSET** #\$F1 (for RCSLOW).

#### **PLL Example**

The PLL divides the XI pin frequency from 1 to 64, then multiplies the resulting frequency from 1 to 1024 in the VCO. The VCO frequency can be used directly, or divided by 2, 4, 6, ...30, to get the final PLL clock frequency which can be used as the system clock.

The PLL's VCO is designed to run between 100 MHz and 200 MHz and should be kept within that range.

$$VCO = \frac{Freq(XI) \times (\%MMMMMMMMMM + 1)}{(\%DDDDDD + 1)}$$

$$PLL = if(\%PPPP = 15) \Rightarrow VCO$$

$$PLL = if(\%PPPP \neq 15) \Rightarrow \frac{VCO}{(\%PPPP + 1) \times 2}$$

Let's say you have a 20 MHz crystal attached to XI and XO and you want to run the Prop2 at 148.5 MHz. You could divide the crystal by 40 (%DDDDDD = 39) to get a 500 kHz reference, then multiply that by 297 (%MMMMMMMMM = 296) in the VCO to get 148.5 MHz. You would set %PPPP to %1111 to use the VCO output directly. The configuration value would be %1\_100111\_0100101000\_1111\_10\_11. The last two 2-bit fields select 15 pf crystal mode and the PLL. In order to realize this clock setting, though, it must be done over a few

steps:

```

HUBSET #$F0 'set 20 MHz+ (RCFAST) mode

HUBSET ##%1_100111_0100101000_1111_10_00 'enable crystal+PLL, stay in RCFAST mode

WAITX ##20_000_000/100 'wait ~10ms for crystal+PLL to stabilize

HUBSET ##%1_100111_0100101000_1111_10_11 'now switch to PLL running at 148.5 MHz

```

The clock selector controlled by the %SS bits has a deglitching circuit which waits for a positive edge on the old clock source before disengaging, holding its output high, and then waiting for a positive edge on the new clock source before switching over to it. It is necessary to select mode %00 or %01 while waiting for the crystal and/or PLL to settle into operation, before switching over to either.

# Locks (Semaphores)

For application-defined cog coordination, the hub provides a pool of 16 semaphore bits, called locks. Cogs may use locks, for example, to manage exclusive access of a resource or to represent an exclusive state, shared among multiple cogs. What a lock represents is completely up to the application using it; they are a means of allowing one cog at a time the exclusive status of 'owner' of a particular lock ID. In order to be useful, all participant cogs must agree on a lock's ID and what purpose it serves.

The LOCK instructions are:

```

LOCKNEW D {WC}

LOCKTRY {#}D {WC}

LOCKTRY {#}D {WC}

```

#### Lock Usage

In order to use a lock, one cog must first allocate a lock from the lock pool with LOCKNEW and communicate that lock's ID with other cooperative cogs. If successful, LOCKNEW returns the lock ID in D and, if WC is given, will clear C (0) if a lock was available or set C (1) if all locks were already allocated. A cog may allocate more than one lock if needed.

Cooperative cogs then use **LOCKTRY** to *take* ownership of the state which that lock represents. The Hub arbitrates lock ownership in a round-robin fashion (as with all exclusive resources) so any cog waiting to take ownership of a lock will get its fair turn and only one will be awarded ownership at any given time. Here's an example of looping until ownership of a lock is successful:

```

'Keep trying to capture lock until successful

.try LOCKTRY write_lock WC

IF_NC JMP #.try

```

Once lock ownership is successful, the cog should perform the task the lock was designed to protect while all other cogs in this cooperative arrangement should be busy with other tasks or waiting for lock ownership approval in a loop similar to the above. It is recommended that lock-protected steps be intentionally swift so as not to hold up other cogs waiting for ownership to perform their lock-protected counter steps.

After the designated task is performed, the cog must immediately use **LOCKREL** to *release* ownership of the lock; allowing other cogs potential ownership of the lock. Only the cog that has taken ownership of the lock can

release it; however, a lock will also be implicitly released if the cog that's holding ownership is stopped (COGSTOP), restarted (COGINIT), or if LOCKRET is executed for that lock.

If the lock is no longer needed by the application (i.e. no cogs need it for the designed purpose), it may be returned to the unallocated lock pool by executing **LOCKRET**. Any cog can return a lock, even if it wasn't the cog that allocated it with **LOCKNEW**.

## **CORDIC Solver**

The Hub contains a 54-stage pipelined CORDIC solver (Coordinate Rotation Digital Computer) that can compute the following functions for all cogs:

- Multiply: 32 x 32 unsigned multiply with 64-bit product

- Divide: 64 / 32 unsigned divide with 32-bit quotient and 32-bit remainder

- Square Root: root of 64-bit unsigned value with 32-bit result

- Rotation: 32-bit signed (X, Y) rotation around (0, 0) by a 32-bit angle with 32-bit signed (X, Y) results

- Cartesian to Polar: 32-bit signed (X, Y) to 32-bit (length, angle) cartesian to polar operation

- Polar to Cartesian: 32-bit (length, angle) to 32-bit signed (X, Y) polar to cartesian operation

- Integer to Logarithm: 32-bit unsigned integer to 5:27-bit logarithm

- Logarithm to Integer: 5:27-bit logarithm to 32-bit unsigned integer

Each cog can issue one CORDIC instruction per its hub access window (which occurs once every eight clocks) and retrieve the result 55 clocks later via the GETQX and GETQY instructions. For faster throughput, cogs can take advantage of the hub access window and CORDIC pipeline relationship to issue a stream of CORDIC instructions interleaved with retrieving corresponding results, achieving up to one CORDIC result every eight clocks. Each cog's active CORDIC instructions and forthcoming results are completely isolated from each other, as well as from other cogs; however, each result must be retrieved on time or else it will be overwritten by the following result, if any.

## Multiply

Use the QMUL instruction to multiply two unsigned 32-bit numbers together and retrieve the CORDIC result with the GETQX and GETQY instructions (for lower and upper long, respectively). QMUL will wait for the hub access window and GETQX / GETQY will wait for the CORDIC results.

```

QMUL D/#,S/# - Multiply D by S

```

To get the results (these instructions wait for the CORDIC results):

```

GETQX lower_long

GETQY upper_long

```

#### Divide

Use the QDIV or QFRAC instruction (either with optional preceding SETQ instruction) to divide a 64-bit numerator by a 32-bit denominator, then retrieve the CORDIC results with the GETQX and GETQY instructions (for quotient and remainder, respectively). QDIV / QFRAC will wait for the hub access window and GETQX / GETQY will wait for the CORDIC results.

```

QDIV D/#,S,# - Divide {$00000000:D} by S

...or...

SETQ Q/# - Set top part of numerator

QDIV D/#,S,# - Divide {Q:D} by S

...or...

QFRAC D/#,S,# - Divide {D:$00000000} by S

...or...

```

```

SETQ Q/# - Set bottom part of numerator QFRAC D/#,S,# - Divide {D:Q} by S

```

...and to get the results:

```

GETQX quotient

GETQY remainder

```

## **Square Root**

Use the QSQRT instruction on a 64-bit number and retrieve the square root CORDIC result with the GETQX instruction. QSQRT will wait for the hub access window and GETQX will wait for the CORDIC results.

```

QSQRT D/#,S,# - Compute square root of {S:D} GETQX root

```

#### Rotation