Name:

ID

Quiz 9 key

- a) What is the machine code (in HEX) of the blez instruction in the following code:

Test: addi \$2 \$0 5

syscall

add \$9 \$9 \$2

addi \$6 \$6 4

lw \$16 (\$6)

blez \$16 Test

# Given that the blez opcode is 6.

The immediate is the offset which is -6 ( in 16 bits binary: Binary 1111 1111 1111 1010 )

000110 10000 00000 1111 1111 1111 1010

0x1A00FFFA

- b) What is the machine code for: L1: j L2, given that the opcode is 2 and L1, L2 addresses are 0x2023078C , 0x20003204

Write L2 in Binary: 0010 0000 0000 0000 0011 0010 0000 0100

Then remove the 2 from right and 4 from left to get your 26 bits to use in the machine code.

The 26 bits are:

0000 0000 0000 0011 0010 0000 01

Add to the left yjr 6 bits op code:

000010 0000 0000 0000 0011 0010 0000 01

Organize by 4 bits (to get the HEX)

0000 1000 0000 0000 0000 1100 1000 0001

0x08000C81

a) The following questions are related to the register file:

- If the output ports are implemented using decoders and tri-state buffers:

- What is the required decoder size? **5x32**

- How many decoders are needed? **2**

- How many **total** tri-state buffers are required? **64**

- If the output ports are implemented using multiplexers:

- How many multiplexers are required? **2**

- What is the size (input vs. output configuration) of each multiplexer? **32x1**

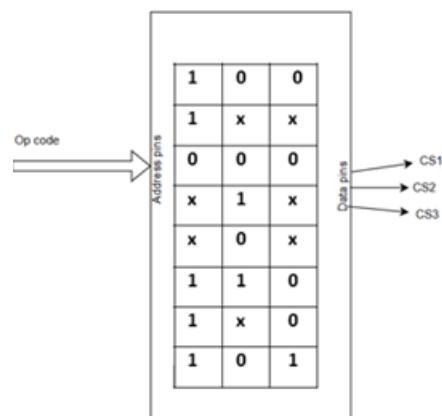

b) If another processor (not related to the above one) has the following truth table for 3 of its control signals (namely: CS1, CS2, CS3). Sketch a complete circuit that can generate the three control signals.

| Op code<br>In decimal | CS1 | CS2 | CS3 |

|-----------------------|-----|-----|-----|

| 0                     | 1   | 0   | 0   |

| 1                     | 1   | x   | x   |

| 2                     | 0   | 0   | 0   |

| 3                     | x   | 1   | x   |

| 4                     | x   | 0   | x   |

| 5                     | 1   | 1   | 0   |

| 6                     | 1   | x   | 0   |

| 7                     | 1   | 0   | 1   |

One Solution: use ROM of min size of **8x3**

Store the Truth table in the ROM

Connect the op code to the address pins

The control signal are connected to the data pins

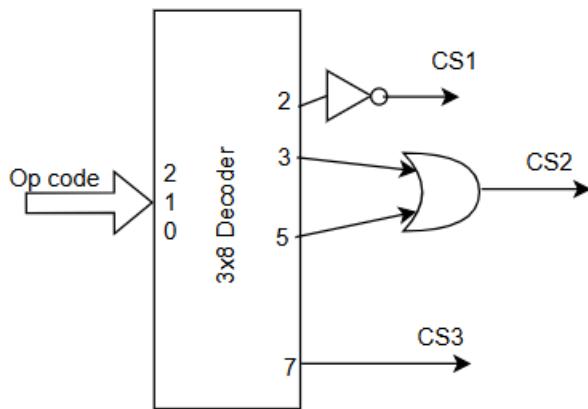

Another Solution: use **3x8 decoder**

c) For a MIPS single cycle circuit discussed in the class, it is executing the following instruction:

lw \$16 20(\$24) which has the following machine code: 0x8F100014.

Assume that every register has a value = its number x 1000 ( For example, register 16 has 16000).

Also assume that the data memory is filled with all 1s (every byte of the memory =0xFF)

Answer the following questions:

- What is the value coming out of BUSA : **2400**

- What is the value coming of BUSB: **1600**

- What is the output of the extender **20**

- What is the output of the ALU **2420**

- What is the value of RW **16**

- What is the value of BUSW **-1**