Главное управление образования Гродненского облисполкома

Управление профессионального образования и профориентации ГУО «Гродненский областной институт развития образования»

Учреждение образования «Гродненский государственный колледж техники, технологий и дизайна»

## АРИФМЕТИКО-ЛОГИЧЕСКИЕ ОСНОВЫ ВЫЧИСЛТЕЛЬНОЙ ТЕХНИКИ

Лабораторный практикум

**Специальность:** 2-40 01 01 Программное обеспечение информационных технологий

## СОДЕРЖАНИЕ

| АННОТАЦИЯ                                                       | 3          |  |  |  |  |  |

|-----------------------------------------------------------------|------------|--|--|--|--|--|

| ОСНОВНЫЕ ПОНЯТИЯ И ОПРЕДЕЛЕНИЯ                                  | 5          |  |  |  |  |  |

| ТРЕБОВАНИЯ ПО ОХРАНЕ ТРУДА ПРИ ПРОВЕДЕНИИ                       | 8          |  |  |  |  |  |

| ЛАБОРАТОРНЫХ РАБОТ                                              |            |  |  |  |  |  |

| ЛАБОРАТОРНАЯ РАБОТА №1. Исследование работы дешифратора         | 13         |  |  |  |  |  |

| экспериментальным путем                                         |            |  |  |  |  |  |

| ЛАБОРАТОРНАЯ РАБОТА №2. Исследование работы мультиплексора      | 23         |  |  |  |  |  |

| экспериментальным путем                                         |            |  |  |  |  |  |

| ЛАБОРАТОРНАЯ РАБОТА №3. Исследование работы сумматоров          | 27         |  |  |  |  |  |

| экспериментальным путем                                         |            |  |  |  |  |  |

| ЛАБОРАТОРНАЯ РАБОТА №4. Исследование работы триггеров           | 32         |  |  |  |  |  |

| экспериментальным путем                                         | J <b>_</b> |  |  |  |  |  |

| ЛАБОРАТОРНАЯ РАБОТА №5. Исследование работы регистра            | 38         |  |  |  |  |  |

| экспериментальным путем                                         | 50         |  |  |  |  |  |

| ЛАБОРАТОРНАЯ РАБОТА №6. Исследование работы счетчиков           | 46         |  |  |  |  |  |

| экспериментальным путем                                         | 70         |  |  |  |  |  |

| ЛАБОРАТОРНАЯ РАБОТА №7. Исследование работы АЛУ                 | 52         |  |  |  |  |  |

| экспериментальным путем                                         | 32         |  |  |  |  |  |

| ЛАБОРАТОРНАЯ РАБОТА №8. Исследование работы ячейки памяти       | 66         |  |  |  |  |  |

| •                                                               | 00         |  |  |  |  |  |

| статического ОЗУ экспериментальным путем                        | 75         |  |  |  |  |  |

| ЛАБОРАТОРНАЯ РАБОТА №9. Разработка и отладка программы с        | 13         |  |  |  |  |  |

| использованием различных форматов команд и методов адресации.   |            |  |  |  |  |  |

| Исследование командного цикла МП при выполнении команд с        |            |  |  |  |  |  |

| различными форматами и методами адресации                       | 00         |  |  |  |  |  |

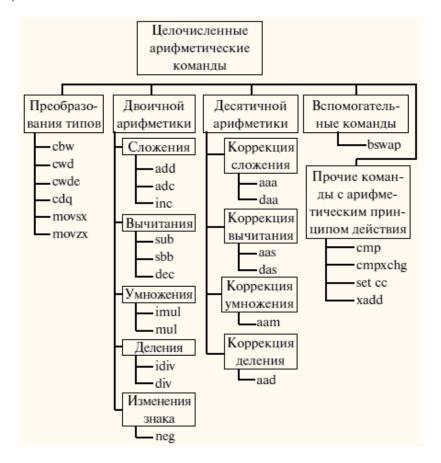

| ЛАБОРАТОРНАЯ РАБОТА №10. Разработка и отладка программы с       | 89         |  |  |  |  |  |

| использованием арифметических команд. Исследование командного   |            |  |  |  |  |  |

| цикла МП при выполнении арифметических команд                   | 0.0        |  |  |  |  |  |

| ЛАБОРАТОРНАЯ РАБОТА №11. Разработка и отладка программы с       | 99         |  |  |  |  |  |

| использованием команд пересылки и сравнения кодов. Исследование |            |  |  |  |  |  |

| командного цикла МП при выполнении команд пересылки и сравнения |            |  |  |  |  |  |

| кодов                                                           |            |  |  |  |  |  |

| ЛАБОРАТОРНАЯ РАБОТА №12. Разработка и отладка программы с       | 112        |  |  |  |  |  |

| использованием команд переходов. Исследование командного цикла  |            |  |  |  |  |  |

| МП при выполнении команд переходов                              |            |  |  |  |  |  |

| ЛАБОРАТОРНАЯ РАБОТА №13. Изучение возможностей системы          | 121        |  |  |  |  |  |

| команд МП для разработки циклической программы                  |            |  |  |  |  |  |

| ЛАБОРАТОРНАЯ РАБОТА №14. Изучение возможностей системы          | 125        |  |  |  |  |  |

| команд МП для разработки программы с использованием подпрограмм |            |  |  |  |  |  |

| и стека                                                         |            |  |  |  |  |  |

| СПИСОК ЛИТЕРАТУРЫ                                               | 132        |  |  |  |  |  |

### **АННОТАЦИЯ**

В современном мире вычислительная техника занимает ведущую роль в различных сферах человеческой деятельности: производстве, транспорте, логистике, образовании и медицине. Умение пользоваться вычислительной техникой становится базовым, а вместе с тем возрастает важность знаний об устройстве вычислительных систем и их компонентах.

В рамках изучения учебного предмета «Арифметико-логические основы вычислительной техники» формируется понимание основополагающих вопросов построения вычислительных систем, предусматривается изучение принципов организации вычислительного процесса, конструктивных особенностей, технических и эксплуатационных характеристик современных вычислительных средств.

Предмет посвящён изучению арифметических основ вычислительной техники, алгебры логики, схемотехники ПК.

Цель изучения — освоение учащимися следующих областей знаний: арифметических основ вычислительной техники на основе двоичной арифметики; логических основ вычислительной техники на базе изучения алгебры логики; схемотехнических основ и архитектурной организации ПК.

В ходе выполнения лабораторных работ по учебному предмету «Арифметико-логические основы вычислительной техники» рассматриваются следующие вопросы:

арифметические и логические основы вычислительной техники;

принципы построения и функционирования устройств вычислительной техники;

функциональный состав и основы организации микропроцессора; система команд управления работой микропроцессора; организация и методы адресации памяти;

взаимодействие аппаратного и программного обеспечения вычислительной техники;

перевод чисел из одной системы счисления в другую и арифметические действия в различных системах счисления;

представление чисел в машинном формате;

оптимизация логических выражений и синтез логических схем;

анализ принципов работы элементов, узлов и устройств вычислительной техники;

приемы составления команды и программного кода на машинно-ориентированном языке программирования.

Лабораторные работы служат связующим звеном между теорией и практикой. Они помогают углубить и закрепить теоретические знания, изучить на практике схемы работы логических устройств.

Лабораторный практикум по предмету «Арифметико-логические основы вычислительной техники» разработан с учетом специфики подготовки учащихся в рамках среднего специального образования по специальности: 2-40 01 01 Программное обеспечение информационных технологий, квалификация специалиста: техник-программист.

При проведении лабораторных работ учащиеся соблюдают установленные правила безопасности. В начале занятия преподаватель сообщает тему и цель работы. Учащиеся в ходе занятия повторяют и закрепляют ранее полученные теоретические знания, выполняют различные задания, формирующие умения практического характера. Преподаватель контролирует ход работы, отвечает на вопросы учащихся и при необходимости корректирует возникающие ошибки. В конце работы учащихся отвечают на контрольные вопросы. В данных вопросах выделены основные аспекты рассматриваемой темы, которые должны быть усвоены учащимся.

В заключительной части выполнения лабораторных работ составляется отчет. Окончательное оформление отчета становится домашним заданием учащихся.

#### ОСНОВНЫЕ ПОНЯТИЯ И ОПРЕДЕЛЕНИЯ

**Арифметико** – **логическое устройство** (**АЛУ**) – блок процессора, предназначенный для выполнения логических и математических операций над двоичными числами.

**Демультиплексор (DMX или DMS)** – комбинационное устройство, преобразующее последовательный сигнал в параллельный и выполняющее функцию, обратную мультиплексору.

**Дешифратор (DC)** – комбинационное устройство, позволяющее распознавать числа, представленные позиционным n-разрядным кодом.

**Единая система конструкторской документации (системаЕСКД)** – комплекс межгосударственных стандартов, устанавливающих взаимосвязанные правила, требования и нормы по разработке, оформлению и обращению конструкторской документации, разрабатываемой и применяемой на всех стадиях жизненного цикла изделия.

**Команда** – это код, определяющий операцию вычислительной машины и данные, участвующие в операции.

**Командный цикл** – интервал, на протяжении которого осуществляется одно обращение микропроцессора к памяти или к внешнему устройству.

**Компаратор** – логическое устройство с двумя входами, на которые подаются два разных двоичных слова равной в битах длины, и тремя двоичными выходами, на которые выдается признак сравнения входных слов (первое слово меньше второго, больше второго или слова равны).

**Логический элемент** — это простейшая структурная единица, выполняющая определённые логические операции над двоичными переменными.

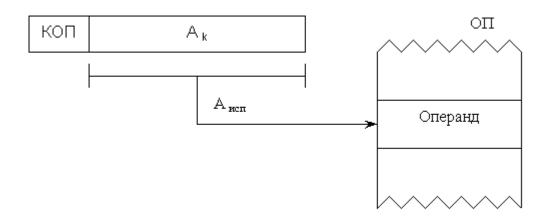

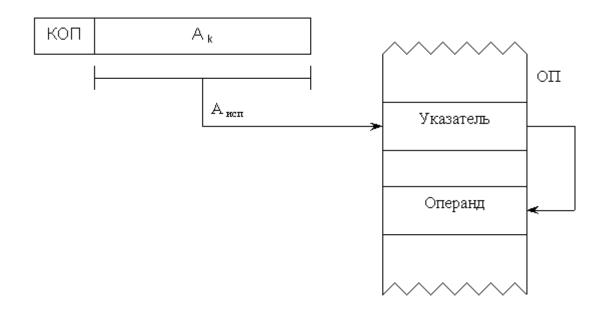

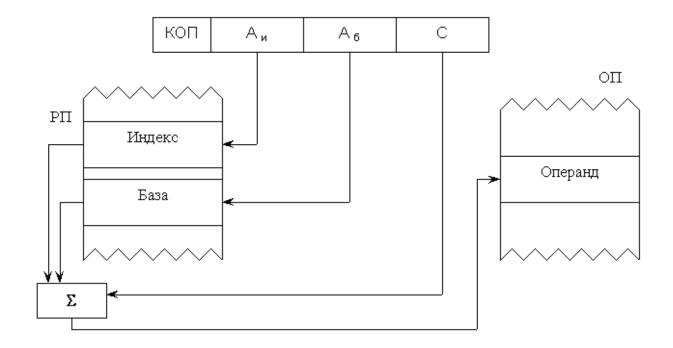

**Метод адресации** – способы указания на определённую ячейку (ячейки) памяти <u>ЭВМ</u> процессору с целью записи, чтения данных или передачи управления.

**Микропроцессор (МП)** – процессор (устройство, отвечающее за выполнение арифметических, логических операций и операций управления, записанных в

машинном коде), реализованный в виде одной микросхемы или комплекта из нескольких специализированных микросхем.

**Мультиплексор** (**MUX или MS**) – комбинационное устройство, обеспечивающее передачу в желаемом порядке цифровой информации, поступающей по нескольким входам на один выход.

**Оперативные запоминающие устройства (ОЗУ или RAM)** – память с произвольной выборкой, которая служит для хранения выполняемой программы и оперативных данных.

**Подпрограмма** именованная или иным образом идентифицированная часть компьютерной программы, содержащая описание определённого набора действий.

**Полусумматор** — логическое комбинационное устройство, имеющее два входа и два выхода. Позволяет вычислять сумму A+B, где A и B —это разряды (биты) обычно двоичного числа, при этом результатом будут два бита S и C, где S — это бит суммы по модулю 2, а C — битпереноса.

**Постоянные запоминающие устройства (ПЗУ или ROM)** –устройства, предназначенные для хранения постоянных данных и служебных программ.

**Регистр** – последовательное устройство, предназначенное для приема, хранения и преобразования двоичной информации.

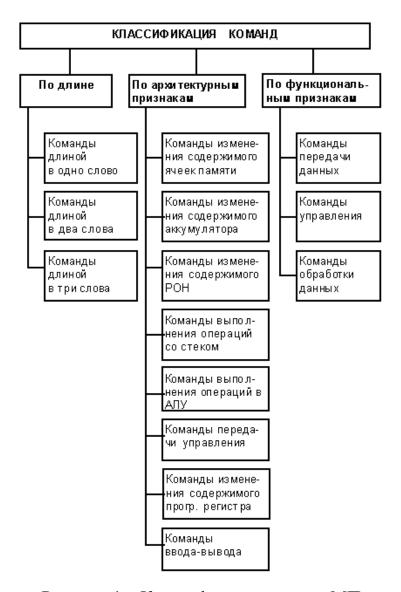

**Система команд** — это строго заданный конечный набор команд, которые может выполнить исполнитель.

**Система счисления** — символический метод записи чисел, представление чисел с помощью письменных знаков.

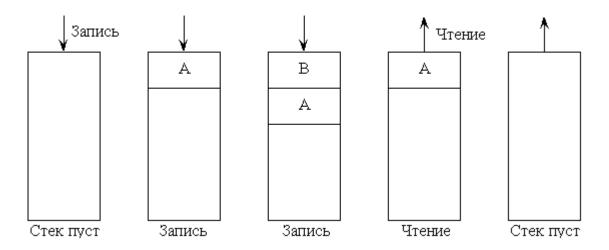

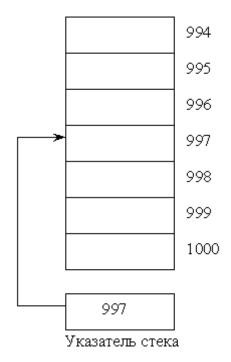

Стек – абстрактный тип данных, представляющий собой список элементов, организованных по принципу LIFO (англ. lastin – firstout, «последним пришёл – первым вышел»).

**Структура команды** – этологическое понятие, которое определяется составом, назначением и расположением полей в команде.

**Сумматор** – логическое комбинационное устройство, предназначенное для выполнения операции арифметического сложения чисел, представленных в виде двоичных кодов.

**Счетчик** — последовательное цифровое устройство, предназначенное для счета входных импульсов, фиксации их числа в двоичном коде и выполнения микрооперации счета по изменению значения числа в счетчике на единицу.

**Триггер** — устройством, которое находится в одном из двух устойчивых состояний и скачкообразно переходит из одного состояния в другое под воздействием внешнего управляющего сигнала.

**Условно графическое обозначение (УГО)** – аббревиатура условного графического обозначения на принципиальной электрической схеме.

**Формат команд** — это структура команды с разметкой номеров разрядов (битов), определяющих границы отдельных полей команды, или с указанием числа битов в определенных полях.

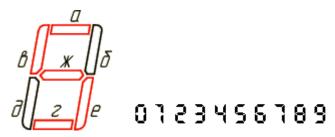

**Шифратор** (**CD**) – комбинационное устройство, выполняющее функции, обратные дешифратору.

## ТРЕБОВАНИЯ ПО ОХРАНЕ ТРУДА ПРИ ПРОВЕДЕНИИ ЛАБОРАТОРНЫХ РАБОТ

При работе в учебном кабинете обучающиеся должны неукоснительно соблюдать правила внутреннего распорядка для обучающихся учреждений образования.

При разработке правил безопасного поведения при организации образовательного процесса по учебному предмету «Арифметико-логические основы вычислительной техники» определяются правила безопасного поведения при работе с видеотерминалом, персональной электронно-вычислительной машиной.

К работе в компьютерном классе допускаются обучающиеся, ознакомленные с правилами безопасного поведения в компьютерном классе и не имеющие противопоказаний по состоянию здоровья.

При работе в компьютерном классе обучающиеся должны соблюдать правила поведения, расписание учебных занятий, установленные режимы труда и отдыха.

работе В компьютерном классе возможно воздействие обучающихся следующих опасных и вредных производственных факторов: неблагоприятное воздействие на организм человека неонизирующих электромагнитных излучений видеотерминалов; неблагоприятное воздействие зрение визуальных эргономических параметров видеотерминалов, на выходящих за пределы оптимального диапазона; неправильный подбор размеров ученической мебели; недостаточная освещенность в компьютерном классе; поражение электрическим при неисправном ТОКОМ электрооборудовании кабинета.

При работе в компьютерном классе педагогическому работнику и обучающимся необходимо соблюдать правила пожарной безопасности, знать места расположения первичных средств пожаротушения. Компьютерный класс должен быть оснащен углекислотным огнетушителем.

При неисправности оборудования обучающимся необходимо прекратить работу и сообщить об этом педагогическому работнику.

В процессе работы с видеотерминалами обучающиеся должны соблюдать порядок проведения работ, правила личной гигиены, содержать в чистоте рабочий стол.

Обучающимся не разрешается самостоятельно включать компьютеры или запускать компьютерные программы, трогать разъемы соединительных кабелей.

Работа в компьютерном классе разрешается только в присутствии педагогического работника. Перед началом работы педагогический работник должен:

- включить полностью освещение в кабинете, убедиться в исправной работе светильников. Уровень искусственной освещенности от системы общего освещения должен составлять не менее 400 люкс;

- убедиться в исправности электрооборудования кабинета: светильники должны быть надежно подвешены к потолку и иметь светорассеивающую арматуру; коммутационные коробки должны быть закрыты крышками; корпуса и крышки выключат елей и розеток не должны иметь трещин и сколов, а также оголенных контактов;

- убедиться в правильной расстановке мебели в компьютерном классе: расстояние между рабочими столами с видеомониторами (в направлении тыла поверхности одного видеомонитора и экрана другого видеомонитора) должно быть не менее 2,0м, а расстояние между боковыми поверхностями видеомониторов не менее 1,2 м;

- тщательно проветрить компьютерный класс и убедиться, что вне зависимости от периода года температура воздуха в пределах +19 +21 °C, относительная влажность воздуха 30–60 процентов, скорость движения воздуха не более 0,1 м/с;

- убедиться в наличии защитного заземления оборудования, а также защитных экранов видеотерминалов; включить персональный компьютер

(далее – ПК) и проверить стабильность и четкость изображения на экранах. Изображение на экранах видеотерминалов должно быть стабильным, ясным и предельно четким, не иметь мерцаний символов и фона, на экранах не должно быть бликов и отражений светильников, окон и окружающих предметов.

#### Обучающийся должен:

- осмотреть и привести в порядок рабочий стол, освободить его от посторонних предметов;

- проверить правильность установки стола, стула, положения оборудования, угла наклона экрана, положения клавиатуры;

- при нарушении целостности корпуса компьютера, монитора, клавиатуры, мыши, любой неисправности оборудования сообщить педагогическому работнику.

Во время работы недопустимы занятия за одним видеотерминалом двух и более человек.

Меловая доска, как правило, в компьютерном классе для написания информации не используется.

Все используемые в компьютерном классе демонстрационные электрические приборы должны быть исправными и иметь заземление или зануление.

Обучающимся не допускается:

- включать ПК без разрешения педагогического работника;

- дотрагиваться до экрана монитора и вращать монитор;

- работать с ПК при снятом корпусе;

- во избежание внутреннего перегрева и выхода ПК из строя закрывать во время работы вентиляционные отверстия посторонними предметами или чехлами;

- вскрывать корпус монитора, системного блока;

- разбирать монитор, системный блок, клавиатуру, мышь;

- переключать силовые питающие кабели проводов связи с периферийными устройствами на задней крышке корпуса системного блока и монитора,

- отключать штепсельные разъемы, переключать разъемы интерфейсных кабелей периферийных устройств при включенном питании;

- производить отключение питания во время выполнения активной задачи;

- оказывать механические усилия (наступать ногами, дергать силовые питающие кабели и тянуть за провода связи с периферийными устройствами);

- ударять по клавишам клавиатуры;

- прикасаться к задней панели системного блока;

- допускать попадание влаги на поверхность системного блока, монитора, клавиатуры;

- загромождать верхние панели устройств бумагами и посторонними предметами;

- передвигать столы с оборудованием, переставлять оборудование на столах.

При поражении электрическим током обучающегося или при получении им травмы педагогический работник должен немедленно полностью отключить от питающей сети ПК (в случае поражения электрическим током), оказать первую помощь пострадавшему, вызвать медицинского работника учреждения образования или скорую медицинскую помощь по телефону 103, сообщить о несчастном случае руководителю учреждения общего среднего образования.

При возникновении пожара педагогический работник должен немедленно эвакуировать обучающихся из здания, сообщить о пожаре по телефону101, администрации учреждения образования и приступить к тушению очага возгорания с помощью первичных средств пожаротушения.

Обучающийся должен:

- в случае появления неисправности в работе ПК выключить его и сообщить об этом педагогическому работнику;

- при ухудшении самочувствия, появлении головной боли, головокружения прекратить работу и сообщить об этом педагогическому работнику;

- при возникновении нестандартной ситуации сохранять спокойствие и неукоснительно выполнять указания педагогического работника.

По окончании работы с разрешения педагогического работника обучающиеся должны закрыть активные задачи, выключить ПК и привести в порядок рабочий стол.

Педагогический работник должен тщательно проветрить учебный кабинет, закрыть окна, фрамуги, выключить свет.

#### РАЗДЕЛ V. Комбинационные цифровые устройства

# **Тема 5.1. Дешифраторы и шифраторы ЛАБОРАТОРНАЯ РАБОТА №1**

#### Исследование работы дешифратора экспериментальным путем

**Цель:** Изучить принципы работы шифратора и дешифратора. Научиться строить таблицу истинности и схему устройства.

#### Порядок выполнения

- 1. Изучить теоретическую часть

- 2. Выполнить практическое задание

- 3. Ответить на контрольные вопросы

- 4. Оформить отчет по проделанной работе

#### Теоретическая часть

**Шифраторы и дешифраторы** являются примерами простейших преобразователей кодов.

**Дешифратор (decoder)** – это комбинационное устройство, позволяющее распознавать числа, представленные позиционным п-разрядным кодом.

Если на входе дешифратора "- разрядный двоичный код, то на его выходе код "1 из N". В кодовой комбинации этого кода только одна позиция занята единицей, а все остальные — нулевые. Например, код "1 из N", содержащий 4 кодовые комбинации, будет представлен следующим образом:

| 1 | 0 | 0 | 0 |

|---|---|---|---|

| 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 0 | 0 | 1 |

Такой код называют **унитарным,** поэтому дешифратор является преобразователем позиционного двоичного кода в унитарный. Так как возможное количество чисел, закодированных n-разрядным двоичным кодом,

равно количеству наборов из и аргументов (N=2"), то дешифратор, имеющий n входов, должен иметь 2n выходов. Такой дешифратор называют полным. Если часть входных наборов не используется, то дешифратор называют неполным, и у него число выходов меньше 2n. Таким образом, в зависимости от входного двоичного кода на выходе дешифратора возбуждается только одна из выходных цепей, по номеру которой можно распознать входное число.

Дешифраторы применяют для расшифровки адресов ячеек запоминающих устройств, высвечивания букв и цифр на мониторах, индикаторах и других устройствах.

Проиллюстрируем синтез дешифраторов на примере полного дешифратора трёхразрядных чисел. Таблица истинности дешифратора (таблица 1) представляет ряд единиц, расположенных по диагонали таблицы, а в остальных клетках которой стоят нули.

Таблица 1

| No | 😉 Входы Выходы |   |    |   |   |   |   |   |   |   |   |

|----|----------------|---|----|---|---|---|---|---|---|---|---|

|    | X              | X | X1 | Y | Y | Y | Y | Y | Y | Y | Y |

|    | 3              | 2 |    | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 0  | 0              | 0 | 0  | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1  | 0              | 0 | 1  | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 2  | 0              | 1 | 0  | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 3  | 0              | 1 | 1  | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 4  | 1              | 0 | 0  | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 5  | 1              | 0 | 1  | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 6  | 1              | 1 | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 7  | 1              | 1 | 1  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

Выходы дешифратора имеют нумерацию, совпадающую с десятичным представлением двоичного числа от 0 до  $2^n$  - 1. Если, например, двоичное число на входе имеет код 101 (табл. 1), то единичный сигнал будет только на

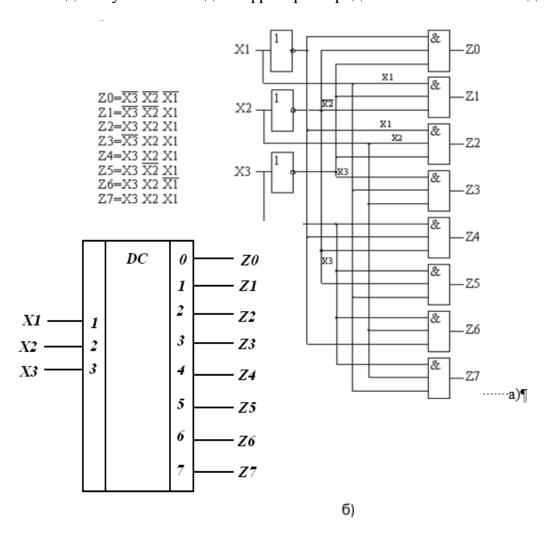

пятом выходе дешифратора, т.е. Z5=1, а на остальных выходах будут нули. Работа этого дешифратора описывается восемью логическими функциями. Составленные по единицам они имеют вид:

$$Z_0 = \overline{X3}\overline{X2}\overline{X1};$$

$Z_2 = \overline{X3}X2\overline{X1};$   $Z_4 = X3\overline{X2}\overline{X1};$   $Z_6 = X3X2\overline{X1};$   $Z_1 = \overline{X3}\overline{X2}X1;$   $Z_3 = \overline{X3}X2X1;$   $Z_5 = X3\overline{X2}X1;$   $Z_7 = X3X2X1.$

Каждая из функций представляет конъюнкцию трёх переменных, а значит, может быть реализована на трехвходовых схемах И. Число элементов одноступенчатого дешифратора определяется числом выходов.

Рисунок 1. а – принципиальная схема линейного дешифратора, б – условное графическое обозначение дешифратора

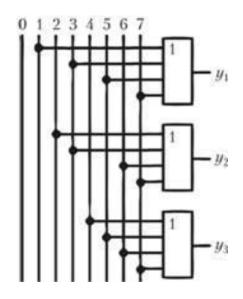

**Шифратор** — это логическое устройство, выполняющее преобразование позиционного кода в n разрядный двоичный код.

Таким образом, шифратор – это комбинационное устройство, реализующее обратную дешифратору функцию.

Полный двоичный шифратор имеет  $2^n$  входов и n выходов.

Шифратор **n-m** — это преобразователь унитарного кода «1 из n» в двоичный (параллельный) код, у которых число выходов m однозначно связано с числом входов n как  $2^m$ . При n = $2^m$  используется полный набор выходных двоичных комбинаций  $Y_i$ . Такой шифратор называется *полным*. Например, шифратор 8-3 полный, т.к. он реализует полный набор возможных комбинаций переменных  $X_i$ (n=8) в полный выходной набор  $Y_i$ (m=3) как  $2^3$ =8.

Таблица истинности полного шифратора 8-3

| Числ |   | Входы |   |   |   |   |   |   |   | ыход | Ю |

|------|---|-------|---|---|---|---|---|---|---|------|---|

| О    | X | X     | X | X | X | X | X | X | Y | Y    | Y |

|      | 0 | 1     | 2 | 3 | 4 | 5 | 6 | 7 | 2 | 1    | 0 |

| 0    | 1 | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 |

| 1    | 0 | 1     | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 1 |

| 2    | 0 | 0     | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1    | 0 |

| 3    | 0 | 0     | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1    | 1 |

| 4    | 0 | 0     | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0    | 0 |

| 5    | 0 | 0     | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0    | 1 |

| 6    | 0 | 0     | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1    | 0 |

| 7    | 0 | 0     | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1    | 1 |

$$Y_0 = X_1 + X_3 + X_5 + X_7 = \overline{\overline{X}_1 \overline{X}_3 \overline{X}_5 \overline{X}_7}$$

$$Y_1 = X_2 + X_3 + X_6 + X_7 = \overline{\overline{X}_2 \overline{X}_3 \overline{X}_6 \overline{X}_7}$$

$$Y_2 = X_4 + X_5 + X_6 + X_7 = \overline{\overline{X}_4 \overline{X}_5 \overline{X}_6 \overline{X}_7}$$

Рисунок 2 – Схема полного линейного шифратора 8-3 на элементах ИЛИ;

Рисунок 3 – УГО шифратора 10-4

Одно из основных применений шифратора — ввод данных с клавиатуры, при котором нажатие любой клавиши с десятичной цифрой должно приводить к передаче в устройство двоичного кода данной цифры. В этом случае нужен неполный шифратор с десятью входами и четырьмя выходами (10-4).

Таблица функционирования шифратора 10-4 имеет вид:

| Входы Х:         | Выходы       |    |    |    |  |

|------------------|--------------|----|----|----|--|

| десятичное число | Двоичный код |    |    |    |  |

|                  | Y3           | Y2 | Y1 | Y0 |  |

| X0: 0            | 0            | 0  | 0  | 0  |  |

| X1: 1            | 0            | 0  | 0  | 1  |  |

| X2: 2            | 0            | 0  | 1  | 0  |  |

| X3: 3            | 0            | 0  | 1  | 1  |  |

| X4: 4            | 0            | 1  | 0  | 0  |  |

| X5: 5            | 0            | 1  | 0  | 1  |  |

| X6: 6            | 0            | 1  | 1  | 0  |  |

| X7: 7            | 0            | 1  | 1  | 1  |  |

| X8: 8            | 1            | 0  | 0  | 0  |  |

| X9: 9            | 1            | 0  | 0  | 1  |  |

Из таблицы следует, что

$$Y0 = X1 \lor X3 \lor X5 \lor X7 \lor X9;$$

$$YI = X2 \lor X3 \lor X6 \lor X7;$$

$$Y2 = X4 \lor X5 \lor X6X7;$$

$$Y3 = X8 \lor X9$$

Для реализации шифратора на элементах И-НЕ необходимо выражения преобразовать по теореме де Моргана:

$$Y0 = \overline{X1 \lor X3 \lor X5 \lor X7 \lor X9} = \overline{X1X3X5X7X9};$$

$$YI = \overline{X2 \vee X3 \vee X6 \vee X7} = \overline{X2}\overline{X3}\overline{X6}\overline{X7};$$

$$Y2 = \overline{X4 \lor X5 \lor X6 \lor X7} = \overline{X4}\overline{X5}\overline{X6}\overline{X7};$$

$$Y3 = \overline{\overline{X8 \vee X9}} = \overline{\overline{X8}\overline{X9}};$$

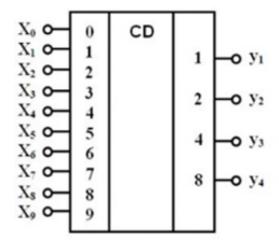

**Преобразователи кодов** – устройства, предназначенные для преобразования одного кода в другой, при этом часто они выполняют нестандартные преобразования кодов. Преобразователи кодов обозначают через X/Y.

Наиболее широко преобразователи кодов известны применительно к цифровым индикаторам. Например, преобразователь 4-х разрядного позиционного двоичного кода в десятичные цифры. Имеется семи сегментный индикатор и с его помощью требуется высветить десять цифр.

#### Семисегментный индикатор

Имеется семь элементов (а-ж), расположенных так, как показано на рисунке. Каждый элемент может светиться либо не светиться, в зависимости от значения соответствующей логической переменной, управляющей его свечением. Вызывая свечение элементов в определенных комбинациях, можно получить изображение десятичных цифр 0-9.

Очевидно, что двоичный код должен иметь не менее 4-х разрядов ( $2^4 = 16$ , что больше 10). Составим таблицу истинности работы такого преобразователя:

|       | Д     | во                       | ИЧ          | Н   |     | ہر ا |     |     |     |     |   |

|-------|-------|--------------------------|-------------|-----|-----|------|-----|-----|-----|-----|---|

|       | ы     | йн                       | <b>(O</b> I | I   | a   | б    | В   | Г   | Д   | e   | Ж |

| Цифра |       | ый код<br>x4 x3<br>x2 x1 |             | (y1 | (y2 | (y3  | (y4 | (y5 | (y6 | (y7 |   |

|       |       |                          |             | )   | )   | )    | )   | )   | )   | )   |   |

|       | $X^2$ |                          |             |     |     |      |     |     |     |     |   |

| 0     | 0     | 0                        | 0           | 0   | 1   | 1    | 1   | 1   | 1   | 1   | 0 |

| 1     | 0     | 0                        | 0           | 1   | 0   | 1    | 1   | 0   | 0   | 0   | 0 |

| 2 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 3 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 4 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 5 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 6 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 7 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 8 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

При построении таблицы были приняты следующие условия: если элемент индикатора светится, то это означает, что он находится в состоянии лог. 1, если погашен, то он находится в состоянии лог. 0.

Управление элементом осуществляется таким образом, что высокий уровень лог. 1 на некотором входе индикатора вызывает гашение соответствующего элемента. Например, для высвечивания цифры 0 необходимо погасить 7-й элемент (у7=0), оставив остальные элементы в состоянии свечения.

По таблице истинности составим систему собственных функций для всех выходов, т.е. СДНФ, минимизируем её и получим логические выражения для выходных величин у1-у7:

$$w1 = \overline{x1} \cdot \overline{x2} \cdot x3$$

$$w2 = x1 \cdot \overline{x2} \cdot \overline{x3} \cdot \overline{x4}$$

$$w3 = \overline{x1} \cdot x2 \cdot x3$$

$$w4 = x1 \cdot \overline{x2} \cdot x3$$

$$w5 = \overline{x1} \cdot x2 \cdot \overline{x3}$$

$$w6 = x1 \cdot x2 \cdot x3$$

$$w7 = x1 \cdot x2 \cdot x3$$

$$w8 = x1 \cdot x2$$

$$w9 = \overline{x1} \bullet \overline{x2} \bullet \overline{x3}$$

$$y1 = w1 \cup w2 = \overline{w1 \cdot w2}$$

$y2 = w3 \cup w4$

y3 = w5

$y4 = w1 \cup w2 \cup w6$

$y5 = w1 \cup w7$

$y6 = w2 \cup w5 \cup w8$

$y7 = w6 \cup w9$

Кроме обычных шифраторов существуют также **приоритетные шифраторы**. Такие шифраторы выполняют более сложную операцию. При работе ЭВМ и других устройств часто решается задача определения приоритетного претендента на обслуживание. Несколько конкурентов выставляют свои запросы на обслуживание, которые не могут быть удовлетворены одновременно. Нужно выбрать, кому предоставляется право первоочередного обслуживания.

Простейший вариант задачи — присвоение каждому источнику запросов фиксированного приоритета. Например, группа из восьми запросов R7, ..., R0 (R — от англ. request — запрос) формируется гак, что высший приоритет имеет источник номер семь, а далее приоритет уменьшается от номера к номеру. Самый младший приоритет у пулевого источника — он будет обслуживаться только при отсутствии всех других запросов. Если имеются одновременно несколько запросов, обслуживается запрос с наибольшим номером.

#### Практические задания:

#### Задание 1

#### Вариант 1:

Построить таблицу истинности и схему двухразрядного линейного дешифратора 2-4 (с двумя входами X1 и X2, 4 выходами) на элементах И.

#### Вариант 2:

Построить таблицу истинности и схему линейного шифратора 4-2 (с 4 входами X1-X4 и двумя выходами У0 и У1) на элементах И.

#### Задание 2

Используя таблицу истинности шифратора 10-4 и логические выражения, преобразованные по теореме де Моргана (см. выше теоретические сведения о шифраторе), построить схему шифратора на элементах И-НЕ.

#### Контрольные вопросы:

- 1. Что такое дешифратор?

- 2. Что такое шифратор?

- 3. Какие логические функции выполняет дешифратор?

- 4. Какие логические функции выполняет шифратор?

- 5. Что называется полным и неполным дешифратором?

- 6. Опишите принцип действия приоритетного шифратора.

### РАЗДЕЛ V. Комбинационные цифровые устройства

## **Тема 5.2. Мультиплексоры и демультиплексоры ЛАБОРАТОРНАЯ РАБОТА №2**

#### Исследование работы мультиплексора экспериментальным путем

**Цель:** Изучить принципы работы мультиплексора и демультиплексора. Научиться строить таблицы истинности и схему устройств.

#### Порядок выполнения

- 1. Изучить теоретическую часть

- 2. Выполнить практическое задание

- 3. Ответить на контрольные вопросы

- 4. Оформить отчет по проделанной работе

#### Теоретическая часть

Мультиплексор — комбинационная схема с несколькими входами и одним выходом. На выход мультиплексора передается информация с одного из пронумерованных входов. Номер входа, с которого данные поступают на выход, определяется комбинацией на управляющих (адресных) входах мультиплексора.

Мультиплексоры различаются по числу (N) входов данных

$$N=2^n$$

где n — количество адресных входов и записывают "мультиплексор N-1".

# Алгоритм синтеза устройства, реализующего логическую функцию на основе мультиплексора:

- 1) представить функцию в виде СДНФ;

- 2) для данной СДНФ заполнить карту Карно (Вейча);

- 3) на карте Карно (Вейча) выделить области по количеству информационных входов мультиплексора. Количество строк m и столбцов n в таких областях должно удовлетворять условию:  $m,n=2^k$ , где k=0,1,2,...Переменные, сохраняющие свое значение в пределах выделенных областей, являются адресными, а остальные информационными;

- 4) подать адресные переменные любым способом на адресные входы выбранного (или заданного) мультиплексора, определив таким образом однозначное соответствие адресных областей определенному информационному входу;

- 5) для каждой области найти МДНФ/МКНФ относительно информационных переменных, для управления информационными входами;

- 6) с помощью тождественных преобразований МДНФ/МКНФ привести к виду, удобному для совместной реализации;

- 7) реализовать схемы по каждому информационному входу мультиплексора в выбранном элементном базисе.

Пример построения мультиплексора, реализующего некоторую функцию:

$$\mathbf{Y} = \overline{X}_{1} \overline{X}_{2} \overline{X}_{1} \overline{X}_{1} + \overline{X}_{1} \overline{X}_{2} X_{1} X_{1} + \overline{X}_{1} X_{2} \overline{X}_{1} \overline{X}_{1} + \overline{X}_{1} X_{2} X_{1} X_{1} + X_{1} X_{2} \overline{X}_{1} X_{1} + X_{1} X_{2} \overline{X}_{1} X_{1} + X_{1} X_{2} X_{1} \overline{X}_{1}$$

$$+ X_{1} \overline{X}_{2} \overline{X}_{1} X_{1} + X_{1} \overline{X}_{2} X_{1} \overline{X}_{1}$$

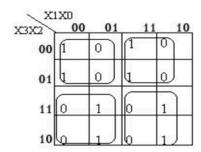

2) Для данной функции построим карту Карно:

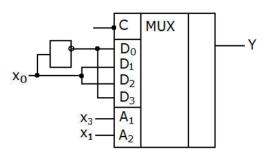

3) Пусть задан мультиплексор с 4 информационными входами (и 2 входа – адресные). На карте Карно выделим 4 адресные области. Переменные,

которые сохраняют свое значение в пределах выделенных областей, являются адресными:  $X_1, X_3$ .

- 4) Их можно двумя способами подать на адресные входы:  $A_1=X_1$ ,  $A_2=X_3$  либо  $A_1=X_3$ ,  $A_2=X_1$  (способ подачи не имеет значения).

- 5) Адресным областям соответствуют информационные входы  $D_0$ ,  $D_1$ ,  $D_2$ ,  $D_3$ .

Для каждой области найти МДНФ относительно информационных переменных  $X_0$ ,  $X_2$  (по принципам работы с картами Карно).

Получаем:

$$D_0 = \overline{X_0}, D_1 = X_0, D_2 = X_0, D_3 = \overline{X_0}$$

Реализуем полученные функции:

## Практические задания:

## Задание 1

Построить схему мультиплексора 8-1.

Задание 2

Построить схему демультиплексора (1-2), имеющего 1 вход и 2 выхода, используя элементы И, НЕ

**Задание 3**Построить схему устройства, реализующего логическую функцию (по вариантам) на основе мультиплексора

| $x_3$ | $x_2$ | $x_1$ | $x_0$ | вариан | вариан |

|-------|-------|-------|-------|--------|--------|

|       |       |       |       | m 1    | m 2    |

| 0     | 0     | 0     | 0     | 0      | 0      |

| 0     | 0     | 0     | 1     | 0      | 0      |

| 0     | 0     | 1     | 0     | 0      | 0      |

| 0     | 0     | 1     | 1     | 1      | 0      |

| 0     | 1     | 0     | 0     | 1      | 1      |

| 0     | 1     | 0     | 1     | 1      | 1      |

| 0     | 1     | 1     | 0     | 0      | 1      |

| 0     | 1     | 1     | 1     | 1      | 1      |

| 1     | 0     | 0     | 0     | 0      | 0      |

| 1     | 0     | 0     | 1     | 0      | 1      |

| 1     | 0     | 1     | 0     | 0      | 0      |

| 1     | 0     | 1     | 1     | 1      | 0      |

| 1     | 1     | 0     | 0     | 1      | 0      |

| 1     | 1     | 0     | 1     | 1      | 1      |

| 1 | 1 | 1 | 0 | 0 | 1 |

|---|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 1 | 1 |

#### Контрольные вопросы:

- 1. Что такое мультиплексор и для чего мультиплексоры используются?

- 2. Объясните назначение адресных входов.

- 3. Объясните назначение информационных входов.

- 4. Для чего в мультиплексорах используется вход С?

- 5. Для чего применяют каскадирование мультиплексоров?

#### РАЗДЕЛ V. Комбинационные цифровые устройства

# **Тема 5.3. Компараторы. Сумматоры ЛАБОРАТОРНАЯ РАБОТА №3**

### Исследование работы сумматоров экспериментальным путем

**Цель:** Изучить принципы работы полусумматора и сумматора. Научиться строить таблицу истинности и схему устройства.

## Порядок выполнения

- 1. Изучить теоретическую часть

- 2. Выполнить практическое задание

- 3. Ответить на контрольные вопросы

- 4. Оформить отчет по проделанной работе

## Теоретическая часть

Арифметико-логическое устройство процессора (АЛУ) обязательно содержит в своем составе такие элементы как **сумматоры**. Эти схемы позволяют складывать двоичные числа.

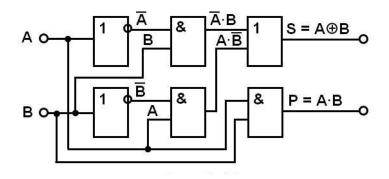

## Полусумматор

**Полусумматор** (рис. 1) имеет два входа а и b для двух слагаемых и два выхода: S – сумма, P – перенос. Обозначением полусумматора служат буквы

HS (half sum – полусумма). Работу его отражает таблица истинности 1 (табл. 1), а соответствующие уравнения имеют вид:

$$S = \overline{a}b + a\overline{b} = a \oplus b$$

$P = ab$  (1)

Таблица 1

Таблица 1

Рис. 1

$A = A = A \oplus B = a \oplus b$   $A \oplus B = a$   $A \oplus$

Из уравнений (1) следует, что для реализации полусумматора требуется один элемент "исключающее ИЛИ" и один двухвходовый вентиль И (рис. 1).

Очевидно, что по отношении: к столбцу S реализуется логическая функция «исключающее ИЛИ», т. е. S = A + B. Устройство, реализующее таблицу 1, называют полусумматором, и оно имеет логическую структуру, изображенную на рисунке 2.

Рисунок 2 – Логическая структура полусумматора

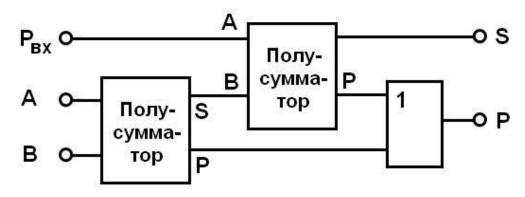

## Полный одноразрядный двоичный сумматор

При суммировании двух многоразрядных чисел для каждого разряда (кроме младшего) необходимо использовать устройство, имеющее дополнительный вход переноса. Такое устройство (рисунок 3) называют

полным сумматором и его можно представить как объединение двух полусумматоров ( $P_{\text{вх}}$  – дополнительный вход переноса). Сумматор обозначают через SM.

Рисунок 3 – Логическая структура сумматора

Он (рис. 2) имеет три входа: а, b — для двух слагаемых и р — для переноса из предыдущего (более младшего) разряда и два выхода: S — сумма, P — перенос в следующий (более старший) разряд. Обозначением полного двоичного сумматора служат буквы SM. Работу его отражает таблица истинности P (табл. 2).

Рис. 2

Таблица 2

| № наб. | a | b | p | P | S |

|--------|---|---|---|---|---|

| 0      | 0 | 0 | 0 | 0 | 0 |

| 1      | 0 | 0 | 1 | 0 | 1 |

| 2      | 0 | 1 | 0 | 0 | 1 |

| 3      | 0 | 1 | 1 | 1 | 0 |

| 4      | 1 | 0 | 0 | 0 | 1 |

| 5      | 1 | 0 | 1 | 1 | 0 |

| 6      | 1 | 1 | 0 | 1 | 0 |

| 7      | 1 | 1 | 1 | 1 | 1 |

В таблицах 2 и 3 выходные сигналы P и S не случайно расположены именно в такой последовательности. Это подчеркивает, что PS рассматривается как двухразрядное двоичное число, например,  $1+1=2_{10}=10_2$ , то есть P = 1, а S = 0 или  $1+1+1=3_{10}=11_2$ , то есть P = 1, а S = 1.

Уравнения, описывающие работу полного двоичного сумматора, представленные в совершенной дизъюнктивной нормальной форме (СДНФ), имеют вид:

$$S = \bar{a}\bar{b}p + \bar{a}b\bar{p} + a\bar{b}p + a\bar{b}p$$

$$(6)$$

Уравнение для переноса может быть минимизировано:

$$P = ab + ap + bp.$$

Поскольку полусумматор имеет только два входа, он может использоваться для суммирования лишь в младшем разряде.

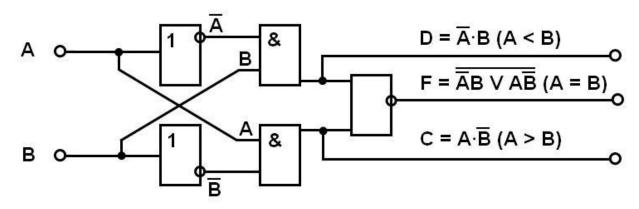

## Цифровые компараторы

**Цифровые компараторы** выполняют сравнение двух чисел, заданных в двоичном коде. Они могут определять равенство двух двоичных чисел A и B с одинаковым количеством разрядов либо вид неравенства A > B или A < B. Цифровые компараторы имеют три выхода.

Схема одноразрядного компаратора представляет собой структуру логического элемента «исключающее ИЛИ-НЕ» (рисунок 4).

#### Рисунок 4 – Логическая схема компаратора

Из анализа схемы следует, что если A=B, то F=1, в противном случае, т. е. при  $A \neq B$ , F=0. Если A > B, т. е. A=1, B=0, то C=1, а если A < B, т. е. A=0, B=1, то D=1.

Если попарно равны между собой все разряды двух п-разрядных двоичных чисел, то равны и эти два числа A и B. Применяя цифровой компаратор для каждого разряда, например, четырехзначных чисел, и определяя значения F1, F2, F3, F4 логических переменных на выходах компараторов, факт равенства A = B установим в случае, когда  $F = F1 \cdot F2 \cdot F3 \cdot F4 = 1$ . Если же F = 0, то  $A \neq B$ .

Неравенство A>B обеспечивается (для четырехразрядного числа) в четырех случаях: или  $A_4>B_4$ , или  $A_4=B_4$  и  $A_3>B_3$ , или  $A_4=B_4$ ,  $A_3=B_3$  и  $A_2>B_2$ , или  $A_4=B_4$ ,  $A_3=B_3$ ,  $A_2=B_2$  и  $A_1>B_1$  (где  $A_4$  и  $B_4$  — старшие разряды чисел A и B). Очевидно, что если поменять местами  $A_1$  и  $B_1$ , то будет выполняться неравенство A<B.

Цифровые компараторы выпускают, как правило, в виде самостоятельных микросхем. Так, микросхема К564ИП2 (рис. 3.52) является четырехразрядным компаратором, в котором каждый из одноразрядных компараторов аналогичен рассмотренной ранее схеме. Данная микросхема имеет расширяющие входы A < B, A = B, A > B, что позволяет наращивать разрядность обоих чисел. Для этого компараторы соединяют каскадно или параллельно (пирамидально).

#### Практические задания:

#### Задание 1

Постройте таблицу истинности и его логическую схему для полусумматора. Приведите УГО.

#### Задание 2

Постройте таблицу истинности и его логическую схему для сумматора. Приведите УГО.

#### Контрольные вопросы

- 1. Что представляет собой полусумматор?

- 2. Дайте определение и опишите назначение сумматора.

- 3. Приведите классификацию сумматоров по различным признакам.

- 4. Дайте определение и опишите назначение компаратора.

#### РАЗДЕЛ VI. Последовательностные цифровые устройства

## Тема 6.1. Триггеры ЛАБОРАТОРНАЯ РАБОТА №4

#### Исследование работы триггеров экспериментальным путем

**Цель:** Изучить принципы работы триггеров. Научиться строить таблицу истинности и схему устройства.

## Порядок выполнения

- 1. Изучить теоретическую часть

- 2. Выполнить практическое задание

- 3. Ответить на контрольные вопросы

- 4. Оформить отчет по проделанной работе

## Теоретическая часть

Триггер (триггерная система) — класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний ((1)» или (0)») и чередовать их под воздействием внешних сигналов.

Триггер — это простейшее устройство, предназначенное для записи и хранения одноразрядных двоичных чисел.

Триггер имеет два выхода (прямой Q и инверсный  $\bar{Q}$ ) и один или несколько входов.

Входы триггера разделяются на информационные и управляющие.

#### Информационные входы обозначаются следующим образом:

- S вход для установки в состояние «1»;

- R вход для установки в состояние «0»;

- J − вход для установки в состояние «1» в универсальном триггере;

- К вход для установки в состоянии «0» в универсальном триггере;

- Т счётный (общий) вход;

- D вход для установки в состояние «1» или состояние «0».

#### Управляющие входы обозначаются:

- V дополнительный управляющий вход для разрешения приёма информации;

- С вход синхронизации.

#### Триггеры имеют 2 выхода:

Q – прямой,

Q – инверсный.

Триггеры можно классифицировать по способу приёма информации, принципу построения, функциональным возможностям.

По способу приёма информации триггеры подразделяются на асинхронные и синхронные.

Асинхронные триггеры воспринимают информационные сигналы и реагируют на них в момент появления на входах триггера.

Синхронные триггеры реагируют на информационные сигналы при наличии разрешающего сигнала на специальном управляющем входе C, называемом входом синхронизации. Синхронные триггеры подразделяются на триггеры со статическим и динамическим управлением по входу C. Триггеры со статическим управлением воспринимают информационные сигналы при

подаче на С-вход уровня 1 (прямой С-вход). Триггеры с динамическим управлением воспринимают информационные сигналы при изменении сигнала на С-входе от 0 к 1(прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход).

По принципу построения триггеры со статическим управлением делятся на одноступенчатые и двух ступенчатые.

Одноступенчатые триггеры характеризуются наличием одной ступени запоминания информации, двухступенчатые триггеры имеют две ступени запоминания информации. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе.

Двухступенчатый триггер обозначают через TT.

По функциональным возможностям триггеры разделяются на следующие классы:

- с раздельной установкой состояния 0 и 1 (RS-триггеры);

- универсальные (ЈК-триггеры);

- с приемом информации по одному входу D (D-триггеры);

- со счётным входом Т (Т-триггеры).

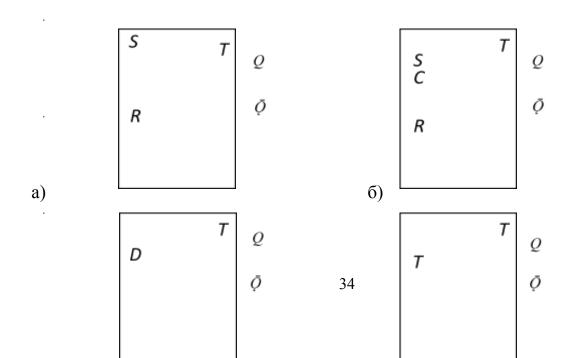

Независимо от вида, если Q=1 и  $\bar{Q}=0$ , то триггер находится в единичном состоянии. При Q=0,  $\bar{Q}=1$  состояние триггеры называется нулевым. Ниже приведены графические обозначения (УГО) триггеров, принятые в системе ЕСКД:

С

Рисунок 1 – Триггеры:

- 1) асинхронный RS-синхронный триггер

- 2) синхронизируемый RS-триггер

- 3) D-триггер

- 4) Т-триггер

- 5) ЈК-триггер

Функционирование триггеров описывается таблицами переходов (истинности):

RS-триггер

| Bxc | ДЫ | Выходь | Выходы |  |  |  |

|-----|----|--------|--------|--|--|--|

| R   | S  | Q      | Ō      |  |  |  |

| 0   | 0  | исх.   | исх.   |  |  |  |

| 0   | 1  | 1      | 0      |  |  |  |

| 1   | 0  | 0      | 1      |  |  |  |

| 1   | 1  | неопр. | неопр  |  |  |  |

## D-триггер

| Вхо | ды | Выходы |

|-----|----|--------|

| D   | С  | Q      |

| 1   | 1  | 1      |

| 0   | 1  | 0      |

Т-триггер

| Входы | Выходы           |

|-------|------------------|

| T     | Q                |

| 0     | исх.             |

| 1     | Q <sub>n-1</sub> |

ЈК-триггеры

| Входы |   | Выход             |

|-------|---|-------------------|

|       |   | Ы                 |

| J     | K | Q                 |

| 0     | 0 | исх.              |

| 0     | 1 | 0                 |

| 1     | 0 | 1                 |

| 1     | 1 | Q̄ <sub>n-1</sub> |

«исх.» — означает режим хранения (исходное состояние или без изменения). «неопр.» — означает, что состояние выходов неопределённое, т. е. комбинация сигналов R = S = 1 является запрещённой.

Схема асинхронного RS-триггера на логических элементах 2ИЛИ-НЕ приведена на рисунке. Управление на схеме осуществляется положительными сигналом (единицей).

#### Практические задания:

### Вариант 1

Постройте таблицу истинности асинхронного RS-триггера. Нарисуйте схему асинхронного RS-триггера на логических элементах и его УГО. Поясните принцип работы устройства.

#### Вариант 2

Постройте таблицу истинности D-триггера. Нарисуйте схему D-триггера на логических элементах и его УГО. Поясните принцип работы устройства.

#### Вариант 3

Постройте таблицу истинности ЈК-триггера. Нарисуйте схему ЈК-триггера на логических элементах и его УГО. Поясните принцип работы устройства.

#### Вариант 4

Постройте таблицу истинности Т-триггера. Нарисуйте схему Т-триггера на логических элементах и его УГО. Поясните принцип работы устройства.

#### Контрольные вопросы:

- 1. Что такое триггер?

- 2. Опишите основное назначение триггеров.

- 3. Опишите основные виды триггеров, приведите их УГО (условно-графическое изображение).

- 4. По каким признакам классифицируются триггеры?

- 5. Опишите принцип действия синхронного и асинхронного триггера

- 6. Назовите область применения триггеров.

- 7. Почему ЈК-триггер считается универсальными?

# РАЗДЕЛ VI. Последовательностные цифровые устройства Тема 6.2. Регистры

#### ЛАБОРАТОРНАЯ РАБОТА №5

# Исследование работы регистра экспериментальным путем

**Цель:** Изучить принципы работы регистров. Научиться строить таблицу истинности и схему устройства.

# Порядок выполнения

- 1. Изучить теоретическую часть

- 2. Выполнить практическое задание

- 3. Ответить на контрольные вопросы

- 4. Оформить отчет по проделанной работе

# Теоретическая часть

Регистры предназначены для хранения и преобразования многоразрядных двоичных чисел. Для запоминания отдельных разрядов числа

могут применяться триггеры различных типов. Одиночный триггер можно считать одноразрядным регистром.

Занесение информации в регистр называется операцией записи. Операция выдачи информации из регистра – считывание.

Перед записью информации в регистр, его необходимо обнулить.

#### Классификация регистров:

#### 1. по способу ввода/вывода информации:

- параллельные (регистры хранения) информация вводится и выводится одновременно по всем разрядам;

- последовательные (регистры сдвига) информация бит за битом «проталкивается» через регистр и выводится также последовательно;

- комбинированные (последовательно-параллельные) параллельный ввод и последовательный вывод (и наоборот).

# 2. по способу представления информации:

- однофазные информация представляется в прямом или обратном (инверсном) виде;

- парафазные информация представляется и в прямом, и в обратном виде.

# Параллельный регистр

Параллельные регистры осуществляют прием и выдачу информации в параллельном коде, а это значит, что для передачи каждого разряда используется отдельная линия. Все разряды двоичного кода слова передаются в одном временном такте.

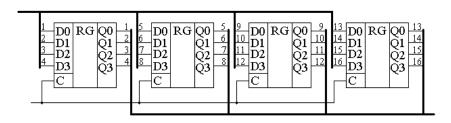

Для записи информации в регистр на его входных выводах (D0-D3) нужно установить значения (логические уровни), после чего на вход синхронизации (С) подать разрешающий импульс – логическую единицу. После этого на выходах Q0-Q3 появится записанное слово. Регистры

запоминают входные сигналы только в момент времени, определяемый сигналом синхронизации.

| D0 | RG Q0 |

|----|-------|

| D1 | Q1    |

| D2 | Q2    |

| D3 | Q3    |

| С  |       |

б)

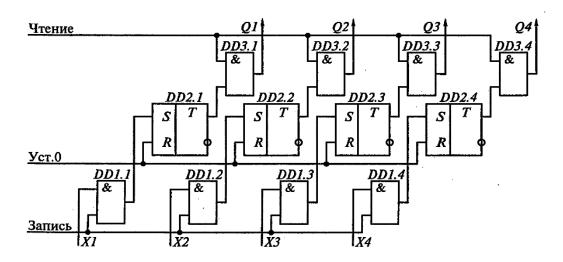

Рисунок 1 - a) схема параллельного регистра на D-триггерах, б)УГО

Рисунок 2 – Схема параллельного регистра на RS-триггерах

Регистр может работать в следующих режимах:

- предварительная установка (подготовка триггеров регистра к записи информации);

- запись информации в триггеры регистра;

- хранение ранее записанной информации;

- чтение информации из регистра.

Логические элементы И (DD1.1-1.4) используются для ввода в регистр четырехразрядной информации со входов X1-X4. Информация хранится в асинхронных RS-триггерах (элементы памяти DD2.1-2.4). Для чтения информации из регистра служат прямые выходы триггеров (выходные элементы DD3.1-3.4).

При решении практических задач часто требуется разрядность параллельных регистров большая восьми. В таком случае можно увеличивать их разрядность параллельным соединением готовых микросхем.

#### Последовательные регистры

Последовательный регистр (регистр сдвига) обычно служит для преобразования последовательного кода в параллельный и наоборот. Применение последовательного кода связано с необходимостью передачи большого количества двоичной информации по ограниченному количеству соединительных линий. При параллельной передаче разрядов требуется большое количество соединительных проводников. Если двоичные разряды последовательно бит за битом передавать по одному проводнику, то можно значительно сократить размеры соединительных линий на плате (и размеры корпусов микросхем).

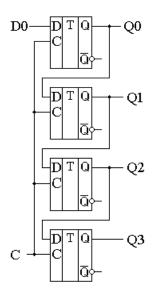

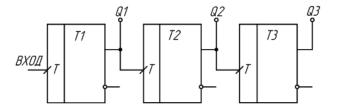

Внутри сдвигового регистра триггеры соединены последовательно, то есть выход первого соединён с входом второго и т.д.: межразрядные связи соединяют выходы триггеров младших разрядов с входами триггеров старших позволяет осуществить последовательное разрядов, что продвижение информации ИЗ разряда разряд ПОД воздействием управляющих синхроимпульсов С.

Последовательный регистр имеет один вход для последовательного ввода информации. Входы синхронизации в последовательных (сдвиговых) регистрах, как и в параллельных регистрах, объединяются. Это обеспечивает одновременность смены состояния всех триггеров, входящих в состав последовательного (сдвигового) регистра.

Рисунок 4 – Схема последовательного регистра на D-триггерах

Рассмотрим работу этого регистра. Можно предположить, что в начале все триггеры регистра находятся в состоянии логического нуля, т.е. Q0=0, Q1=0, Q2=0, Q3=0. Если на входе D-триггера Т1 имеет место логический 0, то поступление синхроимпульсов на входы «С» триггеров не меняет их состояния.

Синхроимпульсы поступают на соответствующие входы всех триггеров регистра одновременно и записывают в них то, что имеет место на их информационных входах. На информационных входах триггеров Т2, Т3, Т4 — уровни логического «0», т.к. информационные входы последующих триггеров соединены с выходами предыдущих триггеров, находящихся в состоянии логического «0», а на вход «D» первого триггера, по условию примера, подается «0» из внешнего источника информации. При подаче на вход «D» первого триггера «1», с приходом первого синхроимпульса, в этот триггер запишется «1», а в остальные триггеры — «0», т.к. к моменту поступления фронта синхроимпульса на выходе триггера Т1 ещё присутствовал логический «0». Таким образом, в триггер Т1 записывается та информация (тот бит), которая была на его входе «D в момент поступления фронта синхроимпульса и т.д.

При поступлении второго синхроимпульса логическая «1» с выхода первого триггера, запишется во второй триггер, и в результате происходит сдвиг первоначально записанной «1» с триггера Т1 в триггер Т2, из триггера Т2 в триггер Т3 и т.д. Таким образом, производится последовательный сдвиг поступающей на вход регистра информации (в последовательном коде) на один разряд вправо в каждом такте синхроимпульсов.

После поступления четырёх синхроимпульсов регистр оказывается полностью заполненным разрядами числа, вводимого через последовательный ввод «D». В течение следующих четырёх синхроимпульсов производится последовательный поразрядный вывод из регистра записанного числа, после чего регистр оказывается полностью очищенным (регистр окажется полностью очищенным только при условии подачи на его вход уровня «0» в режиме вывода записанного числа).

Рисунок 5 – Регистр параллельного действия

Регистр последовательного действия уступает регистру параллельного действия в быстродействии и используется только в случаях, когда количество входных и выходных линий связи ограничено.

# Практические задания:

#### Задание 1.

Построить на D-триггерах схемы последовательного и параллельного регистров в синхронной реализации

# Задание 2.

Нарисовать УГО последовательного и параллельного регистра. Определить как связанны отдельные триггеры в данных регистрах.

# Контрольные вопросы:

- 1. Назовите основное назначение регистров.

- 2. По каким признакам классифицируются регистры?

- 3. Чем определяется разрядность регистров?

- 4. Объясните принцип работы последовательного регистра.

- 5. Объясните принцип работы параллельного регистра.

- 6. Опишите назначение последовательно-параллельного регистра.

# РАЗДЕЛ VI. Последовательностные цифровые устройства

#### Тема 6.3. Счетчики

#### ЛАБОРАТОРНАЯ РАБОТА№6

#### Исследование работы счетчиков экспериментальным путем

**Цель:** Изучить принципы работы счетчиков. Научиться строить таблицу истинности и схему устройства.

#### Порядок выполнения

- 1. Изучить теоретическую часть

- 2. Выполнить практическое задание

- 3. Ответить на контрольные вопросы

- 4. Оформить отчет по проделанной работе

#### Теоретическая часть

Счетчики — устройства, предназначенные для счета числа импульсов, поступающих на их вход. Каждый счетный импульс изменяет состояние счетчика на единицу. Если при счете коды состояния расположены в возрастающем порядке, то счетчик называется суммирующем, если в убывающем порядке — вычитающим. Счетчики, у которых направление счета может изменяться, называются реверсивными.

Число разрешенных состояний счетчика называется **модулем счета** М (или коэффициентом пересчета счетчика  $K_{cq}$ ). Характеризует число (количество) устойчивых состояний, в которых может находиться п-разрядный счетчик, т.е. предельное число входных сигналов, которое может быть подсчитано счетчиком. При поступлении на счетчик числа импульсов больше  $K_{cq}$  счетчик возвращается в исходное состояние.

Счетчики, у которых модуль счета равен целой степени числа 2 ( $M=2^n$ ), называются **двоичными**.

Основу счетчиков составляют триггерные схемы. Счетчики могут быть собраны на D-триггерах, JK-триггерах. Триггеры соединяются последовательно.

По способу организации межразрядных связей счетчики делятся на:

- Асинхронные (переключение триггеров в разрядах осуществляется последовательно один за другим);

- Синхронные (переключение триггеров в разрядах осуществляется одновременно по сигналу синхронизации).

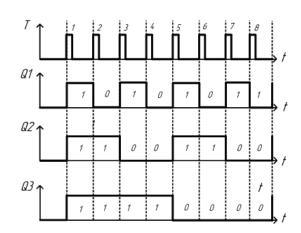

Представление счётчика цепочкой счётных триггеров справедливо как для суммирующего, так и для вычитающего вариантов. При прямом счёте (суммирование) следующий разряд переключается при переходе предыдущего в направлении из 1 в 0, а при обратном счёте – при переключении из 0 в 1.

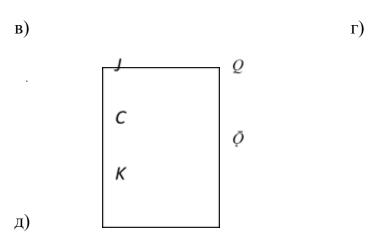

#### Простейший вычитающий асинхронный счётчик на Т-триггерах

Рассмотрим схему счётчика на Т-триггерах, опрокидывающихся по переднему фронту входных импульсов.

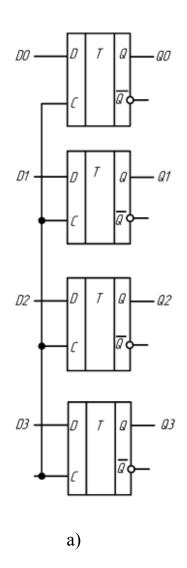

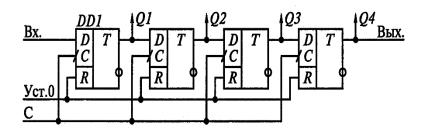

Рисунок 1 – Вычитающий счётчик

Временная диаграмма

Из временной диаграммы видим, что получился вычитающий счётчик. Если информацию снимать с инверсных выходов триггеров, то получится суммирующий счётчик. Суммирующий асинхронный счетчик на **D**-триггерах получается, если инверсный выход предыдущего триггера соединить со входом С последующего триггера. При этом инверсный выход **D**-триггера соединяют с его входом **D**. Счётный режим возможен только у триггеров динамического типа.

Для построения **вычитающего счетчика на D-триггерах** прямой выход предыдущего триггера соединяют со входом С последующего триггера. При этом инверсный выход D-триггера соединяют с его входом D.

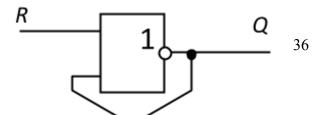

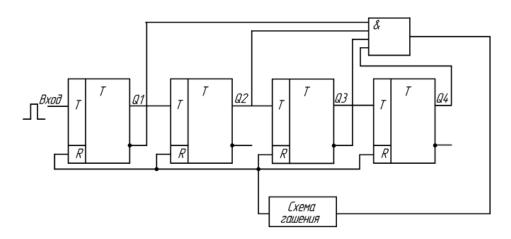

# Счётчик с произвольным модулем счёта (с ограниченным модулем счёта)

K счетчику добавляется логическая схема, проверяющая условие: «код на счетчике изображает число равное  $K_{cq}$ ?». В зависимости от результата проверки направляет входной сигнал либо на шину «Установка 0», либо на суммирование к записанному коду.

Это условие можно проверить с помощью n-входовой схемы U, связанной с прямыми выходами тех триггеров, которые при записи в счетчике числа, равного  $K_{cq}$  должны находиться в состоянии «1» и с инверсными выходами триггеров, которые в этом случае должны находиться в состоянии «0».

Для построения счётчика с произвольным модулем счета можно использовать двоичный счётчик, у которого модуль счёта М должен быть больше модуля счёта разрабатываемого счётчика с произвольным модулем счёта.

#### Пример 1:

Пусть нужно сделать счётчик с M=10 (т.е. счетчик должен иметь 10 состояний: от  $0_{10}$  до  $9_{10}$  или от  $0000_2$  до  $1001_2$ ).

У 4-х разрядного счётчика модуль счёта равен 16 (больше 10).

Схема счётчика представляет собой 4 последовательно включённых счётных триггера, у которых есть вход сброса R (первый триггер содержит младший разряд числа).

Число 10 в двоичной системе счисления представляется 1010. Когда на выходах счетчика будет код 1010, на выходе элемента «И» появится логическая единица, которая запустит схему гашения. Длительность импульса на выходе схемы гашения должна быть достаточна для надёжного сброса всех триггеров счётчика в 0.

Разряды числа 1010, равные 1 подаются на схему «И» с прямых выходов триггеров, а равные 0 - с инверсных. Таким образом, как только счётчик досчитает до 10, произойдёт обнуление всех триггеров и счёт продолжится с кода 0000.

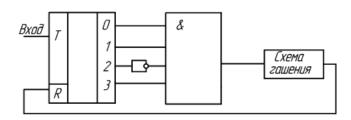

Рисунок 2 – Счётчик с модулем счета М=10 на Т-триггерах

*Пример 2:* Рассмотрим счётчик с M=11 на основе двоичного счётчика в одной микросхеме (без инверсных выходов).

11<sub>10</sub>=1011<sub>2</sub>

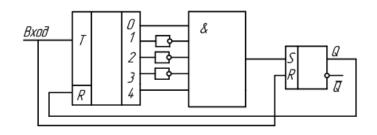

Счётчик с модулем счёта М=11

Пример 3: В качестве схемы гашения может быть RS-триггер.

Счётчик с модулем счёта М=17

В этой схеме  $M=10001_2=17_{10}$

Сигнал на входе К счётчика будет действовать в течение одного периода входных импульсов.

#### Практические задания:

#### Задание 1

#### Варианты 1:

Построить схему асинхронного 4-х разрядного суммирующего счетчика на D-триггерах с R-входом для сброса счетчика. Нарисуйте УГО полученного устройства.

#### Варианты 2:

Построить схему асинхронного 4-х разрядного вычитающего счетчика на D-триггерах с R-входом для сброса счетчика. Нарисуйте УГО полученного устройства.

#### Задание 2

Построить схему суммирующего счетчика с модулем счета  $K_{cq}$  = вашему варианту

#### Задание 3

Изобразите временные диаграммы работы суммирующего счётчика.

#### Задание 4

Изобразите временные диаграммы работы вычитающего счётчика.

# Контрольные вопросы:

- 1. Дайте определение понятию «Счетчик».

- 2. Приведите классификацию счетчиков.

- 3. Объясните принцип работы суммирующего счётчика.

- 4. Объясните принцип работы вычитающего счётчика.

- 5. Объясните принцип работы счётчика с произвольным модулем счёта.

РАЗДЕЛ VII. Организация устройств ЭВМ

# **Тема 7.1. Арифметико-логические устройства**ЛАБОРАТОРНАЯ РАБОТА №7

#### Исследование работы АЛУ экспериментальным путем

Цель: Исследование командного цикла процессора на уровне микрокоманд

### Порядок выполнения

- 1. Изучить теоретическую часть

- 2. Выполнить практические задания

- 3. Занести результаты работы программы в таблицу анализа состояния микропроцессора

- 4. Ответить на контрольные вопросы

- 5. Оформить отчет по проделанной работе

#### Теоретическая часть

Арифметико-логическое устройство АЛУ (Arithmetic-Logic Unit – ALU) представляет собой комбинационное устройство на основе сумматора, выполняющее ряд дополнительных функций обработки данных. На рисунке 1 представлено условное обозначение типичного 4-разрядного АЛУ, реализованного в модуле 74181.

Рисунок 1 – Условное обозначение четырёхразрядного АЛУ (модуль 74181)

Представленное АЛУ содержит две группы входов ДЛЯ ДВVX 4-разрядных операндов (обрабатываемых двоичных чисел) A0N...A3N и B0N...B3N. На выводах F0N...F3N формируется 4-разрядный результат выполненной операции. Вход CN предназначен для подачи входного переноса в младший разряд устройства, если такой перенос существует. Выход CN4 содержит перенос в пятый разряд в случае его возникновения в ходе выполнения операции. Выходы GN и PN предназначены для подачи групповых функций генерации и распространения на внешнюю схему ускоренного формирования переносов (74182). Эта схема может быть использована для построения АЛУ с разрядностью более 4 и параллельным распространением переноса между 4-разрядными блоками. На выходе AEQB формируется сигнал равенства операндов А и В.

Входы SO...S3 и М обеспечивают выбор одной из 32 возможных операций, выполняемых устройством. Список операций представлен в таблице 1. Все операции делятся на две группы: логические и арифметические. Переключение между группами осуществляется с помощью входа М. Приведенная таблица соответствует положительной логике линий данных (1 - высокий уровень). Входные 4-разрядные операнды (данные) и 4-разрядный результат операции обозначены в таблице буквами A, B и F. Бит входного переноса носит имя соответствующего вывода модуля CN.

Логические операции выполняются над операндами побитово (поразрядно), т. е. без взаимодействия разрядов. Эти операции присутствуют и в логическом и в арифметическом режимах. Для отличия от арифметических операций, выполняемых с учетом переносов в разрядах и обозначаемых в таблице обычными символами + и логические операции указаны с помощью кратких обозначений языка AHDL (символом решетка (#) обозначена операция дизьюнкции (ИЛИ), символом доллар (\$) – операция сложения по (исключающее ИЛИ)). Если модулю при выполнении арифметического режима возникает перенос в пятый разряд, то на выходе CN4 устанавливается 0, в противном случае на нем остается 1.

Внутри центрального процессора (CPU) содержится несколько ячеек памяти, называемых **регистрами.** В данном случае эти регистры занимают один байт (8 бит) памяти. Таким образом, в любой момент времени каждый из этих 8-битных регистров хранит одно значение от 0 до 255, или от \$00 до \$FF в шестнадцатеричной системе (рисунок 2).

Внутри этого процессора также есть несколько ячеек памяти, называемых **флагами**, каждый из которых занимает один бит памяти и используется для представления булевых значений. Таким образом, в любой момент времени каждый из этих 1-битных флагов имеет значение TRUE, либо FALSE.

|                               | цанных         | 8                                                                | Регистры ука          | MARKET AND LOSS  |

|-------------------------------|----------------|------------------------------------------------------------------|-----------------------|------------------|

| АН                            | AL             | Аккумулятор                                                      | SI                    | Индекс источника |

| BH                            | BL             | Базовый регистр                                                  | DI                    | Индекс приемник  |

| CH                            | CL             | Счетчик                                                          | BP                    | Указатель базы   |

| DH                            | DL             | Регистр данных                                                   | SP                    | указаель стека   |

| 310                           | ые регист<br>З | <b>ры</b><br>Регистр сегмента кома                               | ю́Т                   |                  |

| C                             | 350            |                                                                  |                       |                  |

| C                             | :5             |                                                                  | ых                    | анных            |

| C<br>E                        | s<br>s         | Регистр сегмента кома Регистр сегмента данн                      | ых<br>эго сегмента да | анных            |

| C<br>I<br>E                   | es<br>es<br>es | Регистр сегмента кома Регистр сегмента данн Регистр дополнительн | ых<br>эго сегмента да | анных            |

| С<br>Е<br>S<br><b>Эчне ре</b> | s<br>s<br>s    | Регистр сегмента кома Регистр сегмента данн Регистр дополнительн | ых<br>эго сегмента да | анных            |

Рисунок 2 – Регистры процессора

**Программа** – это последовательность инструкций, которые указывают центральному процессору, что делать. Большинство инструкций состоит из операции и одного или нескольких операндов, в зависимости от операции.

**Операция** — это как функция, встроенная в процессор и предоставляемая программисту для немедленного использования. Каждая

операция имеет короткое запоминающееся имя, называемое мнемоникой. В письменном языке ассемблера операции обозначаются этой мнемоникой.

**Операнд** — это как аргумент операции. Операндом может быть регистр процессора, ячейка памяти или литеральное значение.

#### Принципы организации командных и машинных циклов

**Команда** представляет собой совокупность микрокоманд, которые в виде двоичных кодов хранятся в постоянной памяти (ПЗУ) устройства управления процессора.

Выполнение команды можно рассматривать как процесс считывания из ПЗУ микрокоманд, инициирующих работу некоторых функциональных узлов процессора на отдельных временных интервалах (тактах). Время, затрачиваемое на выполнение команды, называется командным циклом.

Команды имеют не одинаковую длительность командных циклов, так как содержат различное число микрокоманд, используют разные способы адресации и другую дополнительную информацию. Это обстоятельство отражается в форматах команд, имеющих длину один, два и более байт.

В командном цикле можно выделить две основные фазы:

# • фазу выборки команды

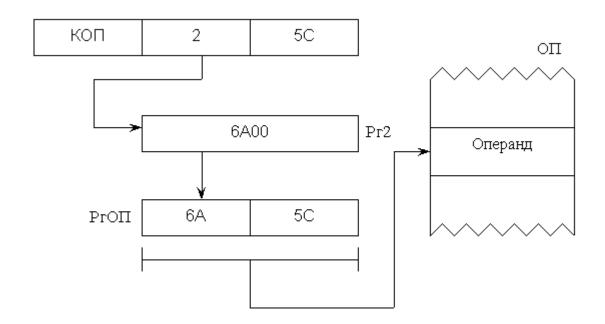

В этой фазе программный счетчик РС выставляет на адресную шину адрес первого байта команды. Микропроцессор вырабатывает сигнал «чтения памяти», благодаря которому содержимое адресуемой ячейки памяти по шине данных поступает в регистр команд IR (Instruction Register).

Программный счетчика РС формирует адрес, указывающий на следующий элемент объектного кода. Фаза выборки одинакова для всех команд;

# • фазу выполнения команды

Фаза начинается с дешифрации команды. В результате дешифрации первого байта определяется вид (код) операции и в устройстве управления формируются необходимые для ее выполнения управляющие сигналы.

Действия процессора в фазе выполнения команды и ее продолжительность зависит от вида операции. Для выполнения операции может потребоваться дополнительное обращение к памяти или внешним устройствам за данными, пересылка данных в соответствующие регистры процессора, непосредственное выполнение операции в АЛУ, вывод результатов в память или внешнее устройство и т. д.

Различная длительность командных циклов и неоднородность их отдельных фаз явились причиной организации машинных циклов для выполнения команд.

Каждый машинный цикл представляет собой цикл обращения к системной магистрали. В машинном цикле производится выборка очередного байта (слова) команды или данных из памяти, запись в память, ввод или вывод данных. Командный цикл может содержать различное число машинных циклов. В первом машинном цикле М1 происходит выборка первого байта команды, ее дешифрация и исполнение, если данные находятся во внутренних регистрах процессора. Если выполнение команды требует обращения к памяти или внешним устройствам, то используется два, три и более машинных циклов.

Машинные циклы, как и командные, также не являются однородными. Поэтому на их выполнение затрачивается различное число тактов.

Таким образом, при выполнении команды все действия процессора синхронизированы вложенными друг в друга циклами трех уровней: командными, машинными и тактовыми.

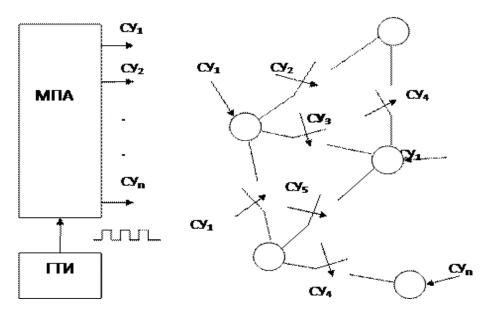

ЭВМ Реализация программы сводится К последовательному выполнению команд. Каждая команда, в свою очередь, выполняется как последовательность микрокоманд, реализующих элементарные действия над операционными элементами процессора. Для пояснения логики функционирования ЭВМ ее целесообразно представить в виде совокупности узлов, связанных между собой коммуникационной сетью (рисунок 3).

Рисунок 3 – Связь команд микропроцессора

Процесс функционирования вычислительной машины состоит в последовательности пересылок информации между ее узлами и элементарных действий (микроопераций), выполняемых в узлах. Понятие узла здесь трактуется весьма широко: от регистра до АЛУ или основной памяти. Также широко следует понимать и термин «элементарное действие». Это может быть установка регистра в некоторое состояние или выполнение операции в АЛУ.

Любое элементарное действие производится при поступлении соответствующего сигнала управления (СУ) из микропрограммного автомата устройства управления. Возможная частота формирования сигналов на выходе автомата определяется синхронизирующими импульсами, поступающими от генератора тактовых импульсов (ГТИ).

Элементарные пересылки или преобразования информации, выполняемые в течение одного такта синхронизации, называются микрооперациями. В течение одного такта могут одновременно выполняться несколько микроопераций. Совокупность сигналов управления, вызывающих микрооперации, выполняемые в одном такте, называют микрокомандой.

Относительно сложные действия, осуществляемые вычислительной машиной в процессе ее работы, реализуются как **последовательность микроопераций**

и могут быть заданы последовательностью микрокоманд, называемой **микропрограммой**.

Реализует микропрограмму, то есть вырабатывает управляющие сигналы, задаваемые ее микрокомандами, микропрограммный автомат (МПА).

# Практическая часть

#### Задание 1.

# Исследуйте состояние регистров и памяти во время выполнения программы

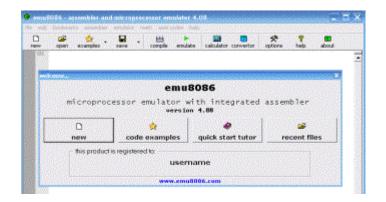

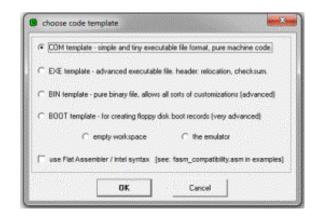

1. Запустите эмулятор и щелкните на кнопку new

2. Выберите тип исполняемого файла:

Директивы, определяющие тип исполнимого файла: #MAKE\_COM# #MAKE BIN#

#MAKE BOOT#

#MAKE EXE#

Вы можете вставить эти директивы в исходный код для определения нужного вам типа исполнимого файла.

Описание типов исполнимых файлов:

#MAKE\_COM# – самый старый и самый простой формат исполнимого файла. Такие файлы загружаются с префиксом 100h (256 байтов).

#МАКЕ\_ЕХЕ# – более "продвинутый" формат исполнимого файла. Не ограничены размер и количество сегментов.

#MAKE\_BIN# – простой исполнимый файл.

#MAKE\_BOOT# – эта директива копирует первую дорожку дискеты (загрузочный сектор).

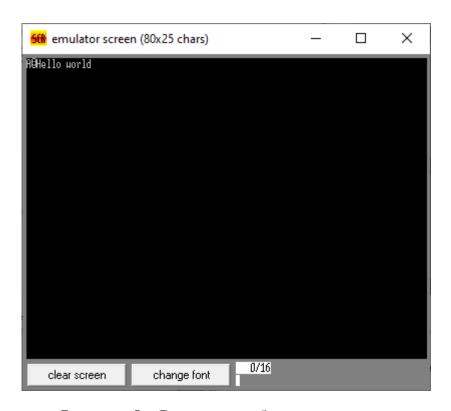

# 3. Создайте файл, который будет выводить: Hello, world

Для этого введите в строке «add your code here» следующие команды:

| № строки | Команда                                |

|----------|----------------------------------------|

| 1        | org 100h                               |

| 2        | begin:                                 |

| 3        | mov ah, 9                              |

| 4        | mov dx, offset message                 |

| 5        | int 21h                                |

| 6        | ret                                    |

| 7        | message db "Hello word", 0dh 0ah, '\$' |

| 8        | end begin                              |

```

32 ORG 100h

33 begin:

34 HOV AH, 9

35 HOV DX, offset message

36 INT 21h

37 ret

38 message db "Hello world", Odh, Oah, '$'

39 end begin

```

#### Рассмотрим исходный текст программы:

- 1 строка ORG 100h устанавливает значение программного счетчика (IP) в 100h, потому что при загрузке COM—файла в память DOS занимает первые 256 байт (100h) блоком данных PSP и располагает код программы только после этого блока. Все программы, которые компилируются в файлы типа COM, должны начинаться с этой директивы.

- 2 строка Метка BEGIN: располагается перед первой командой в программе и будет использоваться в директиве END (Begin англ. начало; end конец), чтобы указать, с какой команды начинается программа. Вообще вместо слова BEGIN можно было бы использовать что-нибудь другое. Например, START:. В таком случае, нам пришлось бы и завершать программу END START.

- *Строки (3) (5)* выводят на экран сообщение "Hello".

Команда MOV DX, OFFSET MESSAGE помещает в регистр DX смещение метки MESSAGE относительно начала сегмента данных, который в нашем случае совпадает с сегментом кода. OFFSET (по-английски – это смещение). Когда, при ассемблировании, Ассемблер дойдет до этой строки, он заменит OFFSET MESSAGE на АДРЕС (смещение) этой строки в памяти. Если мы запишем OFFSET MESSAGE (хотя, правильнее будет MOV DX, WORD OFFSET MESSAGE), то в DX загрузится не адрес (смещение), а первые два символа нашей строки (в данном случае "He"). Так как DX — шестнадцатиразрядный регистр, в него можно загрузить только два байта (один символ всегда один байт).

Команда INT 21H вызывает системную функцию DOS (int от англ. interrupt – прерывание). Прерывание MS–DOS – это своего рода подпрограмма (часть MS–DOS), которая находится постоянно в памяти и может вызываться в любое время из любой программы. Эта команда – основное средство взаимодействия программ с операционной системой. В примере вызывается функция DOS (строка 7) – вывести строку на экран. Эта функция выводит строку от начала, адрес которого задается в регистрах DS: DX, до первого

встречного символа \$. При запуске COM-файла регистр DS автоматически загружается сегментным адресом программы, а регистр DX был подготовлен предыдущей командой.

- 6 строка Команда RET пользуется обычно для возвращения из процедуры. DOS вызывается СОМ-программы так, что команда RET корректно завершает программу.

- 7 строка определяет строку данных, содержащую текст "Hello ", управляющий символ ASCII возврат каретки с кодом 0Dh, управляющий символ ASCII перевод строки с кодом 0Ah и символ \$, завершающий строку. Первое слово (message сообщение) название сообщения. Оно может быть любым (например, mess или string и пр). Управляющие символы (0Dh и 0Ah) переводят курсор на первую позицию следующей строки.

- *8 строка* директива END завершает программу, одновременно указывая, с какой метки должно начинаться ее выполнение.

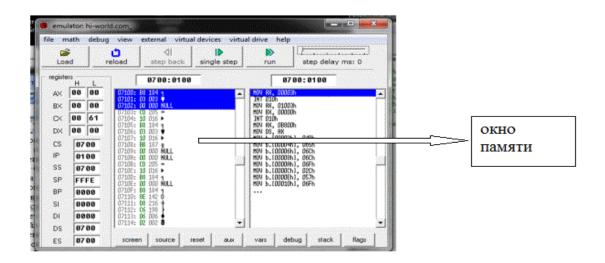

- 4. Щелкните **кнопку [emulate]** (или нажмите клавишу **F5**).

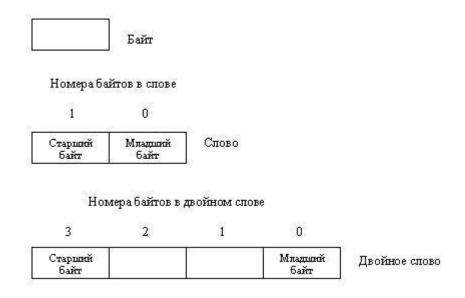

- 5. Щелкните **кнопку [Single Step] (пошаговый режим)** (или нажмите клавишу **F8**), и наблюдайте за выполнением кода.