## APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

B.Tech Degree S5 (R, S) / S3 (PT) (R, S) Examination December 2023 (2019 Scheme)

Course Code: ECT 301

Course Name: LINEAR INTEGRATED CIRCUITS

Max. Marks: 100

Duration: 3 Hours

## PART A

*(Answer all questions; each question carries 3 marks)*

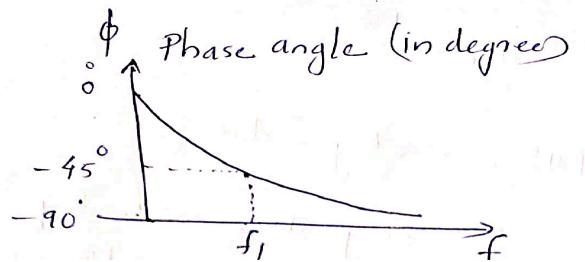

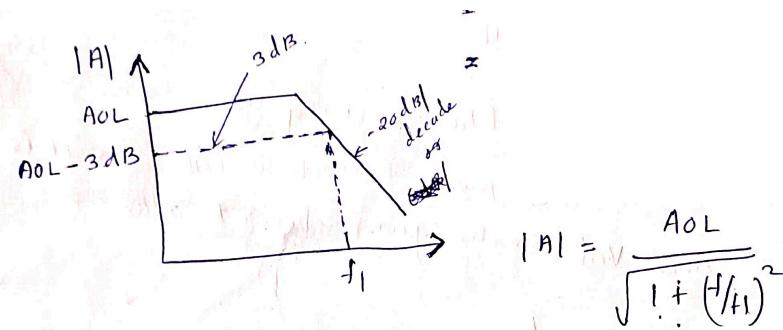

- 1 Discuss the frequency response curve of an operational amplifier. 3

Frequency Response Curve

$$\phi = -\tan^{-1}\left(\frac{f}{f_1}\right)$$

Op amps and Linear Integrated Circuits by Ramakant A Gayakward

page no 162

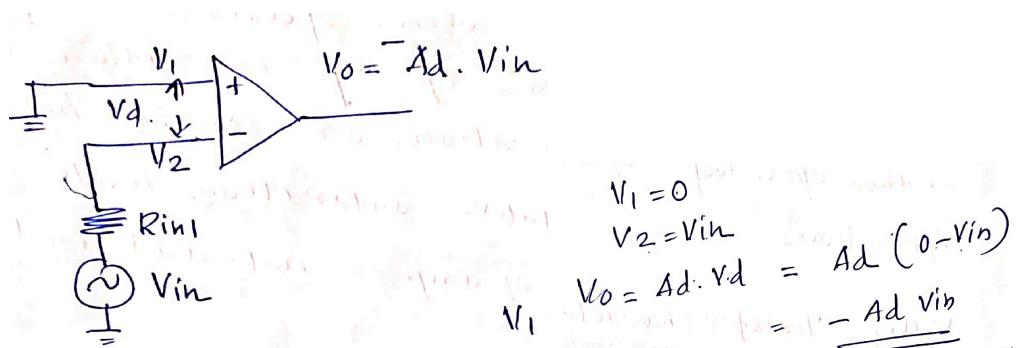

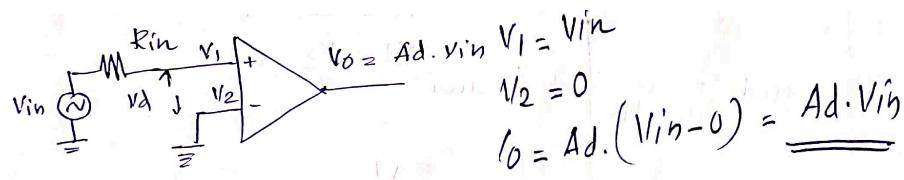

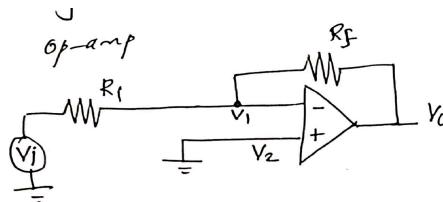

- 2 Differentiate between the open loop configurations of inverting and non-inverting amplifiers. 3

1.5 marks for inverting and 1.5 marks for non inverting configuration

**inverting**

non inverting

Op amps and Linear Integrated Circuits by Ramakant A Gayakwad page no 46

3 Discuss the concept of virtual ground in inverting amplifiers. 3

1 mark for circuit diagram + 2 marks for explanation

Virtual ground concept

Virtual ground is not real ground. The term virtual ground means that at that particular node is almost equal to ground voltage (0V). It is not physically connected to ground. This concept is very useful in analysis of op-amp circuits.

Op amps and Linear Integrated Circuits by Ramakant A Gayakwad page no 88

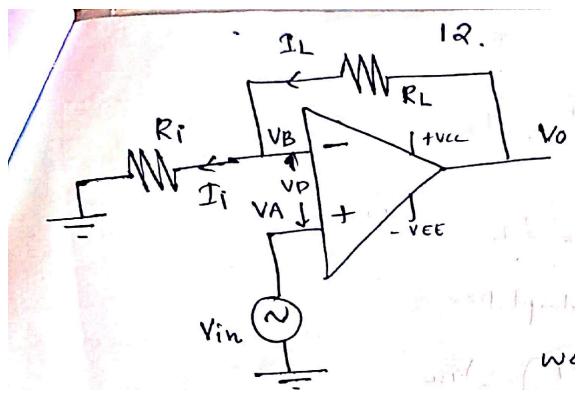

4 Explain the working of voltage to current converter with floating load. 3

1 mark for diagram + 2 marks for equations

applying virtual ground concept

$V_A = V_{in} = V_B$

so,  $\frac{V_{in}}{R_i} = I_L$   $R_i$  constant

so,  $I_L \propto V_{in}$

Op amps and Linear Integrated Circuits by Ramakant A Gayakward

page no 217

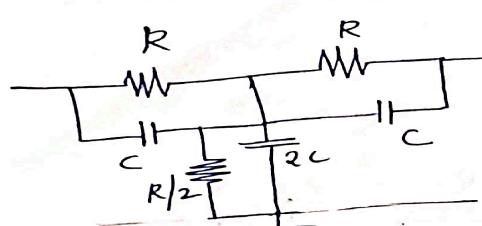

5 Design a notch filter to eliminate power supply hum (50Hz) 3

Let  $C = 0.1 \mu F$

$$f_0 = \frac{1}{2\pi\sqrt{RC}}$$

$$R = 1.083 \text{ K}$$

To prevent the RC network from loading the amplifier it is selected such  $R_1 > 10R$ .

Letting  $R = 1 \text{ K}$ ,  $R_1 = 10 \text{ K}$

$$R_F = 29R_1; R_F = 290 \text{ K}$$

Op amps and Linear Integrated Circuits by Ramakant A Gayakward

page no 274

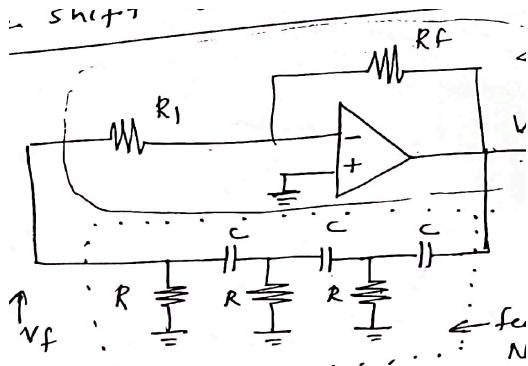

- 6 Design a RC Phase Shift Oscillator for a frequency of oscillation of 600 Hz using  $\mu\text{A } 741$ .

3

Let  $C=0.1\mu\text{F}$

$$f_o = \frac{1}{2\pi\sqrt{6RC}}$$

$$R=1.083 \text{ K}$$

To prevent the RC network from loading the amplifier it is selected such  $R_1 > 10R$ .

Letting  $R=1 \text{ K}$ ,  $R_1=10\text{K}$

$$R_F=29R_1; R_F=290\text{K}$$

Op amps and Linear Integrated Circuits by Ramakant A Gayakward page no 281

- 7 In a VCO, if input signal frequency is 10 kHz, free running frequency is 14 kHz, voltage to frequency conversion factor is 2 kHz/V, find the change in the dc control voltage, during lock.

3

Frequency Shift,  $\Delta f = 14\text{kHz} - 10\text{kHz} = 4\text{kHz}$

$$\Delta V = \frac{\Delta f}{V \text{ to } F \text{ Conversion Factor}} = 2\text{V}$$

Linear Integrated circuits by D Roy Choudhury page no 334

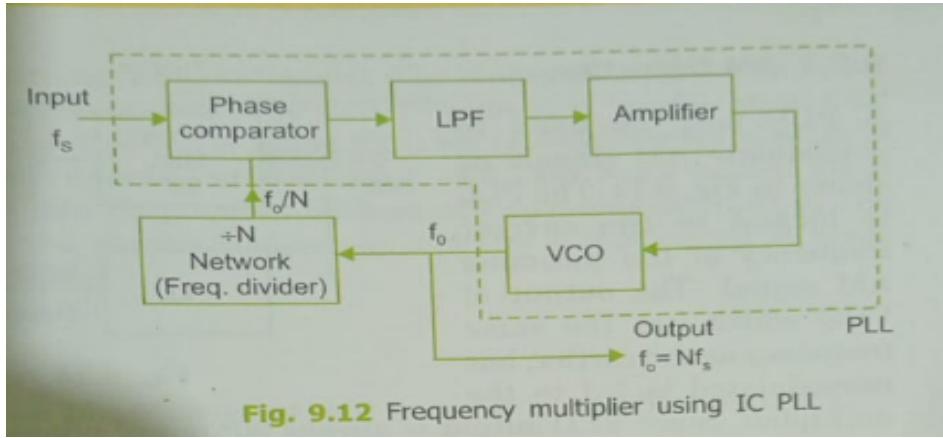

- 8 Explain how PLL can be used as a frequency multiplier. 2 mark for Diagram+1 mark for explanation.

3

Linear Integrated circuits by D Roy Choudhury page no 342

3

- 9 Find the resolution and dynamic range of a digital to analog converter, if the maximum peak to peak output voltage is 5V and the input signal is a 10 bit word.

$$\text{Step size} = \frac{5V}{1024} = 4.88 \text{mV}$$

$$\text{Dynamic Range} = \frac{5V}{4.88 \text{mV}} = 1024$$

Dynamic Range in dB = 60dB

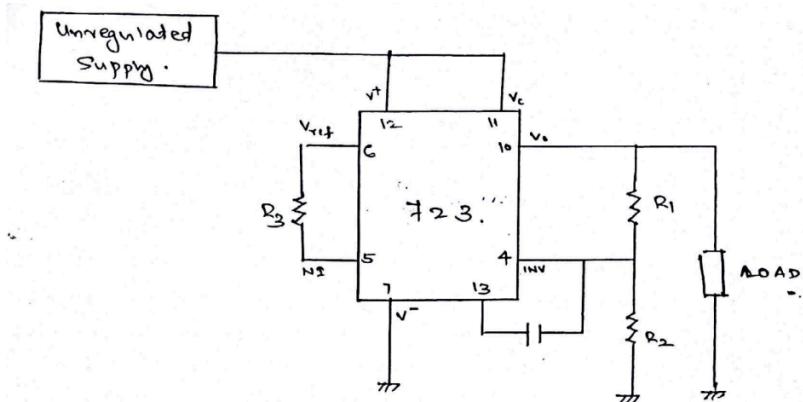

- 10 Explain how 723 IC can be used as a high voltage regulator. Give the equation for output voltage. 3

2 marks for circuit diagram+1 mark for equation

Linear Integrated circuits by D Roy Choudhury page no 252

## PART B

(Answer one full question from each module, each question carries 14 marks)

### Module -1

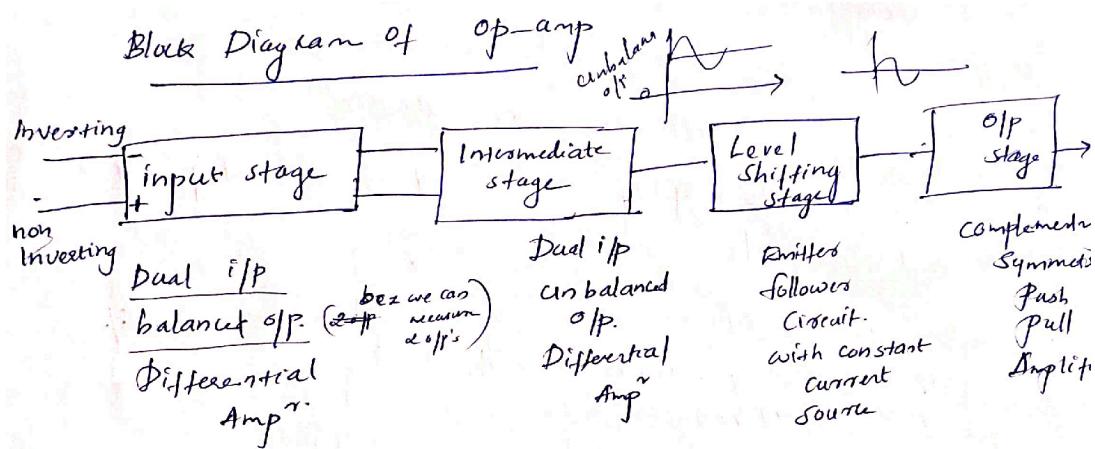

- 11 a Explain the block diagram of an operational amplifier. List out any four ideal op amp characteristics. 7

2 mark for block diagram+ 1 marks for explanation+4 marks for characteristics.

- 1) infinite voltage gain

- 2) infinite i/p impedance

- 3) zero output impedance - output can drive an infinite no. of other devices.

- 4) zero output voltage when input is zero

- 5) Bandwidth is infinite

- 6) infinite CMRR (Common Mode Rejection Ratio)

- 7) infinite slew rate [CMRR - ability of an opamp to reject noise]

Op amps and Linear Integrated Circuits by Ramakant A Gayakward page no 2, 42

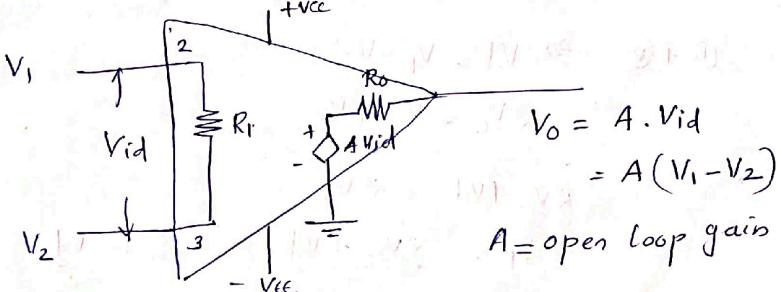

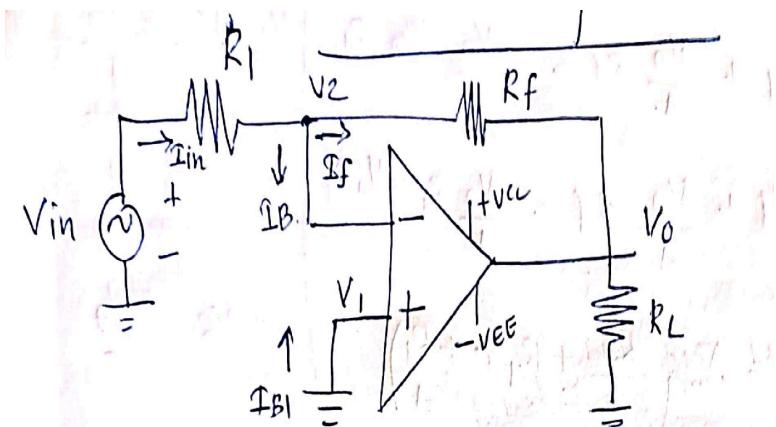

- bb) Define a) Power Supply Rejection Ratio b) Input Bias Current of an op amp. Draw

the equivalent circuit of an opamp.

2 mark for Power Supply Rejection Ratio and 2 marks for Input Bias Current and

3 marks for equivalent circuit

Supply Voltage Reduction Ratio (SVRR) or Power supply Rejection Ratio (PSRR)

It is the ratio of change in op-amps input offset voltage to the change in supply voltage.

$$SVRR = \frac{\Delta V_{IO}}{\Delta V}$$

For 741 opamp SVRR is  $\approx 6.31 \text{ mV/V}$

input bias current  $I_B$

$I_B$  is the Average of the current flow in the Inverting and non-inverting input terminals of the op-amp

$$I_B = \frac{I_{B1} + I_{B2}}{2}$$

maximum value for 741C is 500nA

Equivalent circuit diagram of op-amp

Op amps and Linear Integrated Circuits by Ramakant A Gayakwad page no 37, 122, 43

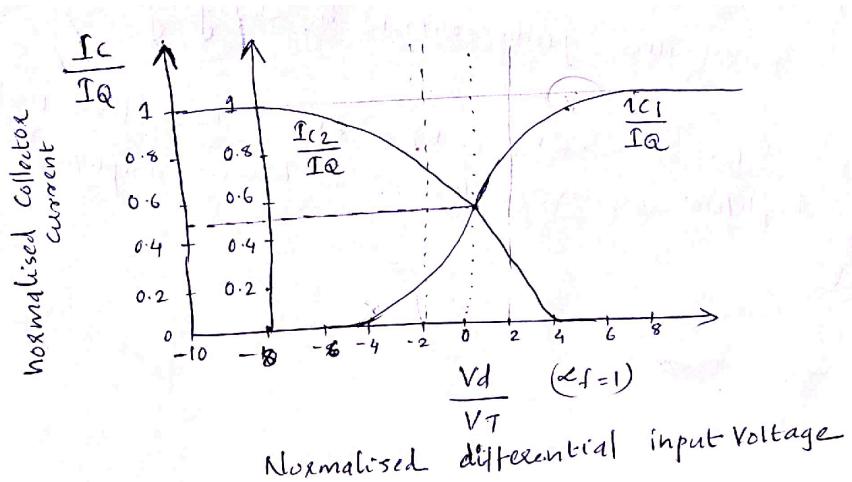

12 a Discuss the transfer characteristics of differential amplifiers.

7

- ) 2 marks for graph + 3 marks for equations + 2 marks for explanations from the graph.

$$i_{C1} = \frac{k_f \frac{T_0}{I_Q}}{1 + e^{\frac{-Vd}{V_T}}}$$

$$i_{C2} = k_f \frac{\frac{T_0}{I_Q}}{1 + e^{\frac{+Vd}{V_T}}}$$

a) for  $Vd > 4V_T$   $i_{C1} = k_f \frac{T_0}{I_Q}$  and  $i_{C2} = 0$

$$V_{O1} = V_{CC} - k_f \frac{T_0}{I_Q} R_C$$

$$V_{O2} \approx V_{CC}$$

By proper value of  $R_C$ ,  $V_{O1}$  can be made zero or

b) for  $V_d < -4V_T$

$$i_{C1} = 0, \quad i_{C2} = 24I_Q$$

$$V_{D1} = V_{CC}$$

$V_{D2}$  is small

$4V_T < V_d < -4V_T$ , This can be operated as switch.

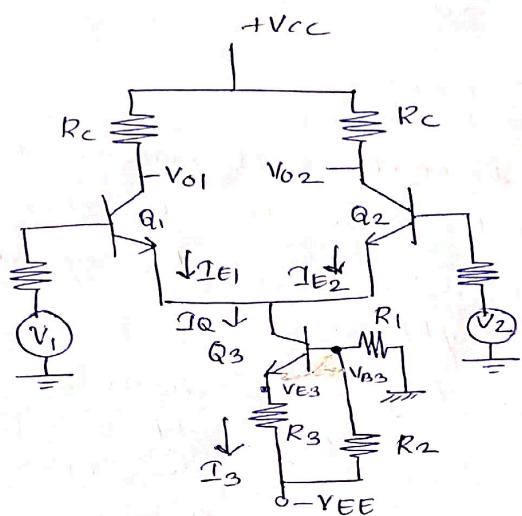

- b) Explain how differential amplifier using constant current bias improves CMRR.

2 marks for circuit diagram + 2.5 marks for equations + 2.5 marks for explanation.

7

$$\text{we have, } I_3 = \frac{V_{E3} - (-V_{EE})}{R_3} \\ = \frac{V_{E3} + V_{EE}}{R_3} \quad \text{--- (1)}$$

$$V_{B3} = -V_{EE} \cdot \frac{R_1}{R_1 + R_2} \quad \text{--- (2)}$$

$$V_{BE3} = V_{B3} - V_{E3} \quad \text{--- (3)}$$

$$V_{BE3} = -V_{EE} \cdot \frac{R_1}{R_1 + R_2} - V_{E3} \\ V_{E3} = -V_{EE} \cdot \frac{R_1}{R_1 + R_2} - V_{BE3}.$$

sub.  $V_{E3}$  in (1)

$$I_3 = -V_{EE} \cdot \frac{R_1}{R_1 + R_2} - V_{BE3} + V_{EE} \\ \frac{-V_{EE} \cdot \frac{R_1}{R_1 + R_2} - V_{BE3} + V_{EE}}{R_3} \quad \text{--- (4)}$$

$$I_Q \approx I_3$$

$$I_Q = I_{E1} + I_{E2}$$

if  $I_{E1} \approx I_{E2}$

$$I_Q = 2I_{E1} \quad \text{sub. in (4)}$$

$$2I_{E1} = -V_{EE} \cdot \frac{R_1}{R_1 + R_2} - V_{BE3} + V_{EE} \\ \frac{-V_{EE} \cdot \frac{R_1}{R_1 + R_2} - V_{BE3} + V_{EE}}{R_3}$$

$$I_{E1} = -V_{EE} \cdot \frac{R_1}{R_1 + R_2} - V_{BE3} + V_{EE} \\ \frac{-V_{EE} \cdot \frac{R_1}{R_1 + R_2} - V_{BE3} + V_{EE}}{2R_3}$$

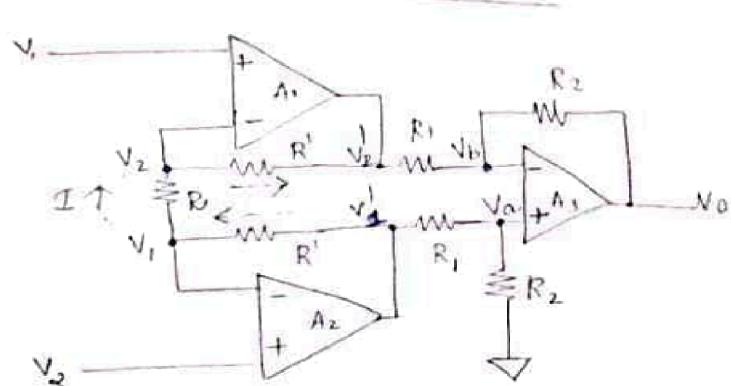

- 13 a) Derive the equation for the output voltage for an instrumentation amplifier using 3 op amps.

7

2 marks for circuit diagram and 5 marks for equation derivation

according to superposition theorem,

$$V_o = V_{i1} - V_{i2} = V_{oa} + V_{ob} \\ = \left[ 1 + \frac{R_2}{R_1} \right] V_{i2}$$

$$V_{ob} = V_o \text{ due to } V_{ob} \quad V_{ob} = -\frac{R_2}{R_1} V_{i2}$$

$$V_{oa} = \left[ 1 + \frac{R_2}{R_1} \right] \left[ \frac{V_{i1} R_2}{R_1 + R_2} \right]$$

$$V_o = V_{oa} + V_{ob} \\ = \left[ 1 + \frac{R_2}{R_1} \right] \left[ \frac{V_{i1} R_2}{R_1 + R_2} \right] - \frac{R_2}{R_1} V_{i2}$$

$$= V_{i1} \frac{R_2}{R_1} - \frac{R_2}{R_1} V_{i2}$$

$$V_o = \frac{R_2}{R_1} [V_{i1} - V_{i2}] \quad \text{--- (1)}$$

If  $V_{i1} \neq V_{i2}$  then current flowing in resistors

$$V_{i1}' = IR' + V_{i1} \quad \left. \begin{array}{l} \\ \end{array} \right\} \text{is (1)} \quad I = \frac{V_{i1} - V_{i2}}{R}$$

$$V_{i2}' = -IR' + V_{i2}$$

$$V_o = \frac{R_2}{R_1} [IR' + V_{i1} - [-IR' + V_{i2}]]$$

$$= \frac{R_2}{R_1} \left[ \frac{2(V_{i1} - V_{i2})}{R} R' + V_{i1} + \left( \frac{V_{i1} - V_{i2}}{R} \right) R' \right]$$

$$V_o = \frac{R_2}{R_1} \left[ \frac{2(V_{i1} - V_{i2})}{R} R' + V_{i1} - V_{i2} \right]$$

$$V_o = \underline{\underline{\frac{R_2}{R_1} \left[ \frac{2R'}{R} + 1 \right] (V_{i1} - V_{i2})}}$$

Gain of instrumentation amplifier,

$$\frac{V_o}{V_{i1} - V_{i2}} = \frac{R_2}{R_1} \left[ \frac{2R'}{R} + 1 \right] (\underline{\underline{V_{i1} - V_{i2}}})$$

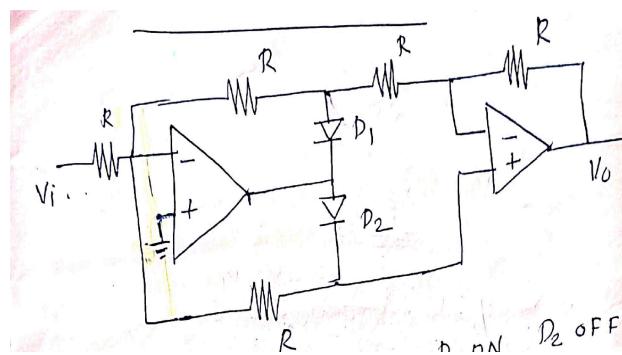

b) Explain the working of full wave precision rectifier.

7

2 marks for circuit diagram+2.5 marks each for explanation during positive half cycle and negative half cycle.

$$\frac{V_i}{R} + \frac{V}{R} + \frac{V}{2R} = 0$$

$$-\frac{V_i}{R} = \frac{3V}{2R}$$

$$V = \frac{-2V_i}{3}$$

$$\therefore V_o = \frac{3}{2} \cdot V = \frac{3}{2} \cdot \frac{-2V_i}{3} \cdot V_i$$

$$\boxed{V_o = -V_i} \quad \begin{matrix} \text{for negative input} \\ (-V_i) \\ \text{Output is positive} \end{matrix}$$

- 14 a) Derive the equation for closed loop voltage gain, input and output resistance of voltage shunt feedback amplifier. 7

1 mark for circuit diagram+2 marks for derivation of voltage gain+2 marks for derivation of input resistance+2 marks for derivation of output resistance

$$A_f = \frac{-kA}{1+AB}$$

$$k = R_f / R_1 \cdot R_2$$

if  $AB \gg 1$

$$1+AB = AB$$

$$A_f = \frac{-k \cdot A}{AB} = \frac{-k}{B} = \frac{-R_f}{R_1 + R_f} = \underline{\underline{\frac{-R_f}{R_1 + R_f}}}$$

Since  $R_i$  and  $A$  are large

$$\frac{R_f}{1+A} \parallel R_i \approx 0$$

$$R_{if} = R_i \text{ (ideal)}$$

$$R_{of} = \frac{R_o}{1+AB}$$

Op amps and Linear Integrated Circuits by Ramakant A Gayakward page no 86

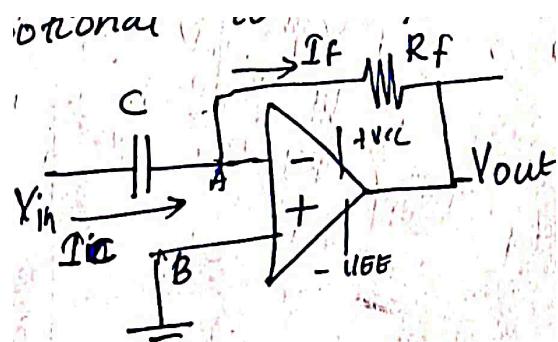

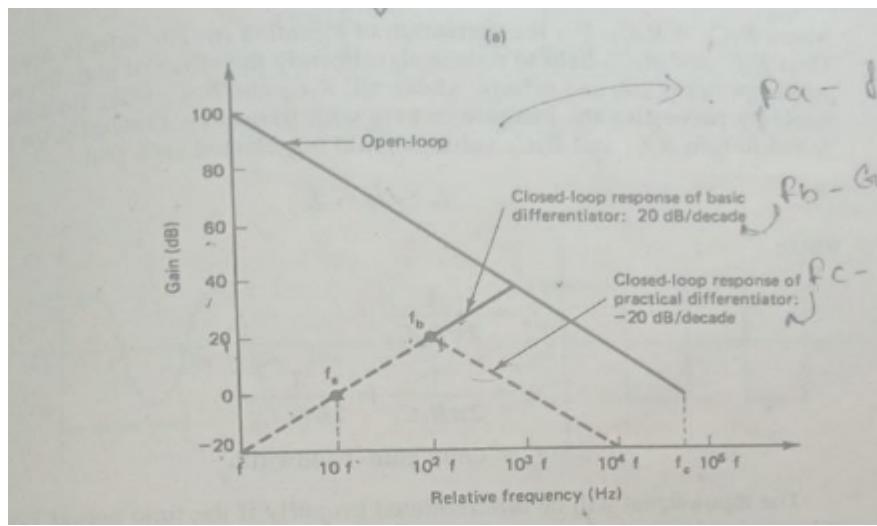

- b) Derive the equation for output voltage for a differentiator. Explain the frequency response of differentiator. 7

2 mark for circuit diagram +2 marks for derivation +3 marks for frequency response.

Apply KCL at node A

$$I_{in} = I_f$$

$$C \cdot \frac{d}{dt} V_{in} = \frac{0 - V_{out}}{R_f}$$

$$V_{out} = -R_f \cdot C \frac{d}{dt} V_{in}$$

$$\left. \begin{aligned} i &= \frac{dQ}{dt} \\ Q &= CV \\ i &= \frac{dC}{dt} \end{aligned} \right\}$$

Op amps and Linear Integrated Circuits by Ramakant A Gayakward page no 234

### Module -3

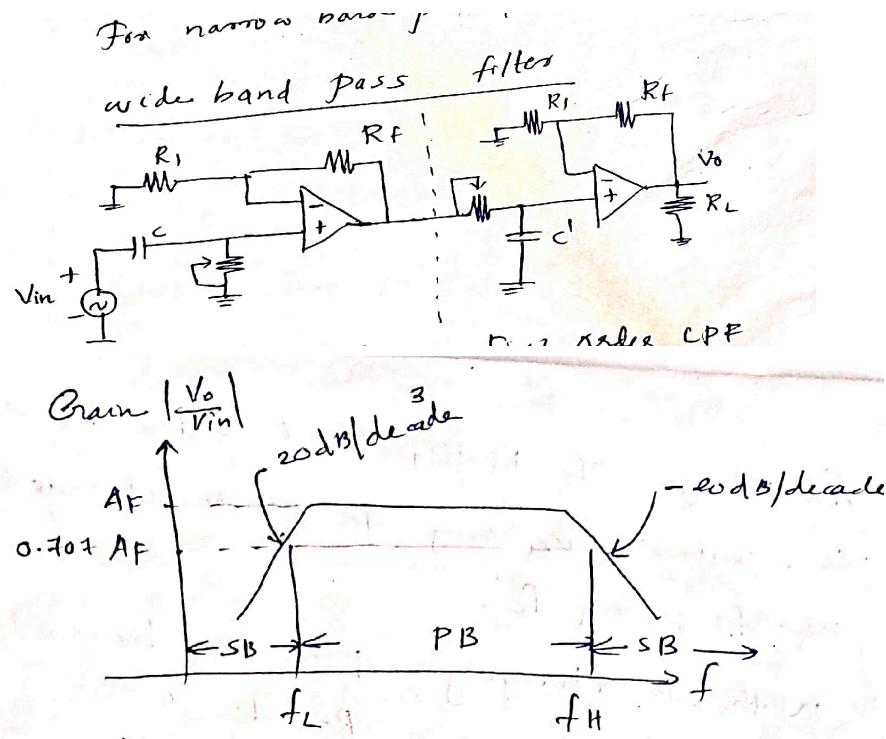

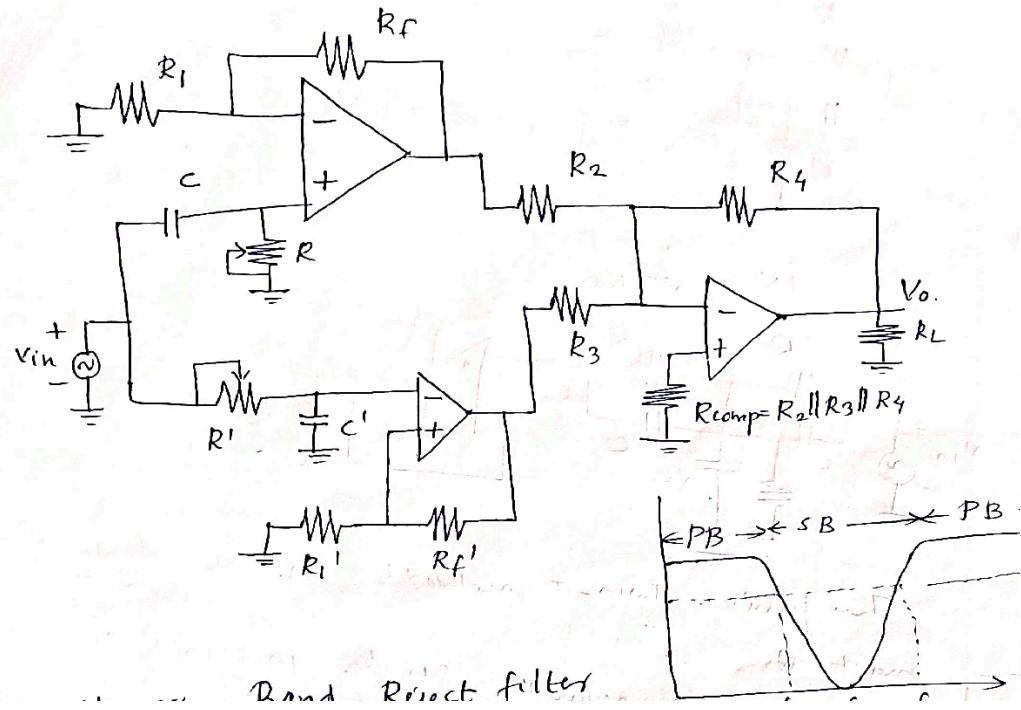

- 15 a) Illustrate how the following filters can be implemented using opamp. Draw their frequency response. 7

1) Band Pass Filter      2) Band Reject Filter.

2.5 marks each can be given if the circuit diagram is drawn. 1 mark each can be given for frequency response (3.5\*2)

Op amps and Linear Integrated Circuits by Ramakant A Gayakwad page no 268,274

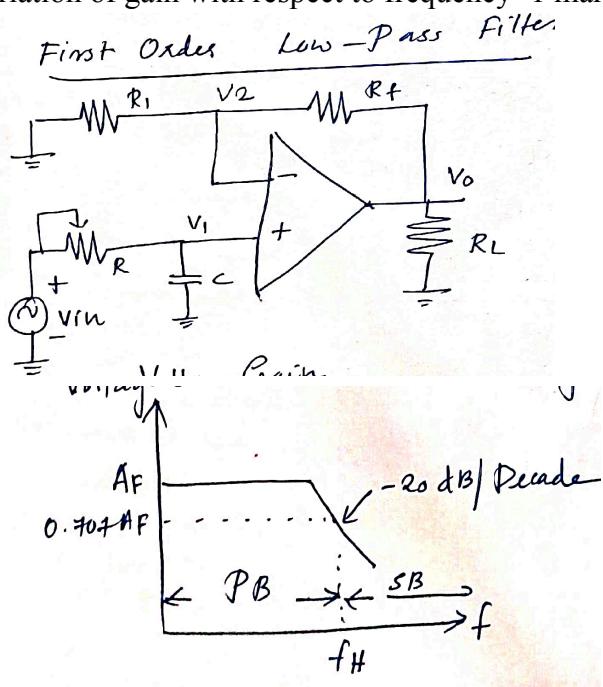

- b) Derive the equation for voltage gain for first order low pass filter. Using the gain magnitude equation illustrate the variation of gain with respect to frequency. What is frequency scaling?

7

2 marks for circuit diagram+ 2 marks for derivation of voltage gain +2 marks for variation of gain with respect to frequency+1 mark for frequency scaling

$$\text{magnitude } \left| \frac{V_o}{V_{in}} \right| = \frac{A_f}{\sqrt{1 + (f/f_H)^2}}$$

$$\text{phase } \phi = -90^\circ - \tan^{-1}(f/f_H)$$

Frequency scaling is the process of converting original cut off frequency to a new frequency

Op amps and Linear Integrated Circuits by Ramakant A Gayakward page no 253,255,256

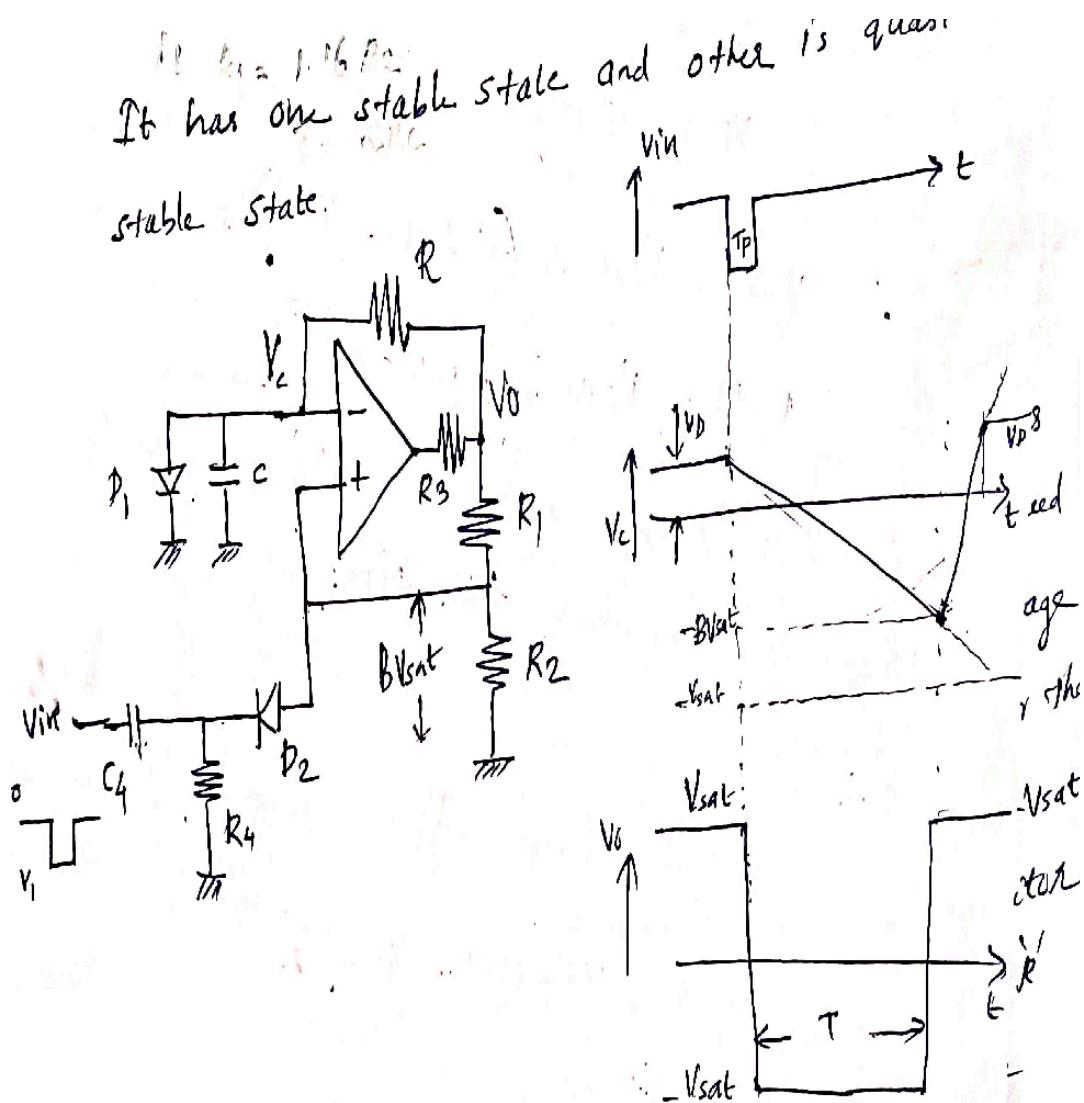

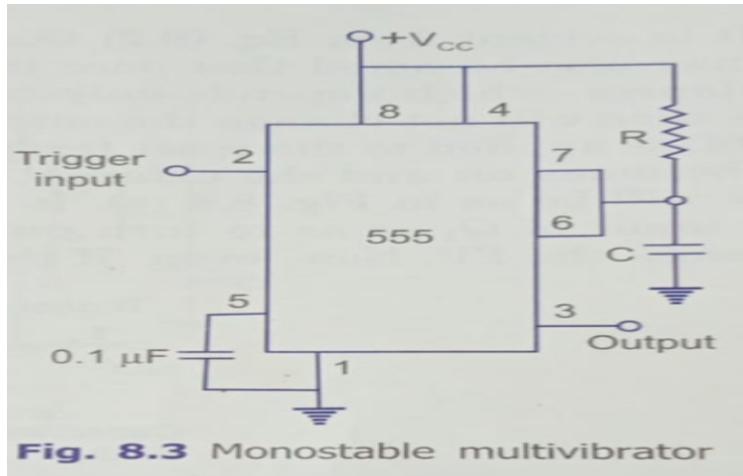

- 16 a) Explain the working of a monostable multivibrator using 741. Derive the equation for pulse width.

2 marks for circuit diagram+2 marks for explanation+3 marks for derivation of pulse width.

Linear Integrated circuits by D Roy Choudhury page no 218

$$\overline{T = 0.69 RC}$$

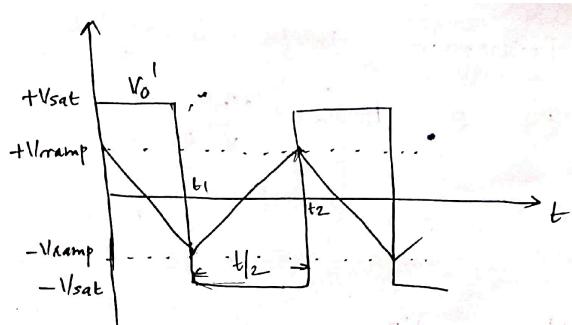

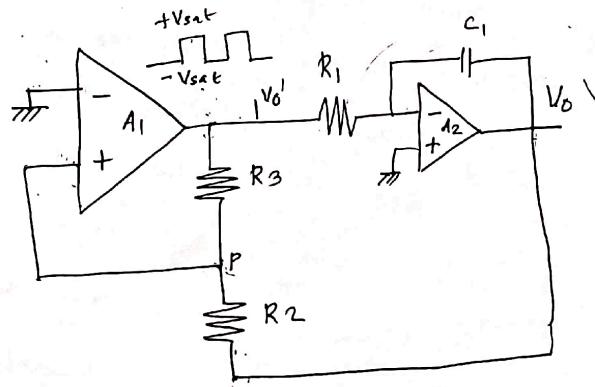

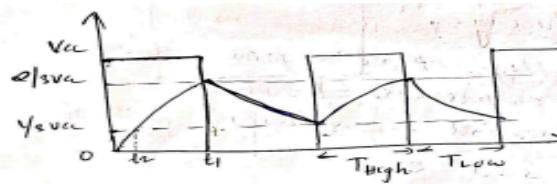

b) Explain the working of triangular wave generator. Derive the equation for frequency of oscillation. 7

2 marks for diagram+2 marks for explanation+3 marks for derivation of frequency of oscillation.

During the time when the output of A1 is at  $-V_{sat}$ , the output of A2 increases in the pos direction.

At instant  $t=t_2$ , the voltage at point 'P' becomes just above 0V, thereby switching the output of A1 from  $-V_{sat}$  to  $+V_{sat}$ . This cycle repeats and generates the triangular waveform.

O/P of Integrator

$$V_o = -\frac{1}{R_C} \int v_i dt$$

$$\begin{aligned} V_o(p-p) &= -\frac{1}{R_1 C_1} \int (-V_{sat}) dt \\ &= \frac{V_{sat}}{R_1 C_1} \int dt \\ &\approx \frac{V_{sat}}{R_1 C_1} (T/2 - 0) \end{aligned}$$

$$V_o(p-p) = \frac{V_{sat}}{R_1 C_1} T/2$$

$$\frac{2R_2}{R_3} V_{sat} = \frac{V_{sat}}{R_1 C_1} \cdot \frac{T}{2} \quad \text{from eqn ③}$$

$$\frac{2R_2}{R_3} = \frac{T}{2R_1 C_1}$$

$$T = \frac{4 R_1 R_2 C_1}{R_3}$$

$$f_o = \frac{1}{T} = \frac{R_3}{4 R_1 R_2 C_1}$$

Op amps and Linear Integrated Circuits by Ramakant A Gayakward page no 289

#### Module -4

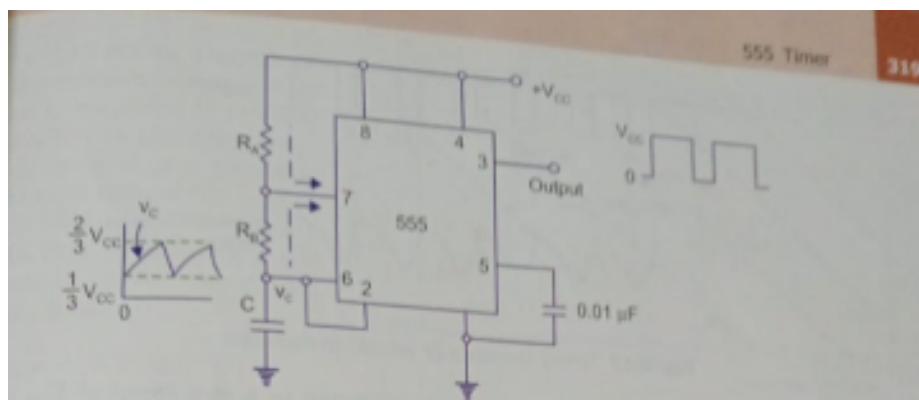

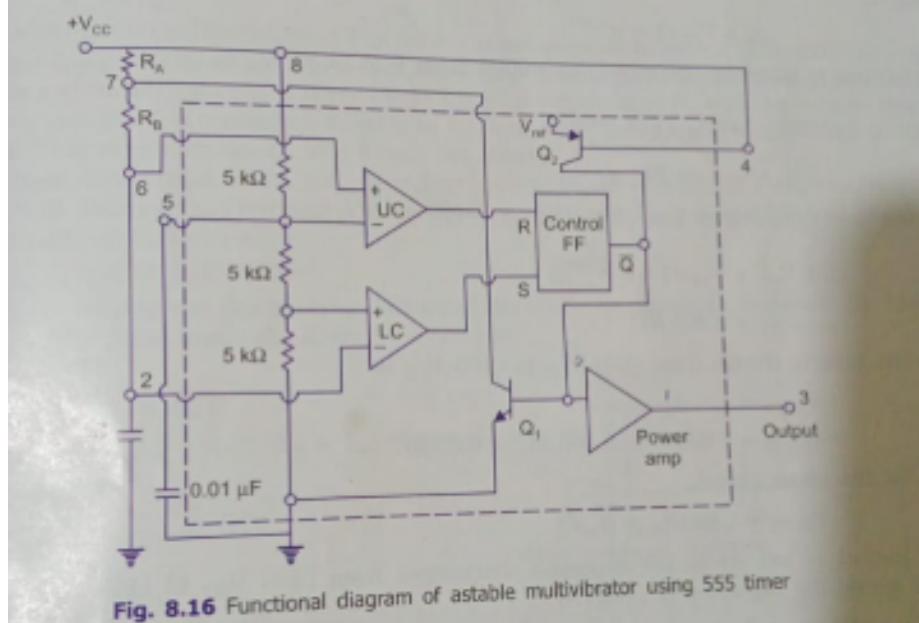

- 17 a) Explain the astable operation of 555 timer I.C. Derive the equation for frequency of oscillation. 7

2 marks for functional block diagram+2 marks for explanation+3 marks for derivation of frequency of oscillation

Fig. 8.15 Astable multivibrator using 555 timer

Fig. 8.16 Functional diagram of astable multivibrator using 555 timer

An astable multivibrator, often called a free-running multivibrator, is a rectangular-wave-generating circuit. Unlike the monostable multivibrator, this circuit does not require an external trigger to change the state of the output, hence the name free-running. However, the time during which the output is either high or low is determined by two resistors and a capacitor, which are externally connected to the 555 timer.

When the power supply  $V_{cc}$  is connected, the external timing capacitor  $C$  charges towards  $V_{cc}$  through  $R_A$  and  $R_B$  with time constant  $(R_A+R_B)C$ . During this time, output (pin 3) is high (equals  $V_{cc}$ ) as Reset  $R=0$ , Set  $S=1$  and this combination makes  $\bar{Q}=0$  which has unclamped the timing capacitor  $C$ .

When the capacitor voltage is just greater than  $2/3 V_{cc}$ , the upper comparator triggers the control flip-flop so that  $R=1, S=0$ ,  $\bar{Q}=1$  and  $Q=0$ . The output of astable is low. This, in turn, makes transistor  $Q_1$  on and capacitor starts discharging towards ground through  $R_B$  and transistor  $Q_1$  with a time constant  $R_B C$ . During the discharge of the timing capacitor, as it is just less than  $V_{cc}/3$ , the lower comparator is triggered and at this stage  $S=1, R=0$ , which turns  $\bar{Q}=0$ . The output of astable is high. Now  $\bar{Q}=0$  unclamps the external timing capacitor. The capacitor is thus periodically charged and discharged between and respectively. Then the cycle repeats.

$t_{\text{high}} \rightarrow$  Time required for capacitor to charge

from  $\frac{1}{3} V_{cc}$  to  $\frac{2}{3} V_{cc}$ .

The capacitor voltage for a low pass RC circuit

so if  $V_{cc}$  is

$V_c = V_{cc} \cdot (1 - e^{-t/RC})$

$t_1$  is the time taken for capacitor to charge

from  $0 \rightarrow \frac{2}{3} V_{cc}$

$$\frac{2}{3} V_{cc} = V_{cc} \cdot (1 - e^{-t_1/RC})$$

$$\frac{2}{3} = 1 - e^{-t_1/RC}$$

$$t_1 = \dots 1.09 RC \quad \text{--- (1)}$$

$t_2$  is the time to charge from  $0$  to  $\frac{1}{3} V_{cc}$

$\frac{1}{3} V_{cc} = V_{cc} \cdot (1 - e^{-t_2/RC})$

$$\frac{1}{3} = 1 - e^{-t_2/RC}$$

$$t_2 = 0.405 RC$$

$$\begin{aligned}

T_{\text{high}} &= t_1 - t_2 \\

&= 1.09 RC - 0.405 RC \\

&= \underline{0.69 RC}

\end{aligned}$$

Linear Integrated circuits by D Roy Choudhury page no 318

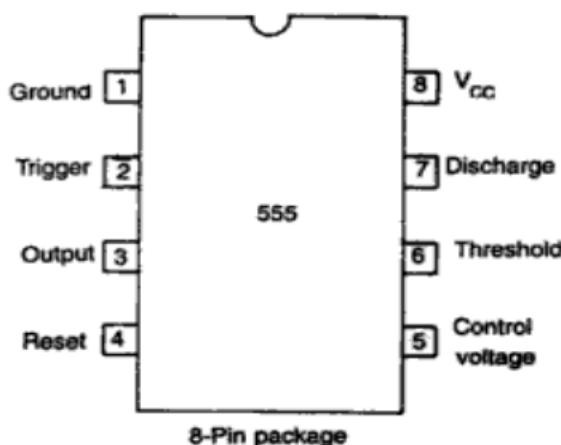

- b) Draw the pin diagram of 555 timer I.C. Design a monostable multivibrator using 555 timer I.C for a pulse width of 1 ms. Draw the circuit diagram. 7

3 marks for pin diagram +3 marks for design +1 mark for circuit diagram.

Fig. 8.1 Pin diagram

$$T_p = 1.1 RC$$

Let  $C = 0.1 \mu F$

$$R = 8.2 K\Omega$$

$$C_1 = 0.01 \mu F$$

Linear Integrated Circuits by D Roy Choudhury page no 311,312

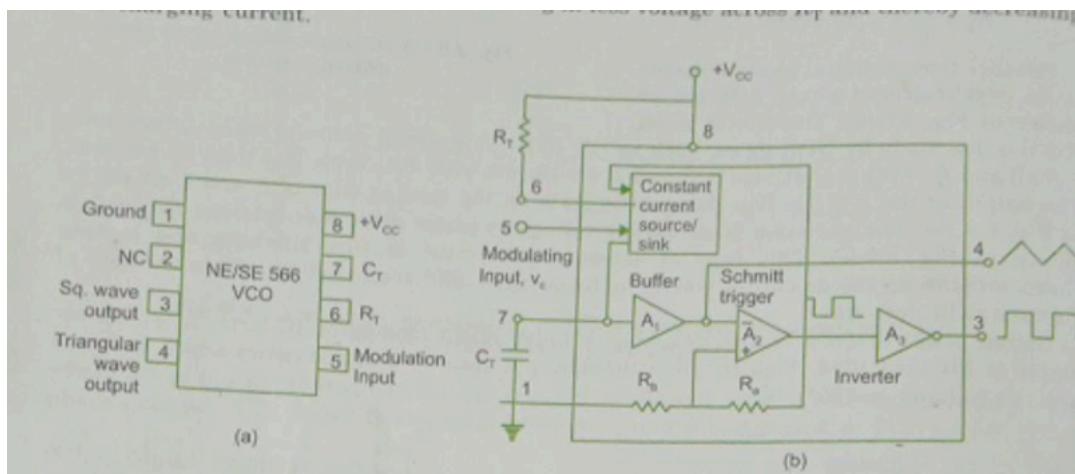

- 18 a) Explain the block diagram of Voltage Controlled Oscillator. Derive the equation for frequency of oscillation. 7

2 marks for block diagram+2 marks for working +3 marks for derivation

we know that,  $q = CV$

$$i = \frac{dq}{dt}$$

$$i = \frac{dCV}{dt} = C \cdot \frac{dV}{dt}$$

$$\frac{i}{C_T} = \frac{dV}{dt} = \frac{\Delta V}{\Delta T}$$

$$\frac{i}{C_T} = \frac{0.5V_{CC} - 0.25V_{CC}}{\Delta T}$$

$$\frac{i}{C_T} = \frac{0.25V_{CC}}{\Delta T}$$

$$\Delta T = \frac{0.25V_{CC} \cdot C_T}{i}$$

Total time period of the rectangular waveforms.  $\Delta T + \Delta T = 2\Delta T$

$$f_0 = \frac{1}{2\Delta T} = \frac{1}{2} \left( \frac{i}{0.25V_{CC} \cdot C_T} \right)$$

$$f_0 = \frac{i}{0.5V_{CC} \cdot C_T}$$

$$i = \frac{V_{CC} - V_C}{R_T}$$

$$f_0 = \frac{2(V_{CC} - V_C)}{C_T R_T V_{CC}} \quad \text{--- (A)}$$

Linear Integrated circuits by D Roy Choudhury page no 334

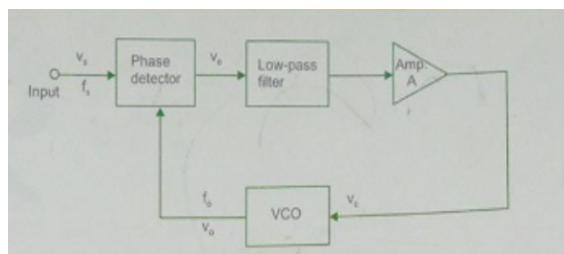

- b) Using closed loop analysis, find the transfer function of the Phase Locked Loop. 7

3 marks for block diagram+ 4 marks for derivation

Linear Integrated circuits by D Roy Choudhury page no 327,332

## Module -5

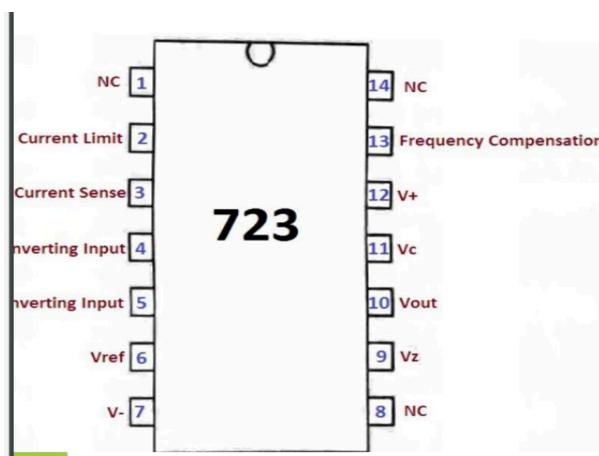

- 19 a) Discuss the functional block diagram of 723 regulators. Draw the pin configuration 7 of I.C 723.

3 marks for functional block diagram+ 2 marks for explanation+2 marks for pin configuration of I.C 723.

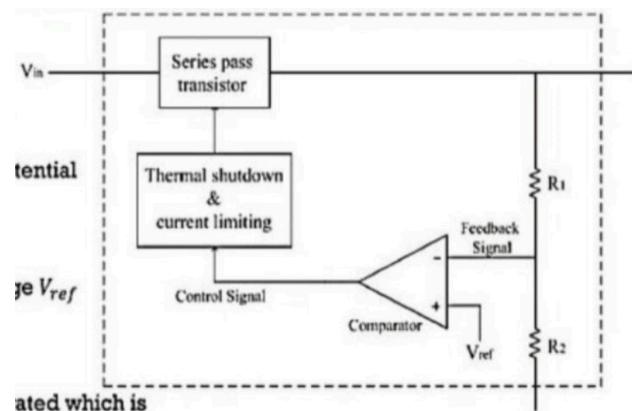

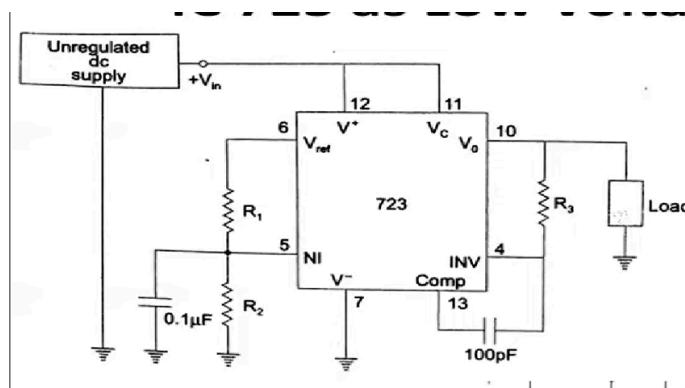

- b) Using functional diagram, explain how regulation is achieved in low voltage regulators using 723. Draw the circuit diagram of low voltage regulator using 723 IC

2 marks for Functional diagram+3 marks for explanation+2 marks for circuit diagram.

Linear Integrated circuits by D Roy Choudhury page no 251

- 20 a) Explain the working of flash type ADC.

3 marks for diagram+4 marks for explanation

7

Linear Integrated circuits by D Roy Choudhury page no 359

- b) An 8 bit Analog to Digital Converter accepts an input voltage signal of range 0 to 10V. What is the minimum value of the input voltage required to generate a change of 1 LSB.? Determine the input voltage required to generate all 1's at the output?

7

What is the digital output for an input voltage of 4.8 V

$$1LSB = \frac{10V}{2^8} = 39.1mV \quad (2 \text{ marks})$$

Maximum input voltage that can cause all 1's at the output =  $10V - 39.1mV = 9.961V$

(2 marks)

The digital output for an applied input voltage of 4.8 V is given by  $D = \frac{4.8V}{39.1mV} = 123$

Converting to binary, the digital output is 01111011 (3 marks)