# **Counters**

A special type of sequential circuit used to count the pulse is known as a counter, or a collection of flip flops where the clock signal is applied is known as counters.

The counter is one of the widest applications of the flip flop. Based on the clock pulse, the output of the counter contains a predefined state. The number of the pulse can be counted using the output of the counter.

There are the following types of counters:

- o Asynchronous Counters

- o Synchronous Counters

The term **asynchronous** refers to events that do not have a fixed time relationship with each other and, generally, do not occur at the same time. An **asynchronous counter** is one in which the flip-flops (FF) within the counter do not change states at exactly the same time because they do not have a common clock pulse.

### A 2-Bit Asynchronous Binary Counter

Figure 8–1 shows a 2-bit counter connected for asynchronous operation. Notice that the clock (CLK) is applied to the clock input (C) of *only* the first flop-flop, FF0, which is always the least significant bit (LSB). The second flip-flop, FF1, is triggered by the  $\overline{Q}_0$  output of FF0. FF0 changes state at the positive-going edge of each clock pulse, but FF1 changes only when triggered by a positive-going transition of the  $\overline{Q}_0$  output of FF0. Because of the inherent propagation delay time through a flip-flop, a transition of the input clock pulse (CLK) and a transition of the  $\overline{Q}_0$  output of FF0 can never occur at exactly the same time. Therefore, the two flip-flops are never simultaneously triggered, so the counter operation is asynchronous.

**The Timing Diagram** Let's examine the basic operation of the asynchronous counter of Figure 8–1 by applying four clock pulses to FFO and observing the Q output of each flipflop. Figure 8–2 illustrates the changes in the state of the flip-flop outputs in response to the clock pulses. Both flip-flops are connected for toggle operation (J=1,K=1) and are assumed to be initially RESET (Q LOW).

| CLOCK PULSE  | $Q_1$ | $Q_0$ |

|--------------|-------|-------|

| Initially    | 0     | 0     |

| 1            | 0     | 1     |

| 2            | 1     | 0     |

| 3            | 1     | 1     |

| 4 (recycles) | 0     | 0     |

#### **8–2** SYNCHRONOUS COUNTER OPERATION

The term **synchronous** refers to events that have a fixed time relationship with each other. A **synchronous counter** is one in which all the flip-flops in the counter are clocked at the same time by a common clock pulse.

### A 2-Bit Synchronous Binary Counter

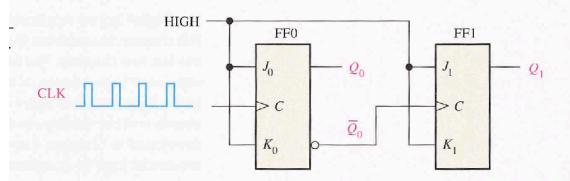

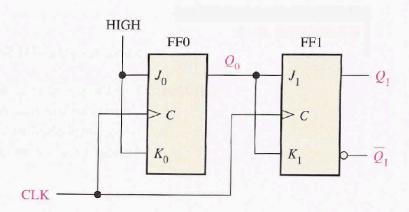

Figure 8–11 shows a 2-bit synchronous binary counter. Notice that an arrangement different from that for the asynchronous counter must be used for the  $J_1$  and  $K_1$  inputs of FF1 in order to achieve a binary sequence.

## FIGURE 8-11

A 2-bit synchronous binary counter.

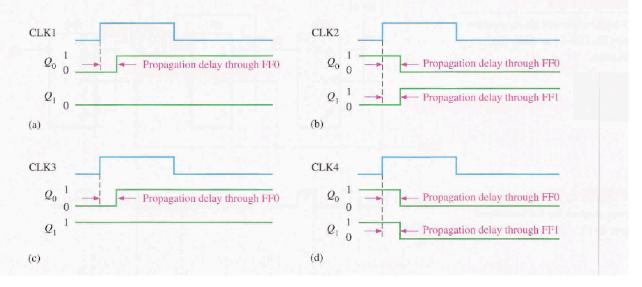

The operation of this synchronous counter is as follows: First, assume that the counter is initially in the binary 0 state; that is, both flip-flops are RESET. When the positive edge of the first clock pulse is applied, FF0 will toggle and  $Q_0$  will therefore go HIGH. What happens to FF1 at the positive-going edge of CLK1? To find out, let's look at the input conditions of FF1. Inputs  $J_1$  and  $K_1$  are both LOW because  $Q_0$ , to which they are connected, has not yet gone HIGH. Remember, there is a propagation delay from the triggering edge of the clock pulse until the Q output actually makes a transition. So, J=0 and K=0 when the leading edge of the first clock pulse is applied. This is a no-change condition, and therefore FF1 does not change state. A timing detail of this portion of the counter operation is shown in Figure 8–12(a).

The clock input goes to each flip-flop in a synchronous counter.

After CLK1,  $Q_0 = 1$  and  $Q_1 = 0$  (which is the binary 1 state). When the leading edge of CLK2 occurs, FF0 will toggle and  $Q_0$  will go LOW. Since FF1 has a HIGH ( $Q_0 = 1$ ) on its  $J_1$  and  $K_1$  inputs at the triggering edge of this clock pulse, the flip-flop toggles and  $Q_1$  goes HIGH. Thus, after CLK2,  $Q_0 = 0$  and  $Q_1 = 1$  (which is a binary 2 state). The timing detail for this condition is shown in Figure 8–12(b).

When the leading edge of CLK3 occurs, FF0 again toggles to the SET state  $(Q_0 = 1)$ , and FF1 remains SET  $(Q_1 = 1)$  because its  $J_1$  and  $K_1$  inputs are both LOW  $(Q_0 = 0)$ . After this triggering edge,  $Q_0 = 1$  and  $Q_1 = 1$  (which is a binary 3 state). The timing detail is shown in Figure 8–12(c).

Finally, at the leading edge of CLK4,  $Q_0$  and  $Q_1$  go LOW because they both have a toggle condition on their J and K inputs. The timing detail is shown in Figure 8–12(d). The counter has now recycled to its original state, binary 0.

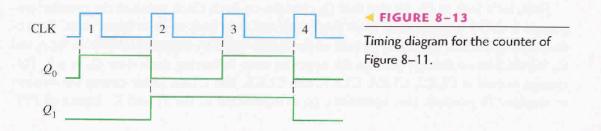

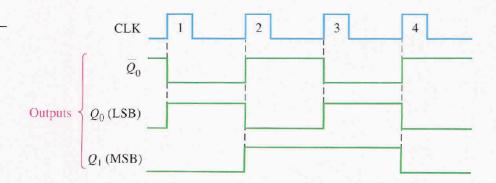

The complete timing diagram for the counter in Figure 8–11 is shown in Figure 8–13. Notice that all the waveform transitions appear coincident; that is, the propagation delays are not indicated. Although the delays are an important factor in the synchronous counter operation, in an overall timing diagram they are normally omitted for simplicity. Major waveform