# Super-pipelined Processor

Angela Zou(az292), Andrew Lin(yl656), Zoe Du(jd963)

## **Table of Content**

| 1. | Introduction                                                                 | 3  |

|----|------------------------------------------------------------------------------|----|

| 2. | FO4 Spice Simulation                                                         | 5  |

| 3. | Baseline Design                                                              | 8  |

|    | 3.1 Datapath                                                                 | 8  |

|    | 3.2 Control Unit                                                             | 10 |

|    | 3.3 Implementation Details                                                   | 10 |

| 4. | Alternative Design                                                           | 12 |

|    | 4.1 Splitting X Stage into X0/X1                                             | 14 |

|    | 4.1.1 Stalling Without Additional Bypassing                                  | 14 |

|    | 4.1.2 Bypassing in X0/X1 Stage                                               | 19 |

|    | 4.2 Splitting D Stage into D0/D1                                             | 23 |

|    | 4.2.1 Register-based Design                                                  | 23 |

|    | 4.2.2 Modification Related to the Instruction Memory Drop Unit               | 26 |

|    | 4.2.3 Potential Latch-based Design                                           | 31 |

|    | 4.3 Dealing with PC Redirection                                              | 32 |

|    | 4.3.1 Branch Resolution in Stage M                                           | 32 |

|    | 4.3.2 JAL in D0 Stage                                                        | 37 |

|    | 4.3.3 Branch Target Buffer                                                   | 41 |

| 5. | Testing Strategy                                                             | 42 |

|    | 5.1 Baseline Testing                                                         | 42 |

|    | 5.2 Alternative Design Testing                                               | 43 |

|    | 5.2.1 Testing Methodology                                                    | 43 |

|    | 5.2.2 Testing Separated ALUs                                                 | 44 |

|    | 5.2.3 Testing the X0/X1 Splitted Processor Without Additional Bypassing      | 45 |

|    | 5.2.4 Testing the Bypassing X0/X1 Splitted Processor                         | 48 |

|    | 5.2.5 Testing the D0/D1 Splitted 7-Stage Processor                           | 51 |

|    | 5.2.6 Testing the D0/D1 Splitted 7-Stage Processor with modified Drop Signal | 53 |

|    | 5.2.7 Testing 7-Stage Pipeline Processor With M Stage Branch Resolution      | 53 |

| (  | 5.2.8 Testing 7-Stage Pipeline Processor With JAL at D0                      | 55 |

| 0. | Evaluation                                                                   | 56 |

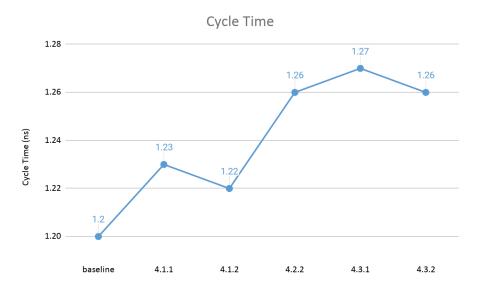

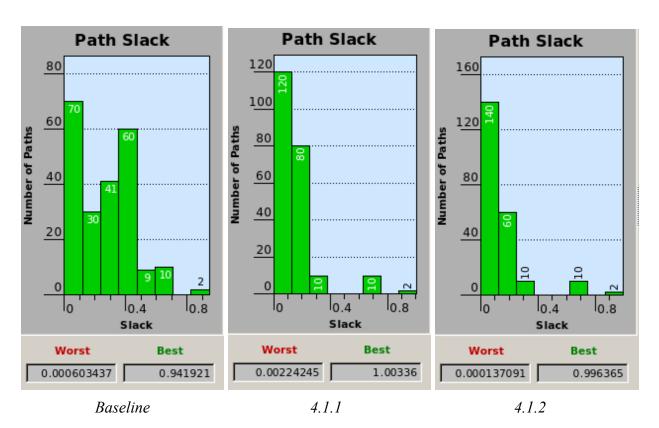

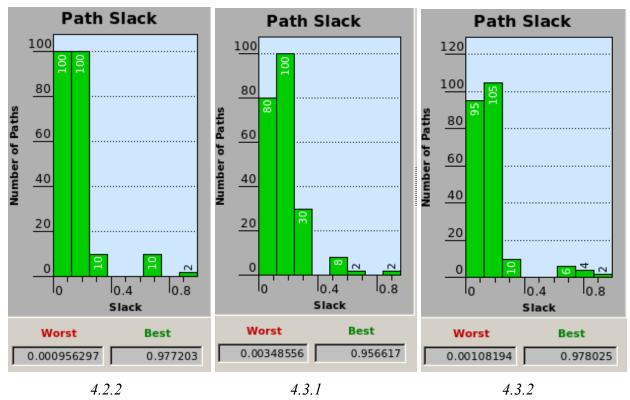

|    | 6.1 Cycle Time                                                               | 56 |

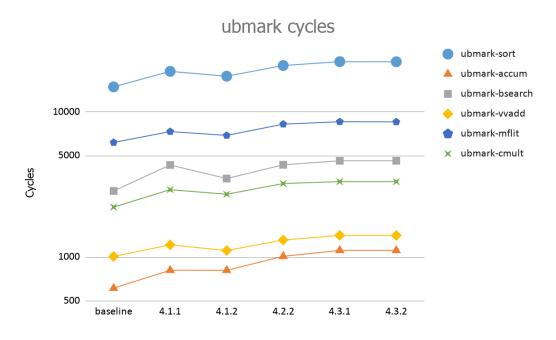

|    | 6.2 CPI                                                                      | 59 |

|    | 6.3 Area                                                                     | 62 |

| _  | 6.4 Power and Energy                                                         | 64 |

|    | Literature Review                                                            | 66 |

| 8. | Appendix                                                                     | 69 |

#### 1. Introduction

One major topic of computer architecture is strategies to improve performance for general-purpose processors. The execution time of a program is determined by the following equation:  $T = i \times cpi \times t$  where i denotes the instructions in total, cpi denotes the cycles per instruction, and t denotes cycle time. Our goal is to improve the performance by reducing t and maintaining a cpi of approximately 1. The cycle time of the processor is determined by the critical path so one effective way to break the critical path into balanced stages is to insert registers in between, also known as pipelining. We intend to divide the well-known 5-stage processor further based on datapath characteristics and therefore achieve superpipelining. One rudimentary example discussed was splitting the M/memory stage into 2 stages, M0 and M1. Since memory operations take a long time due to the cache/memory delay, the critical path can be shortened and clock frequency can be raised, and throughput can be greatly improved as a result.

On the other hand, superscalar and VLIW processors exploit instruction-level parallelism and decrease *cpi* by running multiple instructions in parallel. In theory, a superpipelined design that doubles its pipeline stages and a superscalar design that issues two commands can both achieve a throughput two times higher than a normal pipelined processor under ideal conditions (no hazards/dependencies). However, superscalar and VLIW have their disadvantages. Superscalar processors need to either replicate their hardware units or limit how instructions can be combined to be processed in parallel. VLIW processors have multiple instructions in one word for different functional units but compilers have to decide that at compile time. If the program cannot be broken into parallel instructions that operate on different function units, the parallelism is rendered useless and much of the code size is wasted. Also, both suffer from dependencies between instructions as well as extra logic required for those dependencies and require extra help from smart compilers. They also lack extensibility and compatibility as increasing the level of parallelism means having to alter the machine code for the same program. Therefore, we believe that superpipelining is our best approach to improve performance.

After deciding on superpipelining, we start measuring how throughput is affected by the number of stages. Compared to the simple single-cycle processor, our baseline, a bypassing 5-stage pipelined processor, divides the main datapath into five stages: fetch, decode, execute, memory, and writeback, and thus reduce the critical path. However, as we increase the number of stages, we need to take care of more hazards caused by the dependencies among stages as they cause stalling or squashing, increasing the *cpi* and decreasing the processor performance. In response, we developed direct, unit and random tests to make sure each instruction works and then a sequence of mixed instructions to examine our processor under a variety of hazards.

Now we see the increase in the number of stages helps us reduce the cycle time by reducing the critical path and eventually improve program execution time, a question arises: what is the optimal number of stages for a pipelined processor? This question involves the exploration of the relationship between the number of stages and the number of hazards that

cannot be solved by bypassing. Under such motivation, our team decides to explore the super-pipelined processor capable of running the tinyRV2 instruction set as our alternative design. We apply the same tests from baseline design and develop specific tests to examine the newly emerged hazards.

As discussed in section II, we will use Fan-out of 4 (FO4) delay as a standard time unit to measure the propagation delay of our critical path so we can study our processors regardless of technology constraints. We will calculate FO4 delay for both of our designs and examine the difference. FO4 delay is also used to measure the processor cycle time trend across history so we can compare our designs with others by adopting this standardized unit.

1.

## 2. FO4 Spice Simulation

To measure the propagation delay of a path, we use the propagation delay of a minimum size inverter (3RC) as a relative delay unit. Similarly, to reduce the critical path length and build a high-frequency superpipelined processor, we need a unit that makes our processor cycle time comparable to processors built with different technologies. In this section, we introduce a technology-agnostic metric: Fan-out of 4 (FO4) delay.

For most technologies, the optimal fanout of buffers driving large loads is generally between 2.7 to 5.3, which makes FO4 a good delay measurement unit as tools try to select gates that fit into the fanout range. As a delay metric, one FO4 is the delay of an inverter, driven by an inverter four times smaller, and driving an inverter four times larger. Both conditions are necessary since the rise and fall time of the input signal affect the delay as well as the output load. The FO4 delays of various technologies are shown in *figure 1*.

| the control of the co |       |       |       |       |       |       |       |      |      |      |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|------|------|------|------|

| Vendor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | Orbit | HP    | AMI   | AMI   | TSMC  | TSMC  | TSMC | IBM  | IBM  | IBM  |

| Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | MOSIS | MOSIS | MOSIS | MOSIS | MOSIS | MOSIS | TSMC | IBM  | IBM  | IBM  |

| Feature Size f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | nm    | 2000  | 800   | 600   | 600   | 350   | 250   | 180  | 130  | 90   | 65   |

| $V_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V     | 5     | 5     | 5     | 3.3   | 3.3   | 2.5   | 1.8  | 1.2  | 1.0  | 1.0  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |       |       | (     | ates  |       |       |      |      |      |      |

| $C_g$ (delay)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | fF/μm | 1.77  | 1.67  | 1.55  | 1.48  | 1.90  | 2.30  | 1.67 | 1.04 | 0.97 | 0.80 |

| $C_g$ (power)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | fF/μm | 2.24  | 1.70  | 1.83  | 1.76  | 2.20  | 2.92  | 2.06 | 1.34 | 1.23 | 1.07 |

| FO4 Inv. Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ps    | 856   | 297   | 230   | 312   | 210   | 153   | 75.6 | 45.9 | 37.2 | 17.2 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |       |       |       |       |       |       |      |      |      |      |

Figure 1: FO4 Delay Characteristics for a Variety of Processes (Weste and Harris p.312 Table 8.5)

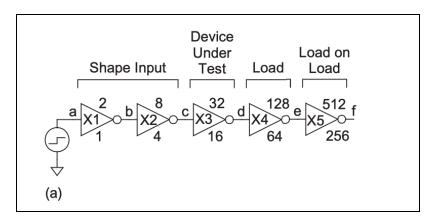

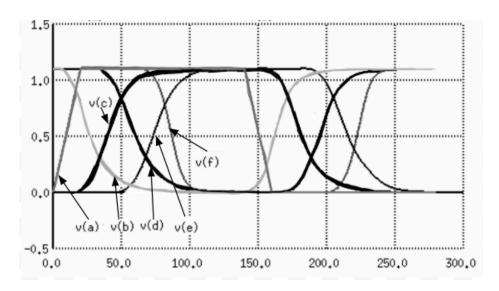

To estimate the FO4 delay of the NanGate 45nm standard-cell library we are using, we used ngspice to simulate the inverter circuit. To gain more understanding of the characteristics of nMOS and pMOS, we first built our own inverters with nMOS and pMOS in the first spice deck. We created a scaling factor so transistor sizes can be expressed as multiples of the minimum width of an NMOS transistor. Since the nMOS of INV\_X1 in the standard cell library has a width of 415nm and a length of 50nm, we used a scale factor such that a width of 1 is equal to 450nm and the length is approximately 0.1 unit. To get a fanout of 4, we used a parameter H=4 to increase the width of the inverter. In this model, we used 5 inverters, each 4 times larger than the inverter before it in the path. As seen in *figure 2*, the first two inverters shape the input waveform, the third one is used for the FO4 delay measurement, and the last two are loads of the path. Using transient analysis, we measured the rising and falling edge propagation delay and average these two to get an inverter FO4 delay of 16.74ps.

Figure 2: FO4 Simulation Model (Inverter built with nMOS and pMOS, Weste and Harris p.295 Fig. 8.9)

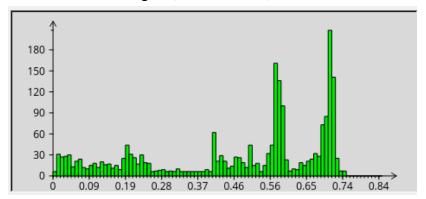

Figure 3: ngspice Waveform (Inverters built with nMOS and pMOS)

Figure 4: ngspice Transient Analysis (Inverters built with nMOS and pMOS)

As we use cells from the NanGate 45nm library when pushing our designs through the ASIC flow, we also built another spice stack using standard inverter cells. Since there are only inverters of size X1, X2, X4, X8, X16, and X32, we used INV\_X1, INV\_X4, and INV\_X16 to build a three-stage path with the first inverter shaping the input, the second as the device under test, and the third as the load. By inspecting the library we find both standard cells and standard cells with parasitic delays. Comparing results in *figure 4*, *figure 5*, and *figure 6*, we conclude that the standard cell library includes optimizations on the layout as well as the relative sizes of

nMOS and pMOS transistors so it has a smaller FO4 delay. By adding parasitic delay to the standard cell, the model more accurately reflected the delay which is longer than the ideal model. Our estimated FO4 is slightly below the FO4 delay of the IBM 65nm process, which is very reasonable.

Figure 5: ngspice Transient Analysis (Inverters from stdcells.spi)

```

Measurements for Transient Analysis

tpdr = 1.524427e-11 targ= 3.692069e-11 trig= 2.167642e-11 tpdf = 1.397153e-11 targ= 1.768417e-10 trig= 1.628701e-10 tpd = 1.46079e-11

```

Figure 6: ngspice Transient Analysis (Inverters from stdcells-lpe.spi)

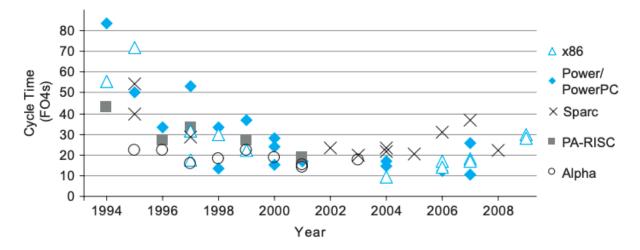

The FO4 delay gives us a relatively accurate metric to assess how well our superpipelined processor divides the stages. According to Hrishikesh *et al.* [4], the optimal depth for each pipeline is 6-8 FO4 delays. Our baseline 5-stage bypassing processor has a cycle time of 1.2ns, which is around 82 FO4 delays. By comparing with other processors of different technologies and eras in *figure 7*, we find our baseline processor at a similar position as the Power/PowerPC processor in 1994, which also had about five stages. The FO4 delay provides a metric for processor cycle time and helps us set goals and evaluate performance of our superpipelined processor optimization.

Figure 7: Microprocessor Cycle Time Trends (Weste and Harris p.175 Fig 4.38)

## 3. Baseline Design

The baseline design focuses on implementing a five-stage pipelined processor with hardware stall and bypass to handle data hazards. One of the most important features of the processor design is the separation of the datapath and control unit: such implementation corresponds to the actual separation between microarchitecture and ISA. Control unit translates the program into hardware language - signals and datapath understands the instruction semantics and performs the executions. We can easily change the instructions and control tables without changing the datapath design - a strategy creating an interface between software and hardware and ensures the safety of the design. This baseline design is a good start for alternative design since this five-stage pipelined processor divides the stages in a somewhat balanced manner, based on datapath characteristics and state functionality.

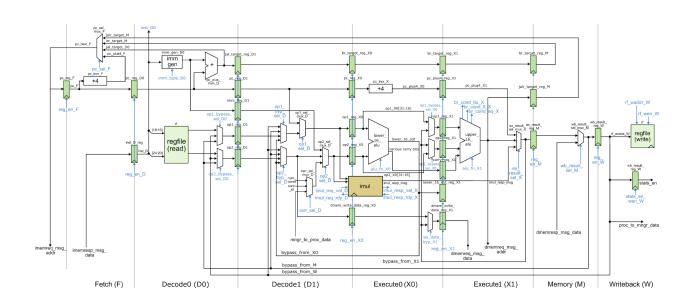

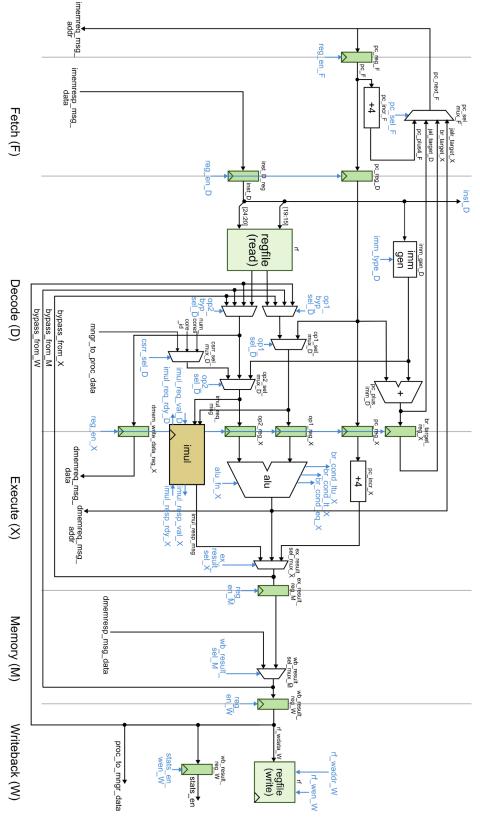

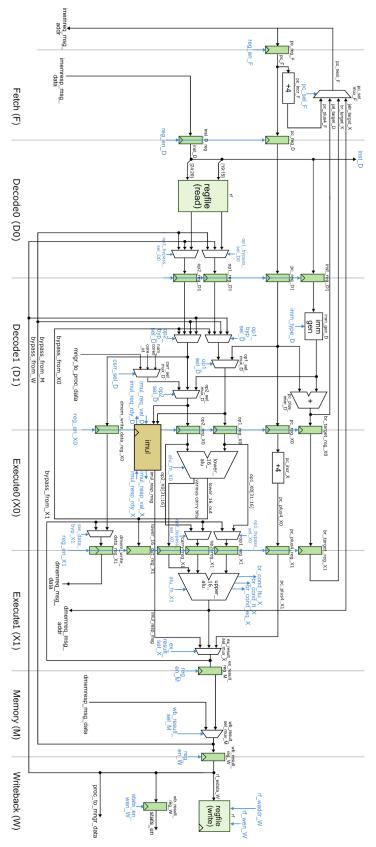

#### 3.1 Datapath

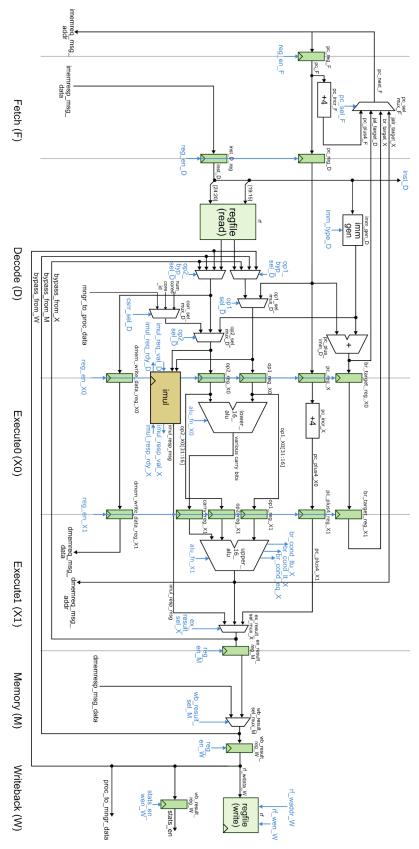

As shown in *Figure 8*, the datapath is split into five stages: fetch, decode, execution, memory, and writeback. Right before the fetch stage, the program counter (PC) is sent to instruction memory. There is an imem drop unit if the requested instruction is not used, which happens due to a squash. Fetch stage increases the PC and reads the instruction pointed by the PC in the memory. A PC mux is used to select multiple PC targets, which can be generated from a branch or a jump. In the decode stage, instruction fetched in the previous cycle is sent to the control unit, which will interpret the 32-bit instruction into different control signals and send them back to the datapath; besides, the decode stage is also responsible for sending input data into the arithmetic logic unit (ALU) and the multiplier. The execution stage takes input from the decode stage, executes the instruction with ALU or multiplier, and outputs the data to the next stage; memory request is also sent if needed by the instruction. In the memory stage, memory response data is sent from the memory and the control unit sends the signal to decide whether to use memory data or use ALU data. The last stage, write back stage writes data into the register file, and whether the stage is useful depends on the instruction type.

Between pipeline stages there exist registers. They store the results of each stage and pass it onto the next stage if there are no stall signals. If there are they will hold the values until the stall is finished. These registers are critical as they are how we make a single-cycle processor into a pipelined processor.

#### 3.2 Control Unit

As illustrated in the previous paragraph, the control unit determines all the signals that select mux inputs and controls pipeline register timing. The most important part, the decode stage, defines a control table that interprets instructions into signals and outputs them to the datapath. These signals include mux control signals, register enable signals, and data type signals. These different signals are passed to different stages accordingly, which maximizes the processor's performance. Another important function of the control unit is to issue stall and

Figure 8: Baseline Processor Datapath

(https://www.csl.cornell.edu/courses/ece5745/handouts/ece5745-lab2-xcel.pdf)

squash signals to avoid data hazards. With all the signals interpreted by the control unit, it is easy to know what instructions are being executed in different stages so that we can implement stall and squash signals to prevent the pipeline from proceeding until data hazards are resolved.

#### 3.3 Implementation Details

As we are following the Tiny RISC-V 2 processor ISA, we implemented 34 instructions that the processor supports by taking an incremental approach. The first set of instructions that we implemented is the register-register type instructions: add, mul, and, or, xor, slt, sltu, sra, srl, sll. For those instructions, we declared new ALU function types in the D stage and added them to the control table. The difference between those instructions is their ALU function type. However mul is very different. We had to add an execute result mux in the X stage. This mux can select from PC increment output, ALU output, or the single stage multiplier output. We also had to set the multiplier request and response in the control table for stall and squash signals. The second set of instructions we implemented is the register-immediate type instructions: addi, andi, ori, xori, slti, sltiu, srai, srli, slli, auipc. Those instructions are very similar to their corresponding register-register instructions except that they use immediate for operand 2 mux selection and have an immediate type select.

The third set of instructions we implemented is the memory instructions 1w and sw. Load and store involves sending memory request messages and waiting for memory responses in the M stage. Memory access address is calculated in the X stage. If it is a sw instruction, data is read from the register and passed into the memory request message; otherwise if it is a 1w instruction, we send a read type memory request and wait for the data from the memory response. The fourth set of instructions we implemented is the jump instructions jal and jalr. In the F stage, the PC selection logic is designed such that if a jump instruction is interpreted in D stage, we would use the PC from D stage. In the D stage, we first declare the new jump types, and then we check if the instruction is jal to redirect the PC if necessary. For jalr instructions, we calculate the target branch in the X stage with a new ALU function. If instruction is jalr, we need to use the jalr target as the next PC. The fifth and final set of instructions we implemented is the branch instructions: bne, beq, blt, bltu, bge, and bgeu. We first declare those branch types in D stage and fill the control table accordingly. Then we check if the branch is taken in the X stage and redirect the PC if it is taken.

Some efforts are put into creating correct stall, squash, and bypass logics to handle hazards that appear in a pipelined processor, including read-after-write data hazard and control hazard brought by branch and jump instructions. Bypassing allows us to avoid hazards without having to stall for every single instruction; as a result, the overhead for load-use data hazard becomes only one cycle. We only have to stall for load word instruction since the data needed to be bypassed is ready at M stage instead of D stage, so the load-use latency is two cycles.

As bypassing data is used to replace the original data output of the register file and we still want the immediate and the PC signals to be potential operands for the ALU unit, we choose to place the bypassing muxes between the register file and the select mux for its corresponding operand. Each bypass mux has four inputs, outputs from the bypassing paths of X, M and W stage and the output of the register file. The output of each bypass mux is connected to an input of its corresponding operand select mux in stage D. If bypassing is needed for resolving the hazard, the bypassing mux select signal will choose the bypassed data and the operand select mux will use the output from the bypassing mux.

As for the control units, we have six bypassing signals and two ostall signals for load use dependency. The bypassing signals indicate if a bypass is needed and, if needed, from which stage among X, M or W does the bypass path come from, and which operand, op1 or op2, will use the data. The load-use dependency is an exception because loaded data is available at the end of the M stage and we have to bypass data back to the D stage to resolve this hazard. To correctly handle stalls and squashes for branches and jump, we have additional status and control signals. jal needs to be resolved in the D stage and branches and jalr in the X stage. We change the PC target mux selection signal based on the instruction type and originate squashes from the stage if the PC is redirected.

The separation of the datapath and control unit is a clear example of modularity and encapsulation. It prevents other modules from being modified while changes are made. Modularity is also shown in the datapath design. As we instantiate registers, muxes, ALU, and the multiplier from existing modules, we create a hierarchy of modules with the processor design at the top, datapath, and control unit in the middle, and other basic components at the bottom. This adds simplicity to the design, makes it more extensible, and decreases the chance of corrupting other functionalities during implementation. As the stall strategy is purely hardware, bringing convenience to the programmers who don't need to worry about adding extra operations to avoid data hazards.

## 4. Alternative Design

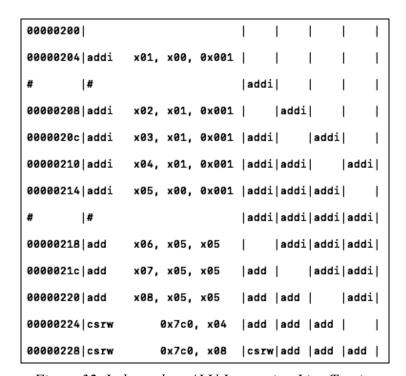

To implement a superpipelined processor based on the original baseline design, we decided to take an incremental approach, splitting the critical path of the previous design and then push the asic flow again to decide the constrainting path of the new design. The best timing we can achieve for the 5-stage bypassing processor is 1.2 ns, which is approximately 82 FO4 delays. The critical path starts from the register for operand 2 in the X stage, goes into the ALU, enters the control logic from ALU's branch prediction signal, and ends at the instruction memory request register. The gate level list for the critical path is shown in *figure 9* and *figure 10*. So the first step we take is to split the X stage.

| Instance                                           | Arc             | Cell                   | Slew<br> | Delay<br>        | Arrival<br>  Time | Required<br>  Time |

|----------------------------------------------------|-----------------|------------------------|----------|------------------|-------------------|--------------------|

|                                                    | clk[0] ^        | +<br>                  | 0.025    | <br>             | -0.134            | -0.134             |

| CTS_ccl_a_BUF_ideal_clock_G0_L1_1                  | i               | CLKBUF_X2              | i 0.025  | 0.001            | i -0.133          | -0.133             |

| CTS_ccl_a_BUF_ideal_clock_G0_L1_1                  | i A ^ -> Z ^    | CLKBUF_X2              | 0.036    | 0.064            | -0.069            | -0.069             |

| proc/v/dpath/CTS_ccl_a_BUF_ideal_clock_G0_L2_3     | i               | CLKBUF_X2              | 0.036    | 0.002            | -0.067            | -0.067             |

| proc/v/dpath/CTS ccl a BUF ideal clock G0 L2 3     | A ^ -> Z ^      | CLKBUF X2              | 0.027    | 0.059            | -0.009            | -0.008             |

| proc/v/dpath/op2_reg_X/clk_gate_q_reg/latch        |                 | CLKGATETST_X4          | 0.027    | 0.001            | -0.008            | -0.008             |

| proc/v/dpath/op2_reg_X/clk_gate_q_reg/latch        | i CK ^ -> GCK ^ | CLKGATETST_X4          | 0.027    | 0.054            | 0.046             | 0.046              |

| proc/v/dpath/op2_reg_X/q_reg_11_                   |                 | DFF_X1                 | 0.027    | 0.002            | 0.048             | 0.048              |

| proc/v/dpath/op2_reg_X/q_reg_11_                   | CK ^ -> 0 ^     | DFF_X1                 | 0.078    | 0.174            | 0.221             | 0.222              |

| proc/v/dpath/alu/lt_x_7/U689                       | 5.1.            | NORZ_X2                | 0.078    | 0.002            | 0.223             | 0.224              |

| proc/v/dpath/alu/lt_x_7/U689                       | A1 ^ -> ZN v    | NOR2_X2                | 0.017    | 0.009            | 0.233             | 0.233              |

| proc/v/dpath/alu/lt_x_7/U706                       | ~ 2, ,          | NOR2_X1                | 0.017    | 0.000            | 0.233             | 0.233              |

| proc/v/dpath/alu/lt_x_7/U706                       | A1 v -> ZN ^    | NOR2_X1                | 0.018    | 0.028            | 0.261             | 0.261              |

| proc/v/dpath/atd/tt_x_7/U707                       | AI V -> ZI      | A0I22 X1               | 0.018    | 0.000            | 0.261             | 0.261              |

| proc/v/dpath/atu/tt_x_//0/0/                       | B2 ^ -> ZN v    | A0122_X1<br>A0122_X1   |          | 0.026            | 0.287             | 0.287              |

| proc/v/dpath/alu/lt_x_7/U707                       | D2 -> ZN V      |                        | 0.027    |                  | 0.287             | 0.287              |

| proc/v/dpath/alu/lt_x_7/U710                       | B2 v -> ZN ^    | A0I221_X1              | 0.027    | 0.000            |                   |                    |

| proc/v/dpath/alu/lt_x_7/U710                       | P5 A -> TM      | A0I221_X1              | 0.043    | 0.087            | 0.373             | 0.374              |

| proc/v/dpath/alu/lt_x_7/U714                       |                 | A0I211_X1              | 0.043    | 0.000            | 0.374             | 0.374              |

| proc/v/dpath/alu/lt_x_7/U714                       | A ^ -> ZN v     | A0I211_X1              | 0.018    | 0.025            | 0.399             | 0.399              |

| proc/v/dpath/alu/lt_x_7/FE_RC_840_0                | !               | 0AI21_X2               | 0.018    | 0.000            | 0.399             | 0.400              |

| proc/v/dpath/alu/lt_x_7/FE_RC_840_0                | A v -> ZN ^     | 0AI21_X2               | 0.019    | 0.025            | 0.424             | 0.424              |

| proc/v/dpath/alu/lt_x_7/U748                       | !               | A0I21_X1               | 0.019    | 0.000            | 0.424             | 0.425              |

| proc/v/dpath/alu/lt_x_7/U748                       | B1 ^ -> ZN v    | A0I21_X1               | 0.011    | 0.020            | 0.444             | 0.444              |

| proc/v/dpath/alu/lt_x_7/U781                       | 1               | OAI21_X2               | 0.011    | 0.000            | 0.444             | 0.444              |

| proc/v/dpath/alu/lt_x_7/U781                       | B1 v -> ZN ^    | OAI21_X2               | 0.041    | 0.057            | 0.501             | 0.501              |

| proc/v/ctrl/FE_0FC368_br_cond_lt_X                 | 1               | INV_X1                 | 0.041    | 0.001            | 0.502             | 0.502              |

| proc/v/ctrl/FE_0FC368_br_cond_lt_X                 | A ^ -> ZN v     | INV_X1                 | 0.010    | 0.010            | 0.511             | 0.512              |

| proc/v/ctrl/FE_RC_594_0                            | i               | 0AI33_X1               | 0.010    | 0.000            | 0.511             | 0.512              |

| proc/v/ctrl/FE_RC_594_0                            | A1 v -> ZN ^    | 0AI33_X1               | 0.058    | 0.042            | 0.553             | 0.554              |

| proc/v/ctrl/U148                                   | i               | NAND2_X1               | 0.058    | 0.000            | 0.553             | 0.554              |

| proc/v/ctrl/U148                                   | A1 ^ -> ZN v    | NAND2_X1               | 0.020    | 0.026            | 0.579             | 0.580              |

| proc/v/ctrl/U153                                   | i               | 0AI211 X2              | 0.020    | 0.000            | 0.579             | 0.580              |

| proc/v/ctrl/U153                                   | İAV -> ZN ^     | 0AI211 X2              | i 0.025  | 0.029            | 0.608             | 0.609              |

| proc/v/ctrl/U156                                   | i               | NAND2_X2               | 0.025    | 0.000            | 0.609             | 0.609              |

| proc/v/ctrl/U156                                   | A1 ^ -> ZN v    | NAND2 X2               | 0.014    | 0.024            | 0.633             | 0.633              |

| proc/v/ctrl/U158                                   |                 | A0I21 X2               | 0.014    | 0.000            | 0.633             | 0.634              |

| proc/v/ctrl/U158                                   | i B2 v -> ZN ^  | A0I21_X2               | 0.025    | 0.037            | 0.670             | 0.671              |

| proc/v/imem_drop_unit/FE_RC_831_0                  |                 | NOR3_X1                | 0.025    | 0.000            | 0.670             | 0.671              |

| proc/v/imem_drop_unit/FE_RC_831_0                  | A1 ^ -> ZN v    | NOR3 X1                | 0.009    | 0.015            | 0.686             | 0.686              |

| proc/v/imemresp_q/genblk1_ctrl/U6                  | ~               | INV_X2                 | 0.009    | 0.000            | 0.686             | 0.686              |

| proc/v/imemresp_q/genblk1_ctrl/U6                  | A v -> ZN ^     | INV_X2                 | 0.007    | 0.012            | 0.698             | 0.699              |

| proc/v/imemresp_q/genblk1_ctrl/U7                  | 1 ~ ~ 21        | NAND2_X1               | 0.007    | 0.000            | 0.698             | 0.699              |

| proc/v/imemresp_q/genblk1_ctrl/U7                  | A1 ^ -> ZN v    | NAND2_X1               | 0.020    | 0.015            | 0.713             | 0.713              |

| proc/v/ctrl/U160                                   | A1 -> 2N V      | NAND2_XI<br>  NAND2_X2 | 0.020    | 0.000            | 0.713             | 0.713              |

|                                                    | A1 v -> ZN ^    | NAND2_X2               | 0.011    |                  | 0.733             | 0.734              |

| proc/v/ctrl/U160<br>proc/v/ctrl/U162               | VT A -> 74      | NAND2_X2<br>  NAND2_X1 | 0.011    | 0.020<br>  0.000 | 0.733<br>  0.733  | 0.734              |

|                                                    | A1 A > 7N ··    |                        |          |                  |                   |                    |

| proc/v/ctrl/U162                                   | A1 ^ -> ZN v    | NAND2_X1               | 0.010    | 0.016            | 0.750             | 0.750              |

| proc/v/ctrl/FE_OFC485_imemresp_deq_en              |                 | INV_X2                 | 0.010    | 0.000            | 0.750             | 0.750              |

| proc/v/ctrl/FE_OFC485_imemresp_deq_en              | A v -> ZN ^     | INV_X2                 | 0.011    | 0.019            | 0.768             | 0.769              |

| proc/v/ctrl/U166                                   | l               | NOR2_X2                | 0.011    | 0.000            | 0.768             | 0.769              |

| proc/v/ctrl/U166                                   | A1 ^ -> ZN v    | N0R2_X2                | 0.008    | 0.010            | 0.779             | 0.779              |

| proc/v/imemreq_q/genblk1_ctrl/U5                   | !               | INV_X2                 | 0.008    | 0.000            | 0.779             | 0.779              |

| proc/v/imemreq_q/genblk1_ctrl/U5                   | A v -> ZN ^     | INV_X2                 | 0.009    | 0.015            | 0.794             | 0.795              |

| proc/v/imemreq_q/genblk1_ctrl/U9                   | I               | NAND2_X1               | 0.009    | 0.000            | 0.794             | 0.795              |

| proc/v/imemreq_q/genblk1_ctrl/U9                   | A2 ^ -> ZN v    | NAND2_X1               | 0.024    | 0.014            | 0.809             | 0.809              |

| proc/v/U4                                          | 1               | AND2_X2                | 0.024    | 0.000            | 0.809             | 0.809              |

| proc/v/U4                                          | A2 v -> ZN v    | AND2_X2                | 0.008    | 0.040            | 0.849             | 0.849              |

| proc/v/imemreq_q/genblk1_ctrl/U6                   | i               | A0I21 X1               | 0.008    | 0.000            | 0.849             | 0.850              |

| proc/v/imemreq_q/genblk1_ctrl/U6                   | B1 v -> ZN ^    | A0I21_X1               | 0.041    | 0.035            | 0.884             | 0.884              |

| proc/v/imemreq_q/genblk1_dpath/qstore/FE_RC_850_0  | i               | AND2 X1                | 0.041    | 0.000            | 0.884             | 0.884              |

| proc/v/imemreq_q/genblk1_dpath/qstore/FE_RC_850_0  | A2 ^ -> ZN ^    | AND2_X1                | 0.009    | 0.040            | 0.924             | 0.924              |

| proc/v/imemreq_q/genblk1_dpath/qstore/clk_gate_rfi |                 | CLKGATETST_X4          | 0.009    | 0.000            | 0.924             | 0.924              |

| le_reg_0_/latch                                    | !               | ,                      | , 5.505  |                  | , 5.527           | . 5.524            |

Figure 9. Gate Level Critical Path for 5-stage processor

Figure 10. Critical Path for 5-stage Processor (Based on <a href="https://www.csl.cornell.edu/courses/ece5745/handouts/ece5745-lab2-xcel.pdf">https://www.csl.cornell.edu/courses/ece5745/handouts/ece5745-lab2-xcel.pdf</a>)

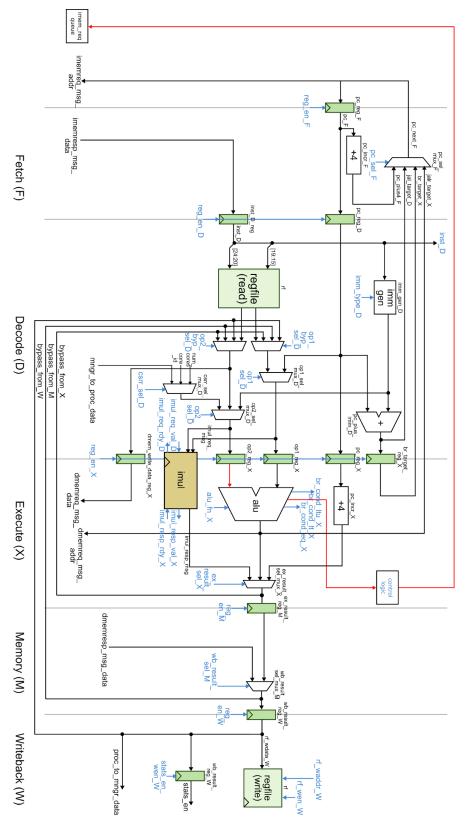

## 4.1 Splitting X Stage into X0/X1

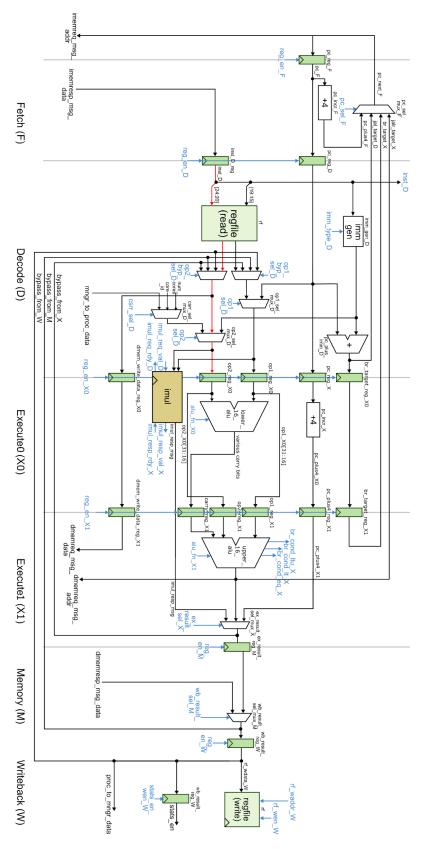

As the Arithmetic Logic Unit (ALU) is the main component of the X stage, we decide to split the ALU into two different parts: the operation of the lower 16 bits of the operands are finished in X0 stage and the remaining necessary data are passed into X1 to finish the higher 16 bits computation. With additional logic described in 4.1.2, this design is possible to avoid stalling due to read-after-write dependencies between X0 and X1 by bypassing data from X0 back to D and from X1 back to X0. Instructions do not need to wait until the instructions they depend on to finish computing at X1 stage.

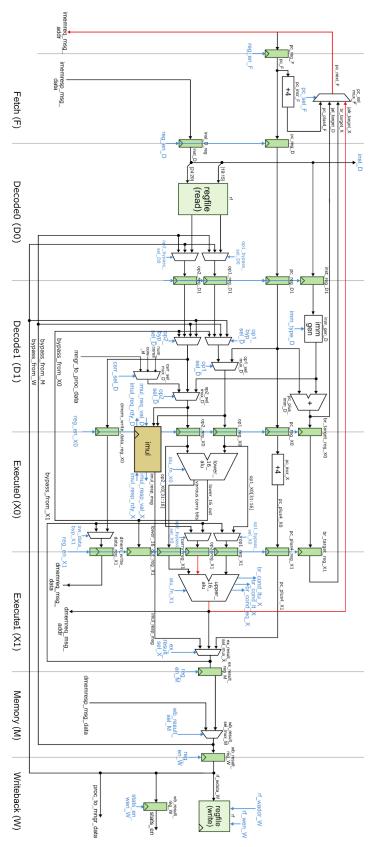

#### 4.1.1 Stalling Without Additional Bypassing

#### 4.1.1.a Datapath

There are 14 instructions we need to support: arithmetic operations (add, sub), logical operations (and, or, xor, nor), shift operation (sll, srl, sra), comparisons (lt, ltu), and special operations (cp0, cp1, and adz). To support arithmetic operation, we need to pass a carry\_out bit between the lower-16-bit ALU and the upper-16-bit ALU. Like what we would do in a normal ripple carry adder, the carrry\_out bit indicates whether we need to add/subtract 1 from the upper-16-bit addition/subtraction. The result of the lower-16-bit computation is also passed through a register into the X1 to generate the final result. The logical operation and the two copy instructions are the easiest to implement as they do not have any dependencies between the upper and lower 16 bits so we keep the original implementation and pass the output from X0 to X1 stage.

Even though shift operations take two 32-bit inputs, it only uses the lower 5 bits of operand 2 to indicate the shift amount, which means we need to pass the shift op1 value to the X1 stage so that the upper 16 bits can shift with the right parameters. Instruction sll performs a logical left shift, meaning there are 0 to 16 bits to be shifted into the upper 16 bit position. So we pass the shift out bits into the upper-16-bit ALU together with the lower-16-bit ALU output. In X1 stage we shift the upper 16 bit of the original operand 0 and or the concatenated the results to generate the final output. Operation srl is a logical right shift, meaning the upper 16 bits will be shifted to the lower 16 bit position. So we set shift out to 0, zero-fill the lower 16 bit position of operand 0 of the X1 stage (which is the upper 16 bits of the actual operand 0), shift, and or the result with the output of X0 stage. Operation sra is the arithmetic right shift and thus we use a \$signed operation to decide whether to zero-fill or one-fill the vacant bit-positions based on the sign of the original operand 0. Comparisons are first determined by the comparison in the upper 16 bits. If they are of equal value, then the result of the lower-16-bit ALU is used to decide the output. Operation adz is a special operation for the JALR instruction. It performs an addition but masks the lowest bit to 0. So its implementation is exactly the same as the add operation, but with the lowest bit connected to 0 in the lower-16-ALU. Besides the 14 operations, ALU also calculates flags used for branch redirection.

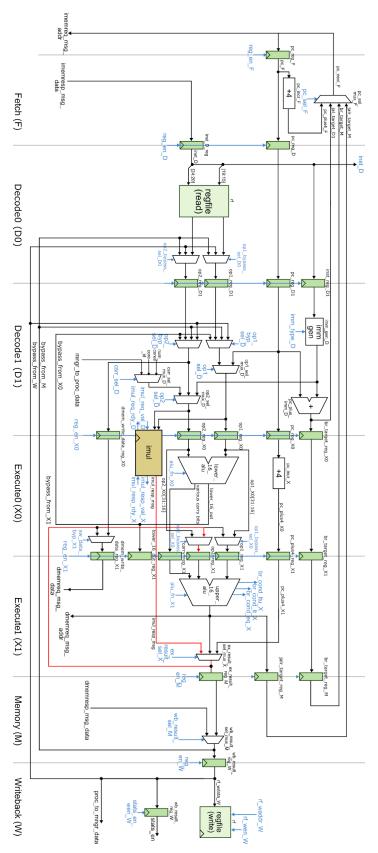

Figure 11. Datapath for X0/X1 Splitted Processor Without Additional Bypassing

Flag ops\_lt and ops\_ltu have exactly the same implementation as the lt and ltu operation, and ops\_eq is implemented by doing comparison in both stages and output 1 if the two operands are the same in both X0 and X1.

After fully testing the two components, we started the integration of ALU and the processor. X0 stage is also responsible for sending the accelerator request message as they are ready at the beginning of X0 stage. In the X1 stage, after the upper-16-bit ALU finishes computation, its output is connected to the jump-and-link-register target and the data memory request message address port. There is a mux after the ALU which is used to select the actual output of the X1 stage among ALU results, multiplier response message, and PC+4 result for jump-and-link based on the instruction type.

#### 4.1.1.b Control Logic

As we add one more stage to the processor, we need to carefully consider the stall, bypass, and squash logic for the processor. As we are implementing a basic 6-stage processor that supports all of the functionality the baseline processor has, we did not have to include the bypassing logic from X0 to D and from X1 to X0. Instead, in the Decode stage, when the processor realizes that the destination register of stage X0 matches with the operand registers in stage D, we stall for one cycle to avoid hazard caused by read-after-write dependency; if the instruction in X1 stage is a lw, and its destination register matches with the operand register in the D stage, we stall until we get the data back from the memory. Besides, as we implement the processor to support the accelerator, we also need to stall at D stage if there is a csrx instruction in-flight at X0/X1 stage since its value will not be returned from the accelerator until M stage. X0 stage only originates stall when the accelerator request is not ready; X1 stage originates stalls if its instruction is multiplication and the multiplier is not ready to respond yet; it also stalls if its instruction needs to send a data memory request but the memory is not ready to take requests. X1 also originates a squash if it needs to handle a PC redirect for branch or jump instruction. Same to our design in the baseline, one stage will be stalled if itself or any state after it originates a stall, and will be squashed only when a stage after it originates a squash.

#### 4.1.1.c Critical Path

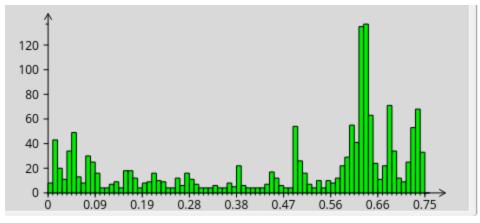

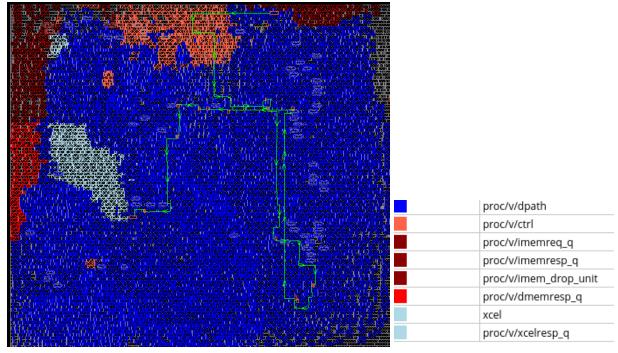

By pushing the design through the ASIC flow, we get a minimum cycle time of 1.3 ns and the critical path is at the D stage (illustrated in *figure 12* and *figure 13*): it starts from the pipeline register for instruction, goes through the register file and the bypassing muxes, and ends at the operand register between D stage and X0 stage. This critical path shows that it might be necessary for us to insert pipeline registers in the D stage after the register file to reduce the cycle time.

| Instance                                     | Arc            | Cell       |        | Slew  | Delay | Arrival | Required      |

|----------------------------------------------|----------------|------------|--------|-------|-------|---------|---------------|

|                                              | l I            |            | ı      |       |       | Time    | Time          |

| <br>                                         | <br>  clk[0] ^ |            | +<br>I | 0.023 | ·     | -0.134  | +<br>  -0.132 |

| proc/v/CTS_ccl_a_BUF_ideal_clock_G0_L1_2     |                | CLKBUF_X3  | ľ      | 0.023 | 0.001 | -0.133  |               |

| proc/v/CTS_ccl_a_BUF_ideal_clock_G0_L1_2     | A ^ -> Z ^     | CLKBUF X3  | i      | 0.032 |       | -0.071  |               |

| proc/v/CTS_ccl_a_BUF_ideal_clock_G0_L2_13    |                | CLKBUF X2  | i      | 0.032 |       | -0.067  |               |

|                                              | A ^ -> Z ^     | CLKBUF X2  | i      | 0.026 |       | -0.010  |               |

| proc/v/dpath/inst D reg/clk gate q reg/latch |                | CLKGATETST | X4     | 0.026 | 0.001 | -0.009  |               |

| proc/v/dpath/inst_D_reg/clk_gate_q_reg/latch | CK ^ -> GCK ^  | CLKGATETST |        |       | 0.053 | 0.044   |               |

| proc/v/dpath/inst D_reg/q_reg_15_            | i              | DFF_X1     | i      | 0.026 | 0.001 | 0.045   | 0.047         |

| proc/v/dpath/inst_D_reg/q_reg_15_            | CK ^ -> Q ^    | DFF_X1     | i      | 0.069 | 0.156 | 0.201   | 0.202         |

| proc/v/dpath/rf/rfile/U110                   |                | OR2_X1     | i      | 0.069 | 0.003 | 0.204   | 0.205         |

| proc/v/dpath/rf/rfile/U110                   | A2 ^ -> ZN ^   | OR2_X1     | i      | 0.083 | 0.116 | 0.320   | 0.321         |

| proc/v/dpath/rf/rfile/U195                   |                | NOR2_X1    | i      | 0.083 | 0.004 | 0.324   | 0.326         |

| proc/v/dpath/rf/rfile/U195                   | A1 ^ -> ZN v   | NOR2_X1    | ĺ      | 0.016 | 0.005 | 0.329   | 0.331         |

| proc/v/dpath/rf/rfile/FE_OFC210_n645         |                | CLKBUF_X1  | ĺ      | 0.016 | 0.000 | 0.329   | 0.331         |

| proc/v/dpath/rf/rfile/FE_OFC210_n645         | A v -> Z v     | CLKBUF_X1  |        | 0.102 | 0.138 | 0.468   | 0.469         |

| proc/v/dpath/rf/rfile/FE_OFC211_n645         |                | CLKBUF_X1  | ĺ      | 0.102 | 0.002 | 0.470   | 0.472         |

| proc/v/dpath/rf/rfile/FE_OFC211_n645         | A v -> Z v     | CLKBUF_X1  | ĺ      | 0.074 | 0.136 | 0.606   | 0.607         |

| proc/v/dpath/rf/rfile/U828                   |                | A0I22_X1   |        | 0.074 | 0.003 | 0.609   | 0.611         |

| proc/v/dpath/rf/rfile/U828                   | B1 v -> ZN ^   | A0I22_X1   |        | 0.031 | 0.065 | 0.674   | 0.676         |

| proc/v/dpath/rf/rfile/U829                   |                | NAND4_X1   |        | 0.031 | 0.000 | 0.674   | 0.676         |

| proc/v/dpath/rf/rfile/U829                   | A4 ^ -> ZN v   | NAND4_X1   |        | 0.045 | 0.083 | 0.757   | 0.759         |

| proc/v/dpath/rf/rfile/U830                   |                | OR4_X1     |        | 0.045 | 0.001 | 0.759   | 0.760         |

| proc/v/dpath/rf/rfile/U830                   | A4 v -> ZN v   | OR4_X1     |        | 0.023 | 0.147 | 0.906   | 0.908         |

| proc/v/dpath/rf/U48                          |                | AND2_X1    |        | 0.023 | 0.000 | 0.906   | 0.908         |

| proc/v/dpath/rf/U48                          | A1 v -> ZN v   | AND2_X1    |        | 0.007 | 0.036 | 0.942   | 0.944         |

| proc/v/dpath/op1_byp_mux_D/U129              |                | A0I22_X1   |        | 0.007 | 0.000 | 0.942   | 0.944         |

| proc/v/dpath/op1_byp_mux_D/U129              | A2 v -> ZN ^   | A0I22_X1   |        | 0.027 | 0.038 | 0.980   | 0.982         |

| proc/v/dpath/op1_byp_mux_D/U131              |                | NAND2_X1   |        | 0.027 | 0.000 | 0.980   | 0.982         |

| proc/v/dpath/op1_byp_mux_D/U131              | A1 ^ -> ZN v   | NAND2_X1   |        | 0.012 | 0.020 | 1.000   | 1.002         |

| proc/v/dpath/op1_sel_mux_D/U54               |                | MUX2_X1    |        | 0.012 | 0.000 | 1.000   | 1.002         |

| proc/v/dpath/op1_sel_mux_D/U54               | A v -> Z v     | MUX2_X1    |        | 0.020 | 0.074 | 1.074   | 1.076         |

| proc/v/dpath/op1_reg_X1/U33                  |                | AND2_X1    |        | 0.020 | 0.001 | 1.075   | 1.077         |

| proc/v/dpath/op1_reg_X1/U33                  | A1 v -> ZN v   | AND2_X1    |        | 0.007 | 0.034 | 1.109   | 1.110         |

| proc/v/dpath/op1_reg_X1/q_reg_4_             |                | DFF_X1     |        | 0.007 | 0.000 | 1.109   | 1.110         |

Figure 12. Gate Level Critical Path for X0/X1 Splitted Processor Without Additional Bypassing (X1 in figure corresponds to X0 in report)

Figure 13. Critical Path for X0/X1 Splitted Processor Without Additional Bypassing

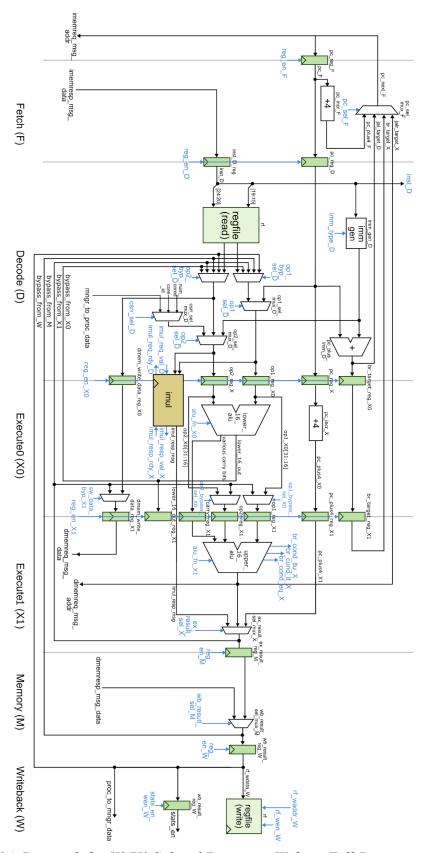

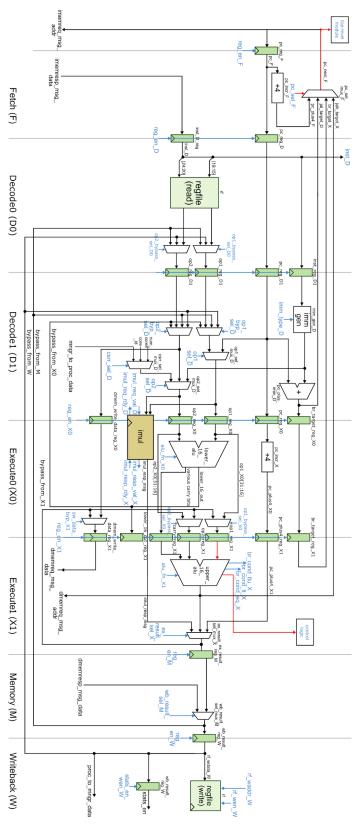

#### 4.1.2 Bypassing in X0/X1 Stage

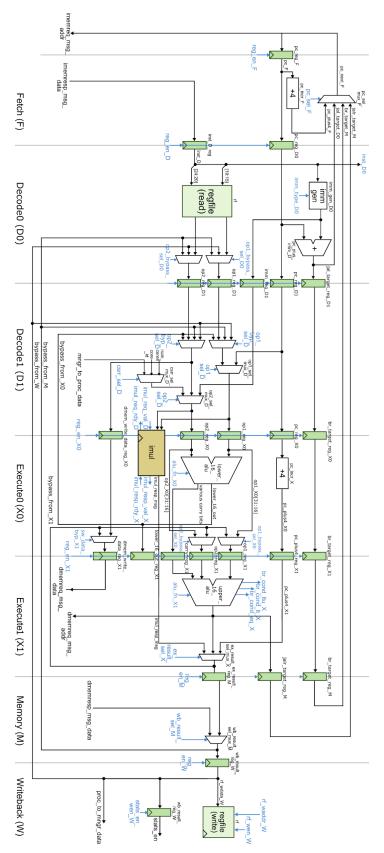

To avoid the extra bubble/stall introduced to the pipeline when executing back to back dependent arithmetic instructions, we plan to add extra bypass logic to our processor, namely from X0 to D and from X1 to X0. In the implementation described in 4.1, the pipeline inserts a bubble whenever the destination register of the instruction in X0 matches one of the two input registers in D as the full 32-bit output will not be ready until the end of X1. To eliminate this bubble, we can forward the lower 16-bit result from the end of X0 to the input muxes at the D stage. We also need to add two additional input muxes at X0 so that the upper-16 bits can be forwarded from the end of X1. This will retrieve some of the CPI as back-to-back dependent instructions are extremely common in assembly. However, the extra delay slot from load-use dependency cannot be resolved as the data from memory does not reach datapath until M.

#### 4.1.2.a Datapath

Based on the above illustration, we add a bypassing path from X0 to the end of the D stage: if the destination register of the instruction in X0 matches with any of the two operands in D stage, the lower 16 bits of the X0 ALU computation result will be bypassed into the D stage; similarly, two additional muxes are added at the end of X0 stage to conditionally bypass data from X1 to X0. To make sure data is correctly stored into memory when there is a dependency between data of the sw instruction and previous instruction destination, X1 result is also bypassed to the memory request data port in X0.

#### 4.1.2.b Control Logic

We still insert a bubble for the load-use dependency scenario as data loaded from memory cannot be returned until the end of the M stage. If there is a match between accelerator request instruction (csrw) operands and previous instruction destination, csrw waits until the computation result is bypassed from X1 back to D stage as the accelerator request is sent in X0 stage. As there are dependencies between X0 and X1 stages, we add additional stall logic for multiplication, comparison, and right shift operation. As the multiplier is given two cycles to do the computation we wait until the end of the X1 stage to collect the result; comparison (lt, ltu) and right shift (srl, sra) result are not ready until X1 stage because the lower 16 bits of comparison operands are only useful when their higher 16 bits are the same and shifting right means higher 16 bits of the operand will be shifted to the lower 16 bit position of the result.

#### 4.1.2.c Critical Path

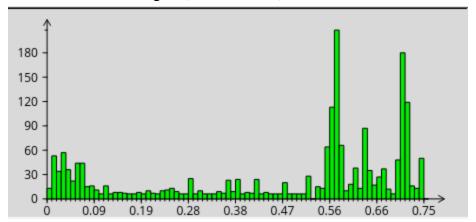

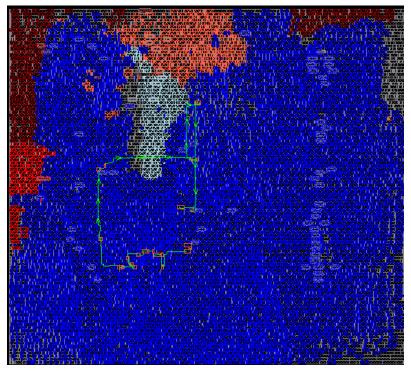

By pushing the design through the ASIC flow, we get a minimum cycle time of 1.25 ns and the critical path is the bypassing path from the X1 stage to the D stage (illustrated in *figure 15* and *figure 16*): it starts from the operand register in X1 stage, goes through the higher-16-bit

Figure 14. Datapath for X0/X1 Splitted Processor Without Full Bypassing

ALU, enters the execution result select mux, follows the bypassing path from X1 to D to the muxes in D stage, and ends at the operand register between D stage and X0 stage. Combining this critical path with the critical path we find for the non-bypassing 6-stage processor, we decide the next step is splitting the D stage into D0/D1.

|                                                         | clk[0] ^      |               | 0.024 |       | -0.138 | -0.145 |

|---------------------------------------------------------|---------------|---------------|-------|-------|--------|--------|

| CTS_ccl_a_BUF_ideal_clock_G0_L1_1                       |               | CLKBUF_X3     | 0.024 | 0.001 | -0.137 | -0.145 |

| CTS_ccl_a_BUF_ideal_clock_G0_L1_1                       | A ^ -> Z ^    | CLKBUF_X3     | 0.030 | 0.061 | -0.077 | -0.084 |

| proc/v/dpath/CTS_ccl_a_BUF_ideal_clock_G0_L2_2          |               | CLKBUF_X1     | 0.030 | 0.003 | -0.073 | -0.081 |

| proc/v/dpath/CTS_ccl_a_BUF_ideal_clock_G0_L2_2          | A ^ -> Z ^    | CLKBUF_X1     | 0.026 | 0.059 | -0.015 | -0.022 |

| proc/v/dpath/op1_reg_X2/clk_gate_q_reg/latch            |               | CLKGATETST_X2 | 0.026 | 0.000 | -0.014 | -0.022 |

| <pre>proc/v/dpath/op1_reg_X2/clk_gate_q_reg/latch</pre> | CK ^ -> GCK ^ | CLKGATETST_X2 | 0.007 | 0.029 | 0.015  | 0.008  |

| proc/v/dpath/op1_reg_X2/clk_gate_q_reg/FE_USKC1279      |               | CLKBUF_X2     | 0.007 | 0.000 | 0.015  | 0.008  |

| _net5499                                                |               | l             |       |       | l I    | 1      |

| proc/v/dpath/op1_reg_X2/clk_gate_q_reg/FE_USKC1279      | A ^ -> Z ^    | CLKBUF_X2     | 0.029 | 0.050 | 0.065  | 0.058  |

| _net5499                                                |               |               |       |       | l l    | 1      |

| proc/v/dpath/op1_reg_X2/q_reg_10_                       |               | DFF_X1        | 0.029 | 0.001 | 0.065  | 0.058  |

| proc/v/dpath/op1_reg_X2/q_reg_10_                       | CK ^ -> Q v   | DFF_X1        | 0.027 | 0.116 | 0.181  | 0.174  |

| proc/v/dpath/alu_higher16/U50                           |               | INV_X1        | 0.027 | 0.004 | 0.185  | 0.178  |

| proc/v/dpath/alu_higher16/U50                           | A v -> ZN ^   | INV_X1        | 0.034 | 0.051 | 0.236  | 0.229  |

| proc/v/dpath/alu_higher16/U136                          |               | A0I22_X1      | 0.034 | 0.001 | 0.237  | 0.230  |

| proc/v/dpath/alu_higher16/U136                          | B1 ^ -> ZN v  | A0I22_X1      | 0.031 | 0.038 | 0.274  | 0.267  |

| proc/v/dpath/alu_higher16/U137                          |               | A0I22_X1      | 0.031 | 0.000 | 0.274  | 0.267  |

| proc/v/dpath/alu_higher16/U137                          | B2 v -> ZN ^  | A0I22_X1      | 0.025 | 0.056 | 0.331  | 0.324  |

| proc/v/dpath/alu_higher16/U138                          |               | OAI21_X1      | 0.025 | 0.000 | 0.331  | 0.324  |

| proc/v/dpath/alu_higher16/U138                          | A ^ -> ZN v   | OAI21_X1      | 0.020 | 0.035 | 0.365  | 0.358  |

| proc/v/dpath/alu_higher16/U300                          |               | AND2_X1       | 0.020 | 0.000 | 0.365  | 0.358  |

| proc/v/dpath/alu_higher16/U300                          | A1 v -> ZN v  | AND2 X1       | 0.008 | 0.038 | 0.403  | 0.396  |

| proc/v/dpath/alu_higher16/U311                          |               | A0I21_X1      | 0.008 | 0.000 | 0.403  | 0.396  |

| proc/v/dpath/alu_higher16/U311                          | A v -> ZN ^   | A0I21_X1      | 0.064 | 0.093 | 0.496  | 0.489  |

| proc/v/dpath/alu_higher16/U312                          |               | A0I21_X1      | 0.064 | 0.000 | 0.497  | 0.489  |

| proc/v/dpath/alu_higher16/U312                          | B2 ^ -> ZN v  | A0I21_X1      | 0.020 | 0.031 | 0.528  | 0.520  |

| proc/v/dpath/alu higher16/U685                          |               | A0I22 X1      | 0.020 | 0.000 | 0.528  | 0.521  |

| proc/v/dpath/alu higher16/U685                          | A1 v -> ZN ^  | A0I22 X1      | 0.035 | 0.047 | 0.574  | 0.567  |

| proc/v/dpath/alu higher16/U686                          |               | NAND2 X2      | 0.035 | 0.000 | 0.574  | 0.567  |

| proc/v/dpath/alu higher16/U686                          | A2 ^ -> ZN v  | NAND2 X2      | 0.029 | 0.044 | 0.618  | 0.611  |

| proc/v/dpath/ex result sel mux X/U89                    |               | A0I222 X1     | 0.029 | 0.002 | 0.621  | 0.613  |

| proc/v/dpath/ex_result_sel_mux_X/U89                    | C2 v -> ZN ^  | A0I222_X1     | 0.054 | 0.112 | 0.732  | 0.725  |

| proc/v/dpath/ex_result_sel_mux_X/U90                    |               | INV_X1        | 0.054 | 0.000 | 0.732  | 0.725  |

| proc/v/dpath/ex_result_sel_mux_X/U90                    | A ^ -> ZN v   | INV_X1        | 0.023 | 0.035 | 0.767  | 0.760  |

| proc/v/dpath/op2 byp mux D/U145                         |               | A0I22 X1      | 0.023 | 0.001 | 0.769  | 0.762  |

| proc/v/dpath/op2_byp_mux_D/U145                         | B2 v -> ZN ^  | A0I22_X1      | 0.029 | 0.052 | 0.821  | 0.814  |

| proc/v/dpath/op2_byp_mux_D/U147                         |               | OAI211_X1     | 0.029 | 0.000 | 0.821  | 0.814  |

| proc/v/dpath/op2_byp_mux_D/U147                         | A ^ -> ZN v   | OAI211_X1     | 0.035 | 0.060 | 0.881  | 0.874  |

| proc/v/dpath/op2 sel mux D/U93                          |               | A0I222 X1     | 0.035 | 0.000 | 0.881  | 0.874  |

| proc/v/dpath/op2 sel mux D/U93                          | C2 v -> ZN ^  | A0I222 X1     | 0.049 | 0.105 | 0.986  | 0.979  |

| proc/v/dpath/op2 sel mux D/U94                          |               | INV X1        | 0.049 | 0.000 | 0.986  | 0.979  |

| proc/v/dpath/op2 sel mux D/U94                          | A ^ -> ZN v   | INV X1        | 0.018 | 0.028 | 1.014  | 1.007  |

| proc/v/dpath/op2 reg X1/U41                             |               | AND2 X1       | 0.018 | 0.000 | 1.014  | 1.007  |

| proc/v/dpath/op2 reg X1/U41                             | A1 v -> ZN v  | AND2 X1       | 0.010 | 0.036 | 1.050  | 1.043  |

| proc/v/dpath/op2_reg_X1/q_reg_2_                        |               | DFF X1        | 0.010 |       | 1.050  | 1.043  |

| +                                                       | ·<br>         |               |       |       |        |        |

| •                                                       |               |               |       |       |        |        |

Figure 15. Gate Level Critical Path for Bypassing X0/X1 Splitted Processor (X1 in figure corresponds to X0 in report)

Figure 16. Critical Path for Bypassing X0/X1 Splitted Processor

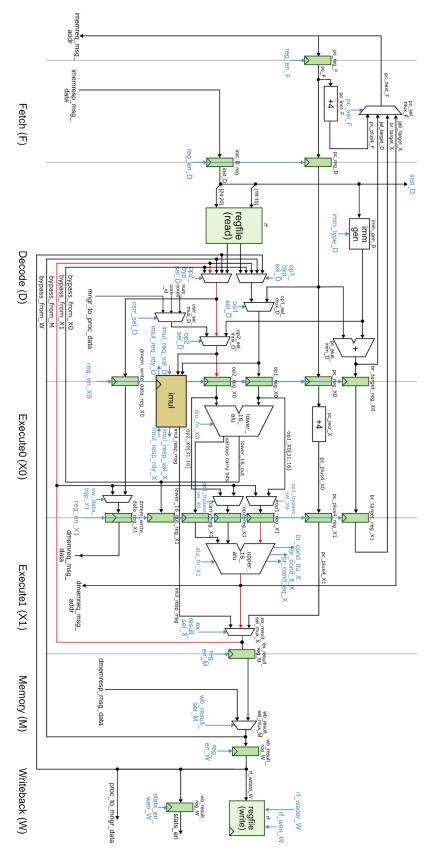

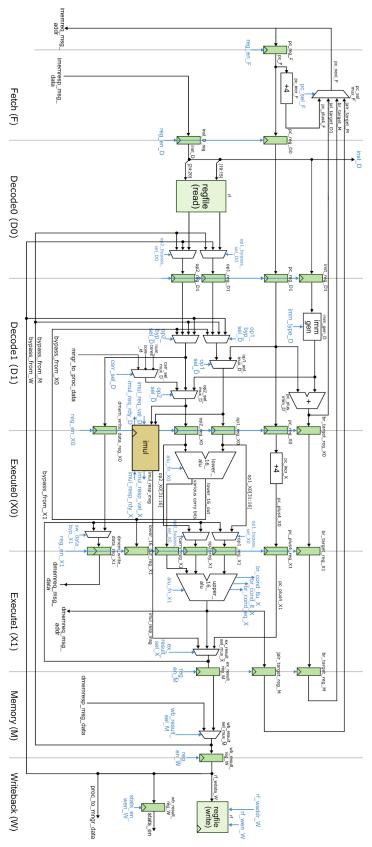

## 4.2 Splitting D Stage into D0/D1

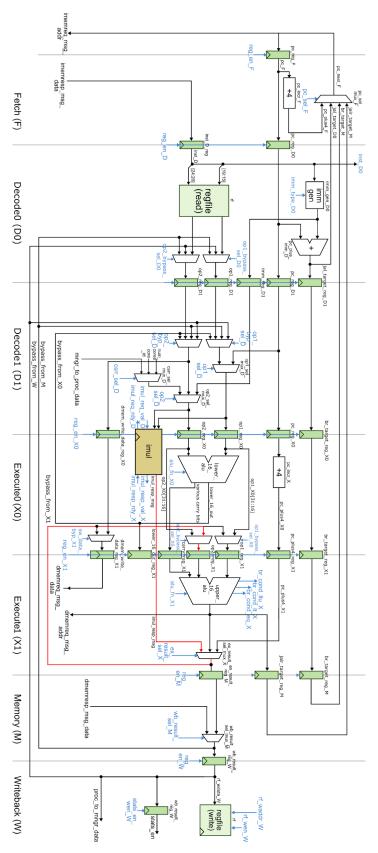

The critical path in section 4.1.1 goes through the register file in stage D as the register file module that we use has sequential write but combinational read, which means everything from reading from the register file to choosing the source of different operands using large muxes has to fit in one cycle. As *figure 15* and *figure 16* shows, both demonstrate a substantial contribution to the critical path. Therefore, we decide to split the D stage right after the register file to reduce the length of the critical path. However, as the register file is physically larger than the area of the bypassing and data selection muxes, the unbalanced D0 and D1 stage might bring a new critical path through the register file. As we are not sure whether the ASIC flow optimizes the register-based design into latch-based design to enable timing-borrowing between stages, the plan is to implement pipeline registers between the register file and the muxes and treat this as an incremental approach to a latch-based balanced design if necessary.

When we pushed the design in 4.1.2 through the ASIC flow, we discovered that the bypassing path from X1 to D becomes a critical path. We thought about rerouting the path to D0, but it achieves nothing as the bypassing path from M to D1 serves the same purpose. M stage also has less combinational logic than X1 so the path is less likely to be a problem. Not being able to come up with a better solution, we decided to erase this path and insert a bubble instead.

Another problem with the new D0/D1 design is that if there is a dependency between instructions in W stage and D0 stage, the data read from the register file will not match the data being written into the register file. Thus we add a bypassing path from W stage to D0 stage specifically for this RAW hazard.

#### 4.2.1 Register-based Design

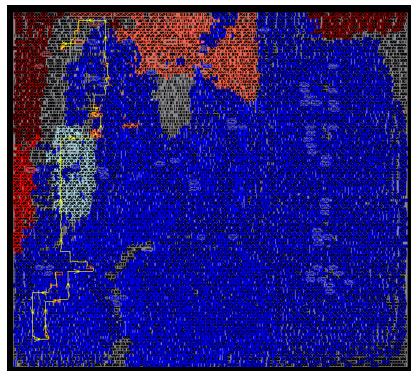

## 4.2.1.a Datapath

As seen in *figure 17*, we decided to insert registers right after op1\_bypass\_mux\_D0 and op2\_bypass\_mux\_D1. The rationale behind this is that we are trying to balance the two stages. While time borrowing using latches might help relax the timing constraint, we still need to properly balance the logic for it to work. The bypassing path mentioned earlier from X1 to D1 is deleted from the data path, and a new bypassing path from W to D0 appears with two muxes to select between register file outputs and bypassing results.