## Mahavir Polytechnic, Nashik

**Department of Artificial Intelligence and Machine Learning**

Year: SY Subject: DTE (313303)

## **UNIT 2: Logic Gates and Boolean Algebra**

Marks: 12

Course Outcome 2: Apply Boolean laws to minimize complex Boolean function.

## **Syllabus:**

- 2.1 Logic Families: Characteristics Parameters of logic Families- Noise margin, Power dissipation, Figure of merit, Fan in, Fan out, Speed of operation Current and Voltage parameters, Comparison of TTL, CMOS and ECL logic family

- 2.2 Introduction to positive and negative logic systems, Logic Gates: Symbol, Truth table of Basic logic gates (AND, OR, NOT) Universal gates (NAND, NOR) and Special purpose gates (EX-OR, EX-NOR)

- 2.3 Buffer: Tristate logic, Unidirectional and Bidirectional

- 2.4 Boolean algebra: Laws of Boolean algebra, Duality Theorem, De-Morgan's theorem

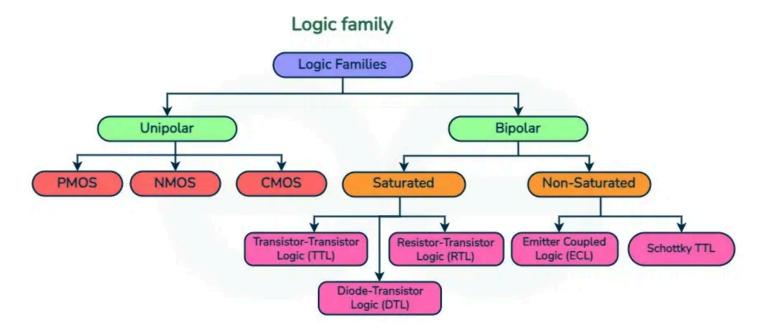

### 2.1 Logic Families

Logic families refer to groups of electronic logic gates that are constructed using similar techniques and have compatible electrical characteristics. These families play a crucial role in digital circuits and systems, as they determine the speed, power consumption, and voltage levels of the circuits. OR

Logic families are different types of technologies being used to build different logic gates. Logic gates are digital circuits that perform basic logic operations like AND, OR, NOT, NAND, and NOR. In other words, it is a group of compatible ICs with the same logic levels and supply voltages fabricated for performing various logical functions. Here, when we say that ICs have the same logic level, we are referring to two types of logic levels that exist.

- In positive logic, 0 is formed by a low voltage level, and a high voltage level forms 1. It means the ON state refers to high voltage as input or output while OFF means low voltage as input or output.

- In negative logic, 0 is formed by a high voltage level, and 1 is formed by a low voltage level. Here, the situation is reversed to that of positive logic. ON means a low voltage input or output while OFF means high voltage as input or output.

Some of the most common logic families detailed Characteristics:

### ☐ TTL (Transistor-Transistor Logic)

Speed: Moderate to high.

Power Consumption: Moderate to high.

Voltage Levels: Typically 5V.

Applications: General-purpose digital circuits, computers, and early microprocessors.

### ☐ CMOS (Complementary Metal-Oxide-Semiconductor)

Speed: Moderate to high (modern CMOS can be very fast).

Power Consumption: Very low (especially in static conditions).

Voltage Levels: Wide range (typically 3.3V, 5V, or lower in modern systems).

Applications: Microprocessors, microcontrollers, memory devices, and most modern digital circuits.

### □ ECL (Emitter-Coupled Logic)

Speed: Very high.

Power Consumption: Very high. Voltage Levels: Typically -5.2V.

Applications: High-speed computing and communication systems.

### **Characteristics (Parameters) of Logic Families**

Even though there are various logic families, the general characteristics, their definitions, nomenclature and terminologies used for all of them have been standardized.

### 1. Voltage and Current Parameters:

### **Voltage Parameters (Threshold Levels):**

Ideally, the input voltage levels of 0V and +5V (for TTL) are called logic 0 and 1 levels respectively.

However, practically we will not always obtain voltage levels matching exactly to these values. Therefore it is necessary to define the worst-case input voltages.

## $V_{IL(max)}$ – worst case low level input voltage:

This is the maximum value of input voltage which will be considered as a logic 0 level. If the input voltage is higher than VIL(max), then it will not be treated as a low (0) input level.

### V<sub>IH(min)</sub> – worst case high level input voltage:

This is the minimum value of input voltage which will be considered as a logic 1 level. If the input voltage is lower than VIH(min), then it will not be treated as a high (1) input level.

### $V_{OH(min)}$ – worst case high level output voltage:

This is the minimum value of output voltage which will be considered as a logic 1 level. If the output voltage is lower than VOH(min), then it will not be treated as a high (1) output level.

## $V_{OL(max)}-$ worst-case low-level output voltage:

This is the maximum value of output voltage which will be considered as a logic 0 level. If the input voltage is higher than VOL(max), then it will not be treated as a low (0) output level.

#### **Current Parameters:**

### IIL – Low-level input Current:

It is the current that flows into the input when a low level input voltage in the specified range is applied.

### IIH – High-level input Current:

It is the current that flows into the input when a high level input voltage in the specified range is applied.

### **IOL – Low-level output Current:**

It is the current that flows from the output when the output voltage is in the specified low voltage range and specified load is applied.

### **IOH – High-level Output Current:**

It is the current that flows from the output when the output voltage is in the specified high voltage range and specified load is applied.

## Fan-in and Fan-out:

#### Fan-in:

Fan in is defined as number of inputs a gate a has. For example, a two input gate will have a fan-in is equal to 2

#### Fan-out:

Fan-out is defined as the maximum number of output

Higher fan-out, higher the current supplying capacity of a gate. For example a fan-out of 5 indicates that the gate can drive (supply current to) at the most 5 inputs of the same IC family.

### **Noise Margin:**

To understand the meaning of the term "Noise Margin" or "Noise Immunity", refer to the input and output voltage profiles

Noise is unwanted electrical disturbances that may induce some voltage in the connecting wires used between two gates or from a gate output to load.

Noise immunity is defined as the ability of a logic circuit to tolerate the noise without causing any unwanted changes in the output.

### **Propagation Delay(Speed of operation):**

The output of logic does not change its state instantaneously in response to the change in the state of the input.

There is a time delay between those two events, which is called the propagation delay.

Thus propagation delay is defined as the time delay between the instant of application of an input pulse and the instant of occurrence of the corresponding output pulse.

### **Power Dissipation:**

As a result of applied voltage and currents flowing through the logic families (ICs), some power will be dissipated in it in the form of heat.

The power is in milliwatts.

Care should be taken to reduce the power dissipation taking place in the logic ICs in order to protect the ICS against damage due to excessive heat, to reduce the loading on power supplies, etc

### **Operating Temperature:**

The temperature range acceptable for the consumer and industrial applications is 0° and 70° C and that for the military applications is -55° to 125° C.

The performance of gates will be in the specified limits over these temperature ranges.

### **Figure of Merit (Speed Power Product SPP):**

The figure of merit of a logical family is the product of power dissipation and propagation delay.

It is called the speed-power product. The speed is specified in seconds and power is specified in watts

Figure if Merit = Propagation delay time x Power dissipation

Practically, the value of the figure of merit should be as low as possible.

### Comparison of TTL, CMOS and ECL logic family

| Parameters           | TTL                                   | CMOS                                                                           | ECL                                    | RTL                                                 |  |

|----------------------|---------------------------------------|--------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------------------|--|

| Basic element        | Transistors, diodes, and resistors    | MOSFETs                                                                        | Resistor and transistors               | resistor and transistors                            |  |

| Fan out              | moderate                              | highest(~50)                                                                   | high                                   | low                                                 |  |

| Propagation<br>Delay | 10ns                                  | 70 <b>ns</b>                                                                   | 2ns                                    | 12ns                                                |  |

| Noise margin         | moderate                              | high                                                                           | low                                    | poor                                                |  |

| Power<br>dissipation | 10mW                                  | 0.1mW                                                                          | 40-50 <b>m</b> W                       | 30mW                                                |  |

| Circuit complexity   | complex                               | moderately complex                                                             | complex                                | simple                                              |  |

| Basic gate           | NAND gate                             | NAND/NOR                                                                       | OR/NOR                                 | NOR gate                                            |  |

| Application          | Oscilloscopes,<br>measurement devices | battery-powered circuits due to low<br>power consumption, mobile<br>equipments | high-speed<br>switching<br>application | practically obsolete<br>due to poor noise<br>margin |  |

## 2.2 Logic Gates: Symbol, Truth table

- Logic gates are the fundamental components of all digital circuits and systems.

- In digital electronics, there are seven main types of logic gates used to perform various logical operations.

- A logic gate is basically an electronic circuit designed by using components like diodes, transistors, resistors, capacitors, etc.,

- As the name implies, a logic gate is designed to perform logical operations in digital systems like computers, communication systems, etc

## Types of logic gate are

There are 7 types of gates

### 1. Basic Logic Gates

There are three basic logic gates:

AND Gate

OR Gate

NOT Gate

## 2. Universal Logic Gates

In digital electronics, the following two logic gates are considered as universal logic gates:

**NOR Gate**

NAND Gate

### 3. Derived Logic Gates

The following two are the derived logic gates used in digital systems:

**XOR** Gate

**XNOR Gate**

## 2.2.1 Basic Logic Gates

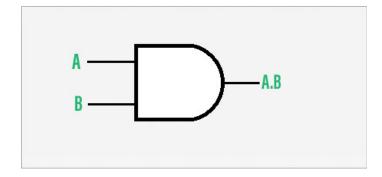

#### 1. AND Gate

- In digital electronics, the AND gate is one of the basic logic gate that performs the logical multiplication of inputs applied to it.

- Symbol:

Z=A.B

Where, A and B are inputs to the AND gate, while Z denotes the output of the AND gate.

| Inj | put | Output  |  |

|-----|-----|---------|--|

| A   | В   | A AND B |  |

| 0   | 0   | 0       |  |

| 0   | 1   | 0       |  |

| 1   | 0   | 0       |  |

| 1   | 1   | 1       |  |

### 2. OR Gate

- The primary function of the OR gate is to perform the logical sum operation.

- The boolean expression for a two input OR gate is given by,

$$Z = A + B$$

- Here, A, B, and C are inputs and Z is the output variables. We can extend this boolean expression to any number of input variables.

- Symbol:

| Inj | out | Output |

|-----|-----|--------|

| A   | В   | A OR B |

| 0   | 0   | 0      |

| 0   | 1   | 1      |

| 1   | 0   | 1      |

| 1   | 1   | 1      |

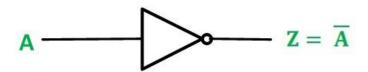

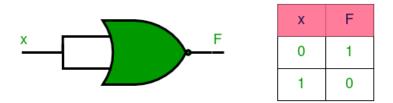

## 3. NOT gate

- In digital electronics, the NOT gate is another basic logic gate used to perform compliment of an input signal applied to it.

- It takes only one input and one output. The output of the NOT gate is complement of the input applied to it

- The NOT gate is also known as inverter, as it performs the inversion operation.

$$Z = \overline{A}$$

The bar over the input variable A represents the inversion operation.

• Symbol:

| Input | Output |

|-------|--------|

| A     | NOT A  |

| 0     | 1      |

| 1     | 0      |

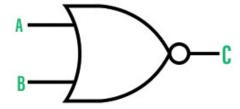

#### 4. NOR Gate

- The NOR gate is a type of universal logic gate that can take two or more inputs but one output.

- It is basically a combination of two basic logic gates i.e., OR gate and NOT gate. Thus, it can be expressed as,

NOR Gate =

$$OR$$

Gate +  $NOT$  Gate

- In other words, a NOR gate is an OR gate followed by a NOT gate

- The boolean expression of a two input NOR gate is given below:

$$Z = \overline{A + B}$$

• Symbol:

| lnį | out | Output  |

|-----|-----|---------|

| Α   | В   | A NOR B |

| 0   | 0   | 1       |

| 0   | 1   | 0       |

| 1   | 0   | 0       |

| 1   | 1   | 0       |

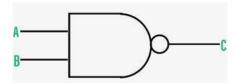

### 5. NAND Gate

- In digital electronics, the NAND gate is another type of universal logic gate used to perform logical operations.

- The NAND gate performs the inverted operation of the AND gate. Similar to NOR gate, the NAND gate can also have two or more input lines but only one output line.

- The NAND gate is also represented as a combination of two basic logic gates namely, AND gate and NOT gate. Hence, it can be expressed as

• Here is the boolean expression of a two input NAND gate.

$$C = \overline{AB}$$

In this expression, A and B are the input variables and C is the output variable.

We can extend this relation to any number of input variables like three, four, or more.

• Symbol:

| Inp | out | Output   |

|-----|-----|----------|

| Α   | В   | A NAND B |

| 0   | 0   | 1        |

| 0   | 1   | 1        |

| 1   | 0   | 1        |

| 1   | 1   | 0        |

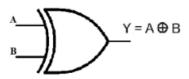

### 6. XOR gate

- In digital electronics, there is a specially designed logic gate named, XOR gate, which is used in digital circuits to perform modulo sum.

- It is also referred to as Exclusive OR gate or Ex-OR gate.

- The XOR gate can take only two inputs at a time and give an output.

- The output of the XOR gate is high or logic 1 only when its two inputs are dissimilar.

The operation of the XOR gate can be described through a mathematical equation called its boolean expression. The following is the boolean expression for the output of the XOR gate.

$$C = A \oplus B$$

Here, C is the output variable, and A and B are the input variables.

This expression can also be written as follows:

$$C = A\overline{B} + \overline{A}\mathbf{B}$$

• Symbol:

• Truth Table:

| Inp | out | Output  |

|-----|-----|---------|

| Α   | В   | A XOR B |

| 0   | 0   | 0       |

| 0   | 1   | 1       |

| 1   | 0   | 1       |

| 1   | 1   | 0       |

### 7. XNOR Gate

- The XNOR gate is another type of special purpose logic gate used to implement exclusive operation in digital circuits.

- It is used to implement the Exclusive NOR operation in digital circuits.

- It is also called the Ex-NOR or Exclusive NOR gate.

- It is a combination of two logic gates namely, XOR gate and NOT gate. Thus, it can be expressed as,

$$XNOR Gate = XOR Gate + NOT Gate$$

The output of an XNOR gate is high or logic 1 when its both inputs are similar. Otherwise the output is low or logic 0.

Here is the boolean expression of the XNOR gate.

$$C = \overline{A \oplus B}$$

We can also write this expression as follows:

$$C = AB + \overline{AB}$$

Here, the A and B are inputs and Y is the output.

• Symbol:

• Truth Table:

| Inj | out | Output   |

|-----|-----|----------|

| A   | В   | A XNOR B |

| 0   | 0   | 1        |

| 0   | 1   | 0        |

| 1   | 0   | 0        |

| 1   | 1   | 1        |

## **Applications of Logic Gates**

- Computers

- Microprocessors

- Microcontrollers

- Digital and smart watches

• Smartphones, etc.

## 2.3 Boolean algebra: Laws of Boolean algebra

- Boolean algebra is the category of algebra

- It is used to analyze and simplify digital circuits or digital gates.

- It is also called Binary Algebra or logical Algebra.

- It has been fundamental in the development of digital electronics and is provided for in all modern programming languages.

## Laws of Boolean Algebra

There are six types of Boolean algebra laws. They are:

- Commutative law

- Associative law

- Distributive law

- AND law

- OR law

- Inversion law

#### 1. Commutative law

- Any binary operation which satisfies the following expression is referred to as a commutative operation.

- Commutative law states that changing the sequence of the variables does not have any effect on the output of a logic circuit.

$$A. B = B. A$$

$$A + B = B + A$$

#### 2. Associative Law

• It states that the order in which the logic operations are performed is irrelevant as their effect is the same.

$$(A.B).C = A.(B.C)$$

$(A+B)+C = A+(B+C)$

#### 3. Distributive Law

• Distributive law states the following conditions:

$$A. (B + C) = (A. B) + (A. C)$$

$$A + (B. C) = (A + B) \cdot (A + C)$$

### 4. AND Law

• These laws use the AND operation. Therefore they are called AND laws.

$$\mathbf{A} \cdot \mathbf{0} = \mathbf{0}$$

$$\mathbf{A} \cdot \mathbf{1} = \mathbf{A}$$

$$A. A = A$$

$$A.\overline{A} = 0$$

### 5. OR Law

• These laws use the OR operation. Therefore they are called OR laws.

$$\mathbf{A} + \mathbf{0} = \mathbf{A}$$

$$\mathbf{A} + \mathbf{1} = \mathbf{1}$$

$$A + A = A$$

$$A + \overline{A} = 1$$

### 6. Inversion Law

• In Boolean algebra, the inversion law states that double inversion of variable results in the original variable itself.

$$\bar{A} = A$$

## De Morgan's First Law:

De Morgan's First Law states that

$$\overline{(AB)} = \overline{(A + \overline{B})}$$

The first law states that the complement of the product of the variables is equal to the sum of their individual complements of a variable.

The truth table that shows the verification of De Morgan's First law is given as follows:

| A | В | $\overline{A}$ | $\overline{B}$ | $\overline{(AB)}$ | $\overline{(A + B)}$ |

|---|---|----------------|----------------|-------------------|----------------------|

| 0 | 0 | 1              | 1              | 1                 | 1                    |

| 0 | 1 | 1              | 0              | 1                 | 1                    |

| 1 | 0 | 0              | 1              | 1                 | 1                    |

| 1 | 1 | 0              | 0              | 0                 | 0                    |

The last two columns show that  $\overline{(AB)} = \overline{(A + B)}$

Hence, De Morgan's First Law is proved.

## De Morgan's Second law:

De Morgan's Second law states that  $\overline{(A + B)} = \overline{(A \cdot B)}$

The second law states that the complement of the sum of variables is equal to the product of their individual complements of a variable.

The following truth table shows the proof for De Morgan's second law.

| A | В | $\overline{A}$ | $\overline{\overline{B}}$ | $\overline{(A+B)}$ | $\overline{(A \cdot B)}$ |

|---|---|----------------|---------------------------|--------------------|--------------------------|

| 0 | 0 | 1              | 1                         | 1                  | 1                        |

| 0 | 1 | 1              | 0                         | 0                  | 0                        |

| 1 | 0 | 0              | 1                         | 0                  | 0                        |

| 1 | 1 | 0              | 0                         | 0                  | 0                        |

The last two columns show that  $\overline{(A + B)} = \overline{(A \cdot B)}$

Hence, De Morgan's second law is proved.

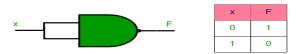

## 2.5 Implementation of Basic Gate using Universal gates.

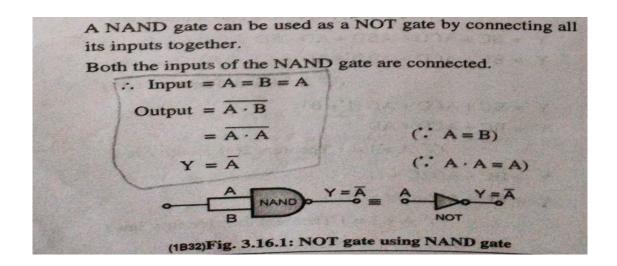

## 2.5.1 Implementation of NOT Gate using NAND gate:

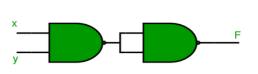

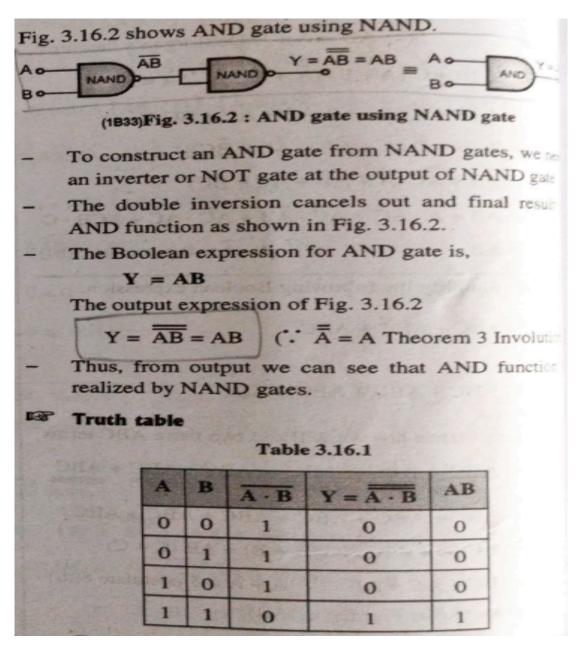

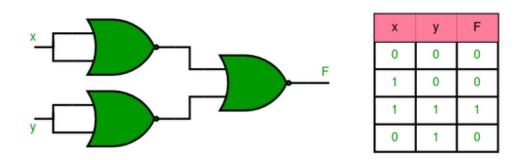

## 2.5.2 Implementation of AND Gate using NAND gate:

The AND gate can be implemented by using two NAND gates in the below fashion:

| x | у | F |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

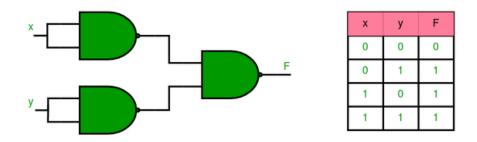

### 2.5.3 Implementation of OR Gate using NAND gate:

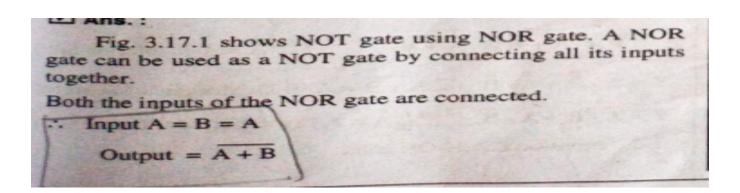

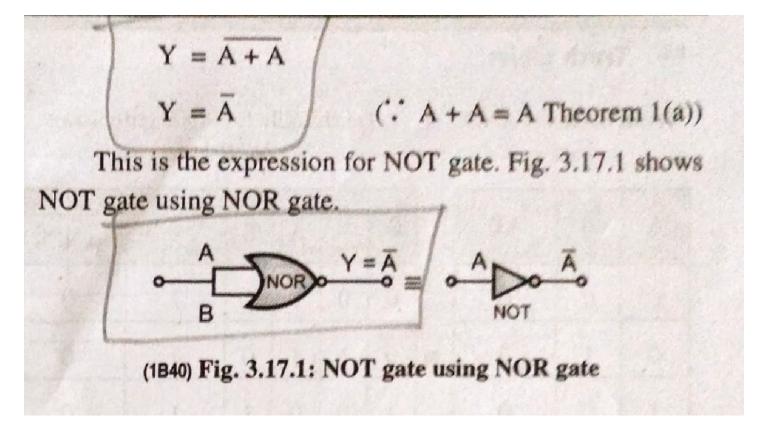

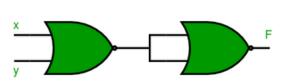

### 2.5.4 Implementation of NOT Gate using NOR gate:

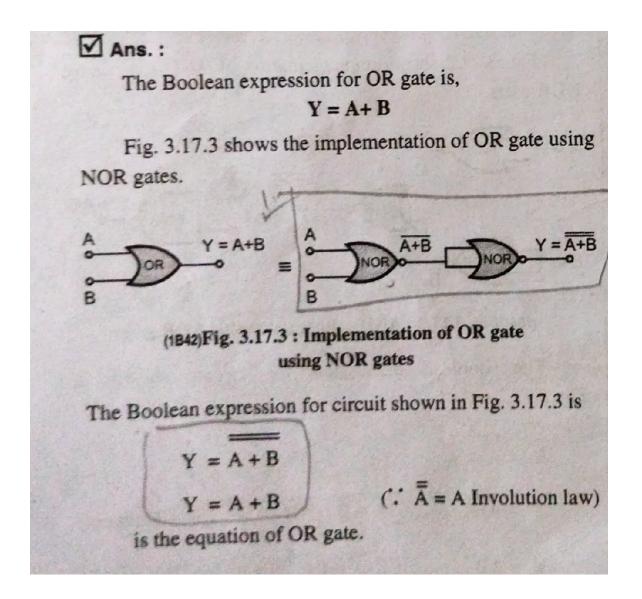

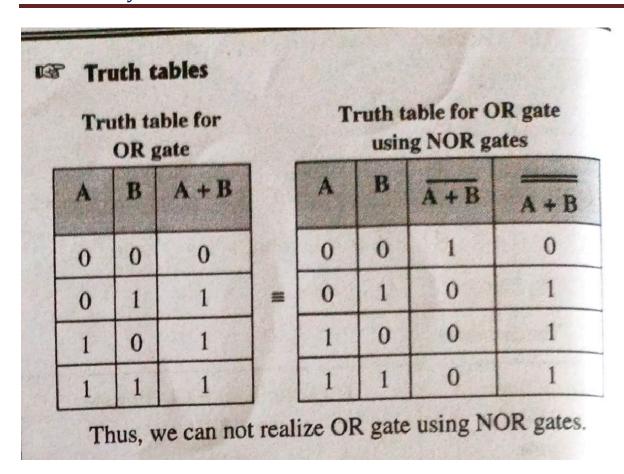

### 2.5.5 Implementation of OR Gate using NOR gate:

| х | у | F |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

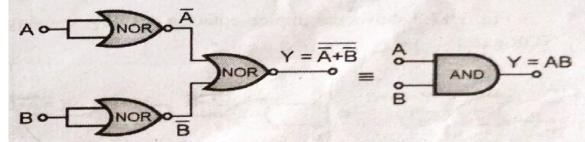

## 2.5.6 Implementation of AND Gate using NOR gate:

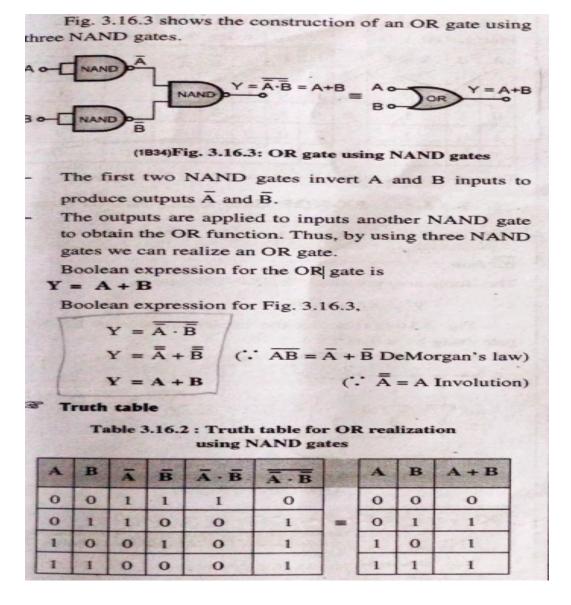

Fig. 3.17.2 shows implementation of AND gate using NOR gates.

# (1841)Fig. 3.17.2: AND neither gate using NOR gate

The Boolean expression for circuit shown in Fig. 3.17.2 is,

$$Y = \overline{\overline{A} + \overline{B}}$$

$Y = \overline{\overline{AB}}$  (:  $\overline{\overline{A}} + \overline{\overline{B}} = \overline{AB}$  DeMorgan's Theorem)

$Y = AB$  (:  $\overline{\overline{A}} = 1$  Involution law Theorem 3)

is the equation of AND gate.

| Truth table for AND gate |   |    |   | Truth table for AND gate using NOR gates |   |   |   |                     |                               |

|--------------------------|---|----|---|------------------------------------------|---|---|---|---------------------|-------------------------------|

| A                        | В | AB | 1 | A                                        | В | Ā | Ē | $\bar{A} + \bar{B}$ | $\overline{A} + \overline{B}$ |

| 0                        | 0 | 0  |   | 0                                        | 0 | 1 | 1 | 1                   | 0                             |

| 0                        | 1 | 0  | = | 0                                        | 1 | 1 | 0 | 1                   | 0                             |

| 1                        | 0 | 0  |   | 1                                        | 0 | 0 | 1 | 1 .                 | 0                             |

| 1                        | 1 | 1  |   | 1                                        | 1 | 0 | 0 | 0                   | 1                             |

Thus, we can realize AND gate using NOR gates.

## **Example of Boolean Algebra:**

Ex. 4.15.1: Use De-Morgan's theorem to simplify the following Boolean expression.

$$Y = \overline{AB} + \overline{AB}$$

Soln. :

$$Y = \overline{AB + AB}$$

$$Y = \overline{AB} \cdot \overline{AB}$$

[De-Morgan's law:

$$(\overline{A} + \overline{B}) = \overline{A} \cdot \overline{B}$$

]

$$Y = (\overline{\overline{A}} + \overline{B}) \cdot (\overline{A} + \overline{\overline{B}})$$

$$Y = (A + \overline{B}) \cdot (\overline{A} + B)$$

[Inversion law :  $\overline{\overline{A}} = A$ ]

$$Y = AA + AB + \overline{AB} + BB$$

[AND law:

$$A \cdot \overline{A} = 0$$

,  $B \cdot \overline{B} = 0$ ]

[Distributive law:

$$\overline{A} + AB = \overline{A} + B$$

]

$$Y = AB + \overline{AB}$$

Ex. 4.15.2 : Verify the following Boolean function

$$AB + \overline{AC} + BC = AB + \overline{AC}$$

Soln.:

L.H.S. =  $AB + \overline{AC} + BC$

=  $AB + \overline{AC} + BC \cdot L$

=  $AB + \overline{AC} + BC \cdot (A + \overline{A})$

[OR law:  $A + \overline{A} = 1$ ]

=  $AB + \overline{AC} + ABC + \overline{ABC}$

=  $AB + \overline{AC} + ABC + \overline{ABC}$

[OR law:  $(1 + C) = (1 + B) = 1$ ]

=  $AB + \overline{AC} = R.H.S$ . Hence Proved

UEx. 4.15.19 (MSBTE - Q. 4(b), W-17, 4 Marks)

Simplify following equation using boolean algebra and decircuit diagram:

$$Y = \overline{A} (A + \overline{B}) + \overline{B} (\overline{A} + B).$$

$$Y = \overline{A} (A + \overline{B}) + \overline{B} (\overline{A} + B).$$

$$= \overline{A} A + \overline{A} B + \overline{A} B + \overline{B} B$$

$$= O + \overline{A} B + \overline{A} B + \overline{B}$$

$$= \overline{A} B + \overline{A} B$$

$$= \overline{A} B [OR law : A + A = A]$$

$$A \longrightarrow \overline{A}$$

$$B \longrightarrow \overline{B} AND Y = \overline{A} B$$