# UTN

## FACULTAD REGIONAL AVELLANEDA

**Teoría sobre el transistor de potencia IGBT**

**CATEDRA: Electrónica de Potencia**

**PROFESOR: Ing. Daniel Graff**

# Indice

|                                                                                         |           |

|-----------------------------------------------------------------------------------------|-----------|

| <b><u>1. Introducción</u></b>                                                           | <b>4</b>  |

| <b><u>2. Tabla comparativa:</u></b>                                                     | <b>4</b>  |

| <b><u>3. Estructura</u></b>                                                             | <b>4</b>  |

| <b><u>3-1. Operación durante el encendido (turn-on)</u></b>                             | <b>5</b>  |

| <b><u>3-2. Operación durante el apagado (turn-off)</u></b>                              | <b>6</b>  |

| <b><u>3-3. Latch-up</u></b>                                                             | <b>7</b>  |

| <b><u>4. SOA (Safe-Operating-Area)</u></b>                                              | <b>7</b>  |

| <b><u>4-1. FBSOA (Forward Biased Safe-Operating-Area)</u></b>                           | <b>7</b>  |

| <b><u>4-2. RBSOA (Reverse Biased Safe-Operating-Area, Turn-Off SOA)</u></b>             | <b>8</b>  |

| <b><u>4-3. SCSOA (Short Circuit Safe-Operating-Area)</u></b>                            | <b>9</b>  |

| <b><u>5. Características de conducción</u></b>                                          | <b>9</b>  |

| <b><u>5-1. Características de transferencia estáticas</u></b>                           | <b>9</b>  |

| <b><u>5-2. Switchback</u></b>                                                           | <b>10</b> |

| <b><u>5-3. Dependencia con la temperatura</u></b>                                       | <b>10</b> |

| <b><u>6. Transconductancia</u></b>                                                      | <b>12</b> |

| <b><u>7. Interpretación de la hoja de datos</u></b>                                     | <b>12</b> |

| <b><u>7-1. Nomenclatura</u></b>                                                         | <b>13</b> |

| <b><u>7-2. Case Outline – TO-247AC</u></b>                                              | <b>13</b> |

| <b><u>7-3. Absolute Maximum Ratings</u></b>                                             | <b>14</b> |

| <b><u>7-3-1. Tensión de colector – emisor (Vces)</u></b>                                | <b>14</b> |

| <b><u>7-3-2. Corriente continua de colector (Ic)</u></b>                                | <b>14</b> |

| <b><u>7-3-3. Corriente pulsante de colector (Icm)</u></b>                               | <b>15</b> |

| <b><u>7-3-4. Corriente de carga inductiva con clamping (ILM)</u></b>                    | <b>16</b> |

| <b><u>7-3-5. Corriente continua y máxima del diodo en directa (IF y IFM)</u></b>        | <b>17</b> |

| <b><u>7-3-6. Tensión gate - emisor (Vge)</u></b>                                        | <b>18</b> |

| <b><u>7-3-7. Potencia disipada (PD)</u></b>                                             | <b>18</b> |

| <b><u>7-3-8. Temperatura de juntura (Tj) y temperatura de almacenamiento (Tstg)</u></b> | <b>18</b> |

| <b><u>7-3-9. Tiempo de sostenimiento de corto circuito (Tsc)</u></b>                    | <b>18</b> |

| <b><u>7-4. Thermal Resistance</u></b>                                                   | <b>19</b> |

| <b><u>7-4-1. Resistencia térmica de juntura al ambiente (R<sub>θja</sub>)</u></b>       | <b>20</b> |

| <b><u>7-4-2. Resistencia térmica de juntura a carcaza (R<sub>θjc</sub>)</u></b>         | <b>20</b> |

| <b><u>7-4-3. Resistencia térmica de carcaza a disipador (R<sub>θcs</sub>)</u></b>       | <b>20</b> |

| <b><u>7-4-4. Resistencia térmica de disipador al ambiente (R<sub>θsa</sub>)</u></b>     | <b>22</b> |

|                                                                           |           |

|---------------------------------------------------------------------------|-----------|

| <b><u>7-5. Transient Thermal Impedance (Zthjc)</u></b>                    | <b>24</b> |

| <b><u>7-6. Electrical Characteristics</u></b>                             | <b>27</b> |

| <u>7-6-1. Tensión de breakdown entre colector y emisor (V(br)ces)</u>     | 27        |

| <u>7-6-2. Tensión de breakdown entre emisor y colector (V(br)ecs)</u>     | 28        |

| <u>7-6-3. Tensión de saturación entre colector y emisor (Vce(on))</u>     | 28        |

| <u>7-6-4. Tensión de umbral entre emisor y gate (Vge(th))</u>             | 29        |

| <u>7-6-5. Transconductancia directa (gfe)</u>                             | 29        |

| <u>7-6-6. Corriente de corte de colector (Ices)</u>                       | 30        |

| <u>7-6-7. Corriente de fuga entre gate y emisor (Iges)</u>                | 30        |

| <u>7-6-8. Caída en directa del diodo (VFM)</u>                            | 30        |

| <b><u>7-7. Switching Characteristics</u></b>                              | <b>31</b> |

| <u>7-7-1. Inductancia interna del emisor (Le)</u>                         | 31        |

| <u>7-7-2. Capacitores interelectródicos del gate</u>                      | 31        |

| <u>7-7-3. Carga del gate</u>                                              | 33        |

| <u>7-7-4. Potencia promedio entregada por el driver</u>                   | 35        |

| <u>7-7-5. Resistencia en serie al gate (Rg)</u>                           | 35        |

| <u>7-7-6. Análisis de la transición durante el encendido y el apagado</u> | 37        |

| <u>7-7-7. Tiempos de conmutación</u>                                      | 40        |

| <u>7-7-8. Energía de conmutación</u>                                      | 41        |

| <u>7-7-9. Características del diodo</u>                                   | 43        |

| <b><u>8. Referencias</u></b>                                              | <b>45</b> |

# Teoría de los IGBTs (insulated gate bipolar transistor)

## 1. Introducción

Un transistor de potencia MOSFET permite ser manejado mediante un simple diseño de control de gate y tiene una excelente capacidad en conmutaciones rápidas, su desventaja es el rápido incremento de la RDS(on) y de la tensión de breakdown a tensiones superiores a los 200 V.

El transistor de potencia BIPOLAR tiene excelentes características durante el encendido debido a su baja caída de tensión que posee en directa, pero su desventaja es el complejo diseño de control de la base en operaciones donde se requiera conmutaciones rápidas.

El transistor de potencia IGBT tiene combinada las ventajas de los dos dispositivos mencionados, tiene en su entrada la estructura de un MOS la cual permite un simple diseño de control y conmutar a velocidades muy altas. Su salida tiene la estructura de un BIPOLAR, siendo superior su capacidad de corriente que este último.

Bajo estas condiciones, el IGBT es usado extensamente en aplicaciones de media y alta tensión y corriente como alternativa a los MOSFETs, BIPOLARES, TIRISTORES, etc.

## 2. Tabla comparativa:

| Features                   | BJT                    | MOSFET                | IGBT    |

|----------------------------|------------------------|-----------------------|---------|

| <b>Drive Method</b>        | Current                | Voltage               | Voltage |

| <b>Drive Circuit</b>       | Complex                | Simple                | Simple  |

| <b>Input Impedance</b>     | Low                    | High                  | High    |

| <b>Drive Power</b>         | High                   | Low                   | Low     |

| <b>Switching Speed</b>     | Slow ( $\mu$ s)        | Fast (ns)             | Middle  |

| <b>Operating Frequency</b> | Low (less than 100kHz) | Fast (less than 1MHz) | Middle  |

| <b>S.O.A.</b>              | Narrow                 | Wide                  | Wide    |

| <b>Saturation Voltage</b>  | Low                    | High                  | Low     |

## 3. Estructura

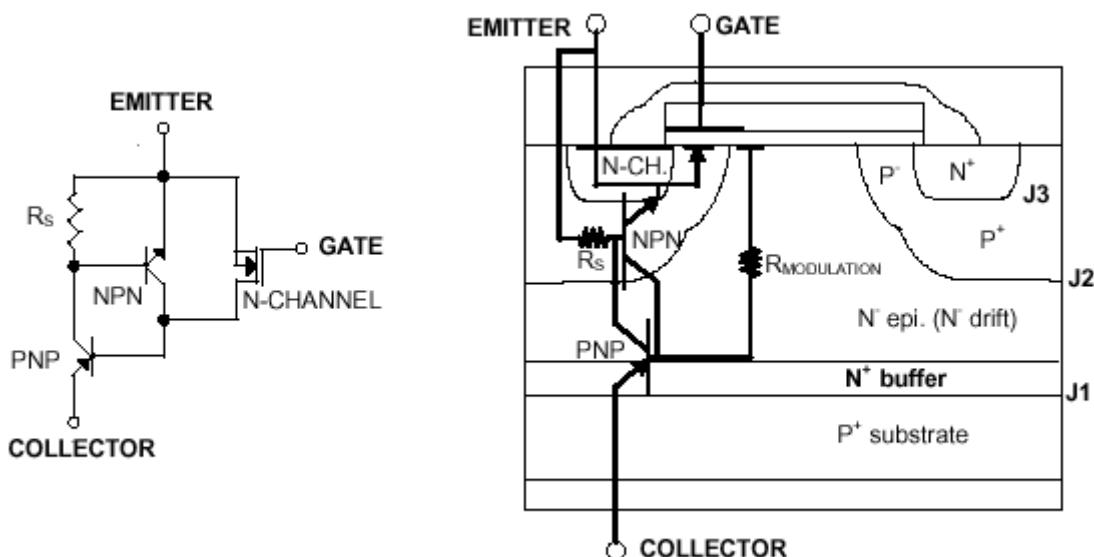

La corriente de la base del transistor PNP es alimentada a través del canal de entrada, además de este existe un transistor NPN, el cual se diseña para volverse inactivo cortocircuitando la base y el emisor al terminal source del MOSFET.

Las 4 capas de PNPN, que abarca a los dos transistores forman la estructura de un tiristor, el cual causa la posibilidad de un latch-up.

A diferencia del MOSFET, no tiene un diodo en inversa que exista parásitamente por construcción.

Un IGBT es llamado asimétrico cuando hay una capa buffer N+ entre la capa de sustrato P+ y la región drift N-, de otra manera es llamado simétrico. La capa buffer N+ mejora la velocidad de apagado reduciendo la inyección de los portadores minoritarios e incrementando la tasa de recombinación durante la conmutación.

Las características de latch-up también son mejoradas reduciendo la ganancia de corriente del transistor PNP, el problema es que la caída en directa incrementa. Sin embargo el espesor de la región drift N- puede ser reducida con la misma capacidad de bloqueo de la tensión en directa, porque la capa buffer N+ mejora esa capacidad, aminorando la caída en directa.

Un IGBT asimétrico tiene mejores características en velocidad de conmutación y caída de tensión.

La capacidad de bloqueo en directa y en inversa son aproximadamente iguales porque ambos son determinados por el mismo espesor de la capa drift N- y por la misma resistencia. La tensión de bloqueo inverso de un IGBT asimétrico que contiene la capa buffer N+ entre el sustrato P+ y la región drift N- es aminorada a unas decenas de volts debido a la existencia de un pesado dopaje en ambos lados de J1.

### 3-1. Operación durante el encendido (turn-on)

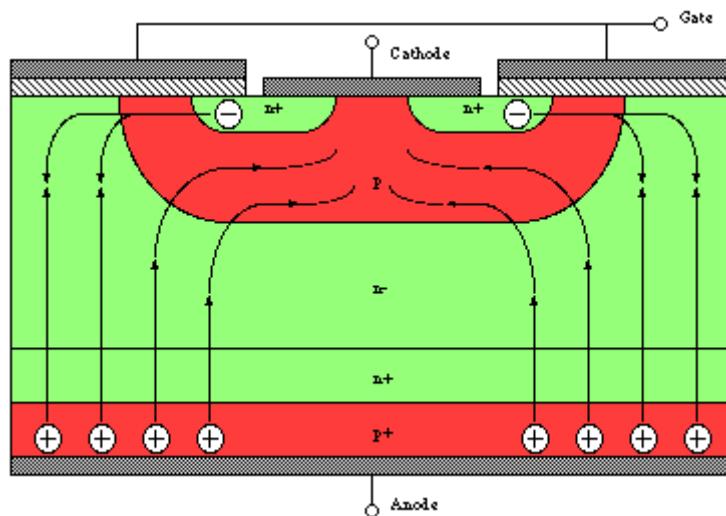

La conducción en el dispositivo comienza con un valor de tensión de gate mayor a la tensión de umbral. Esta provoca un estrangulamiento del canal P, bajo el gate, el cual provee un canal tipo N que vincula al emisor del IGBT con la región N-. Los electrones son inyectados por el emisor N+ a la zona N-, estos representan la corriente de base del PNP, mientras que al mismo tiempo la juntura J1, que se polariza en directa porque el potencial ánodo – cátodo del PNP es mayor a 0,7 V, está inyectando lagunas desde la región P+ en N-.

Esta inyección provoca la modulación de la conductividad de la región N-, donde las densidades de laguna – electrón son varias ordenes de magnitud mayor que la original región N- con impurezas.

Esta modulación de conductividad le otorga al IGBT su baja tensión en el estado de conducción, debido a que se reduce la resistencia de la región N-. Algunas de las lagunas inyectadas, se recombinarán en la zona N-, mientras que otras se difundirán y alcanzarán la juntura con la región tipo P, donde serán recolectadas.

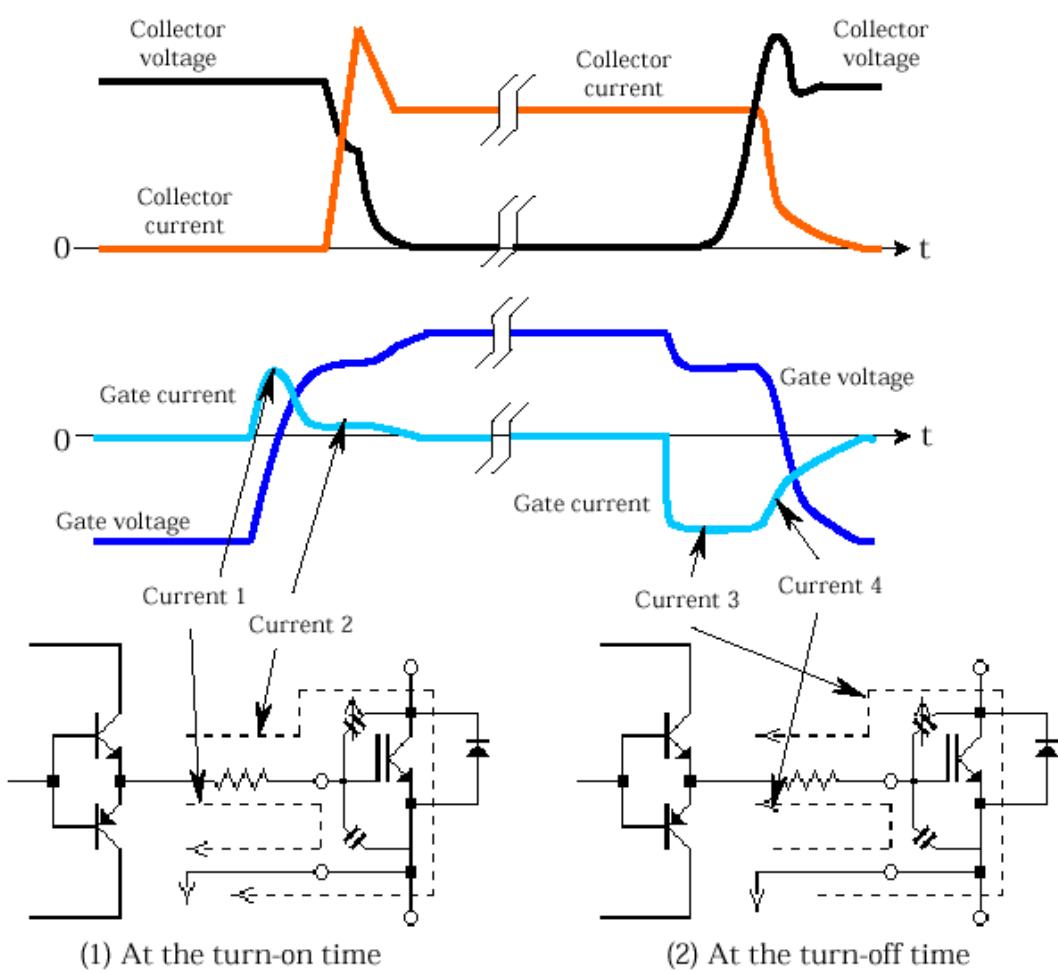

La siguiente figura muestra como fluyen los electrones que son inyectados por el source del MOS dentro de la región drift N-, mientras que al mismo tiempo la juntura J1, la cual está polarizada en directa inyecta lagunas dentro de la misma región.

Hay dos clases de corriente que fluyen en el terminal emisor, una es la corriente de electrones proveniente del MOS que fluye a través del canal y la otra es la corriente de lagunas provenientes del BIPOLAR que fluye a través de la juntura J2.

### 3-2. Operación durante el apagado (turn-off)

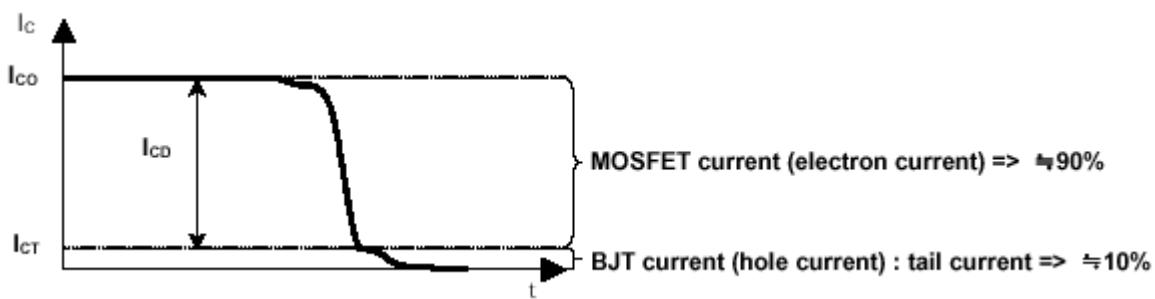

Cuando la tensión del gate cae por debajo de la tensión de umbral, la capa de inversión no puede ser mantenida y la alimentación de electrones en la región N- es bloqueada, punto en el cual el proceso de apagado comienza, sin embargo no puede ser apagado rápidamente debido a la alta concentración de portadores minoritarios en la región N- durante la conducción en directa.

Primero la corriente de colector decrece rápidamente debido a la cesación de corriente de electrones a través del canal, y luego el colector reduce gradualmente su corriente cuando la densidad de portadores minoritarios decae debido a la recombinación.

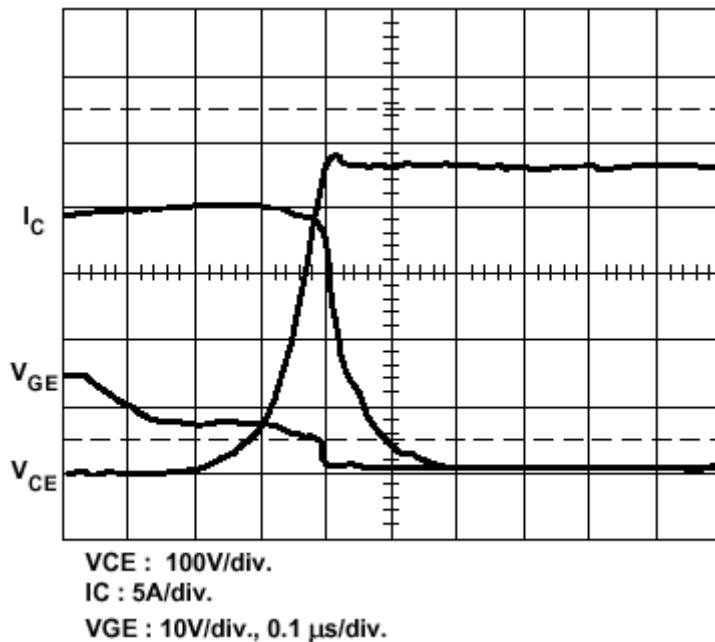

Como muestra la figura la corriente de colector cae a cero en dos etapas.

El tiempo de vida de los portadores minoritarios en la región drift N- incrementa con el incremento de la temperatura, esto no solo retarda el proceso de recombinación (tail current), también incrementa la ganancia del transistor PNP. Así que el tiempo de apagado se incrementa.

El estado on/off del dispositivo es controlado, como en un MOSFET por la tensión del gate. Si la tensión aplicada al gate, con respecto al emisor es menor a la tensión de umbral (threshold) entonces no es creada la capa de inversión del MOS y el dispositivo se encuentra apagado. Cualquier tensión aplicada en directa caerá a través de la juntura J2 polarizándola en inversa. La única corriente que fluirá será una pequeña corriente de fuga. La tensión de breakdown es por lo tanto determinada por la tensión breakdown de esta juntura.

### 3-3. Latch-up

El IGBT contiene un tiristor PNPN parásito en su estructura entre el colector y el emisor. Se puede enganchar como un tiristor si se da la siguiente condición:

$$(\alpha_{npn} + \alpha_{pnp}) \geq 1$$

En el circuito equivalente mostrado anteriormente incluye un transistor parásito NPN formado por la región del source tipo N+, la región tipo P y la región drift tipo N-, también muestra la resistencia lateral de la región tipo P llamada  $R_s$ .

Si la corriente que fluye a través de esta resistencia es lo suficientemente alta producirá una caída de tensión que polarizará en directa la juntura de la región N+, encendiéndolo al transistor parásito NPN el cual forma parte del tiristor parásito. Una vez que esto suceda hay una fuerte inyección de electrones de la región N+ dentro de la región P y el control del gate es perdido.

Esto significa que la corriente del IGBT no es más controlada por el gate del MOS, destruyéndose debido a la excesiva disipación de potencia producida.

La capa intermedia N+ y la amplia base epitaxial reducen la ganancia del transistor NPN mediante el diseño interno, evitando, por lo tanto el enganche.

La corriente de latching es fuertemente influenciada por el tiempo de apagado de la tensión del gate, porque aumenta la ganancia del NPN, por lo tanto un lento apagado previene esta condición manteniendo una pequeña corriente a través de este transistor.

### 4. SOA (Safe-Operating-Area)

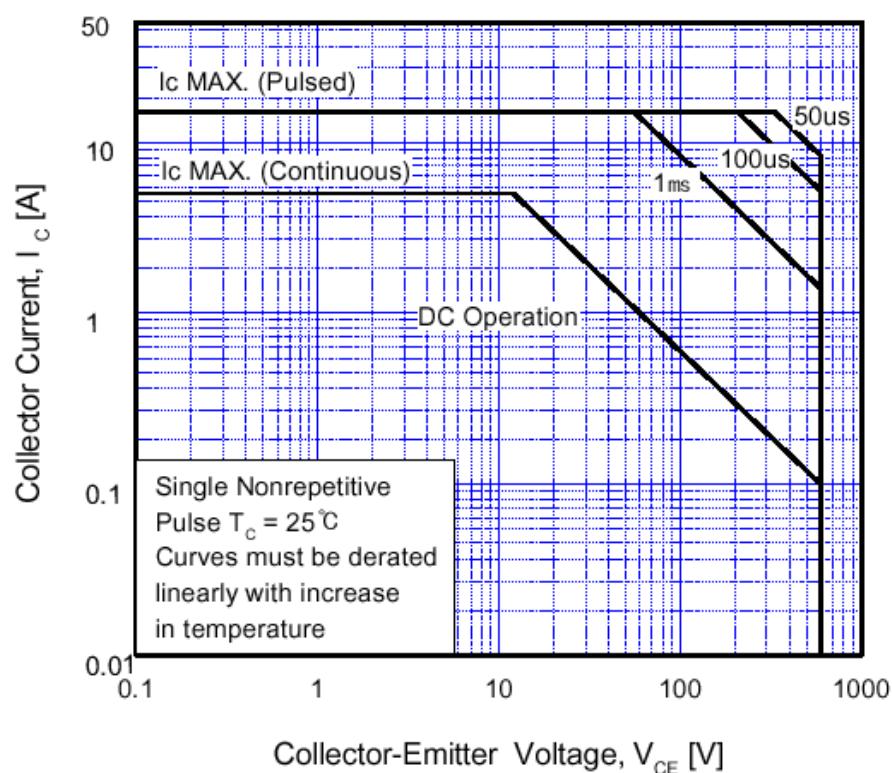

El SOA de un IGBT puede ser dividida en las siguientes tres partes basadas en condiciones de tensión y corriente.

- A- Alta tensión, baja corriente: La máxima tensión es limitada por la tensión de breakdown.

- B- Alta corriente y baja tensión: La máxima corriente es limitada por el latch-up del tiristor parásito.

- C- Simultáneamente alta tensión y corriente: Limitada por la elevación de temperatura provocada por altas disipaciones de potencia.

Sí una alta corriente y tensión son introducidas simultáneamente por un corto tiempo, entonces el SOA no es mas limitado por la disipación de potencia.

#### 4-1. FBSOA (Forward Biased Safe-Operating-Area)

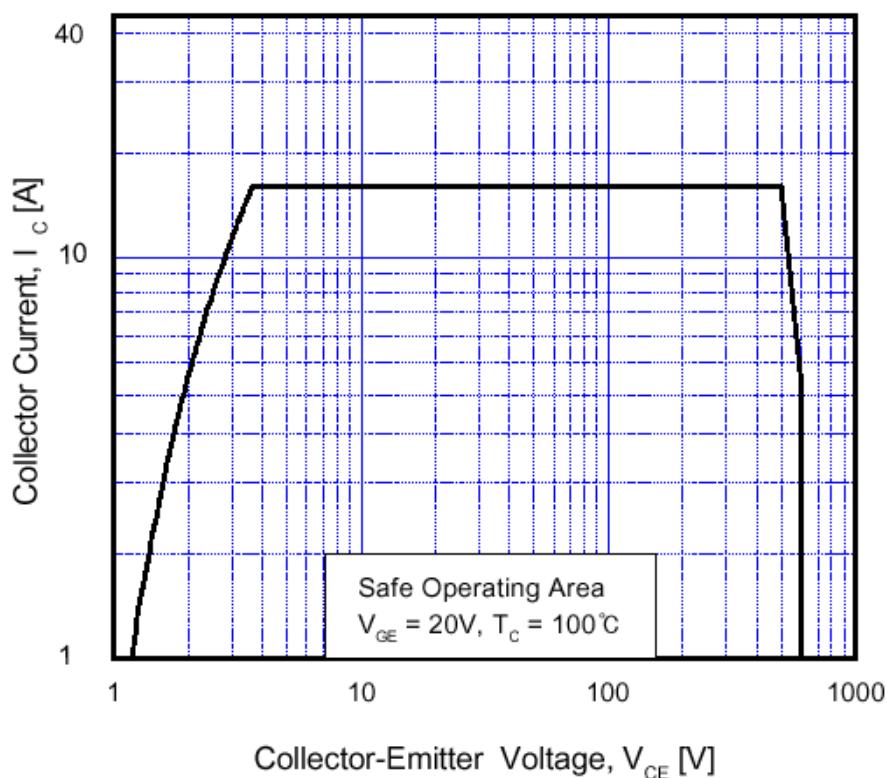

Muestra el área de operación segura durante el periodo de encendido.

Indica la máxima tensión que el dispositivo puede soportar sin fallar cuando la corriente de colector está saturado.

Como muestra la figura, el límite es casi cuadrado para tiempos cortos de conmutación, similar al transistor MOSFET. El IGBT es limitado térmicamente para periodos largos de conmutación.

#### 4-2. RBSOA (Reverse Biased Safe-Operating-Area, Turn-Off SOA)

Muestra el área de operación segura durante el periodo de apagado. La tensión varía desde una pequeña tensión hasta la tensión de fuente con corriente constante y sin corriente de gate. El corte superior derecho, indica que el RBSOA es reducido cuando la  $dV_{ce}/dt$  es incrementada para evitar el latch-up dentro del dispositivo. La línea horizontal superior representa el valor máximo de ICM (corriente pulsante de colector).

#### 4-3. SCSOA (Short Circuit Safe-Operating-Area)

Operación en cortocircuito: la corriente en el IGBT está limitada por la tensión de gate y la transconductancia pudiendo alcanzar valores en exceso de 10 veces en su valor continuo. Esta técnica incrementa las pérdidas de conducción y reduce las velocidad de conmutación. Alta tensión y corriente simultáneamente provoca un excesivo esfuerzo al dispositivo.

#### 5. Características de conducción

Un IGBT consiste de un PNP controlado por un MOSFET de canal N en una configuración seudo darlington, el JFET es incluido en el circuito equivalente para representar la resistencia de modulación. La densidad de celda de la estructura del MOSFET es mayor cuanto mayor es la tensión, comparable con la tecnología de los transistores MOSFET y en consecuencia posee un mejor producto de resistencia – área.

La región base del PNP no está presente y la juntura PN base – emisor, que abarca toda la extensión de la oblea no puede ser terminada ni pasivada. Esto influye en el apagado y en el comportamiento del bloqueo inverso del IGBT. La tensión de ruptura es cercana a los 20 V.

Como se ve en el circuito equivalente, la caída de tensión de un IGBT es la suma de dos componentes: la caída de tensión de diodo formado por la juntura PN y la caída de tensión del MOSFET. De esta manera, a diferencia de un transistor MOSFET de potencia, la caída de tensión del IGBT en estado de conducción nunca será menor que la caída de tensión umbral de un diodo.

### 5-1. Características de transferencia estáticas

El MOSFET de entrada posee una característica típica de todos los transistores MOSFET de baja tensión: es sensible a la tensión de excitación del gate.

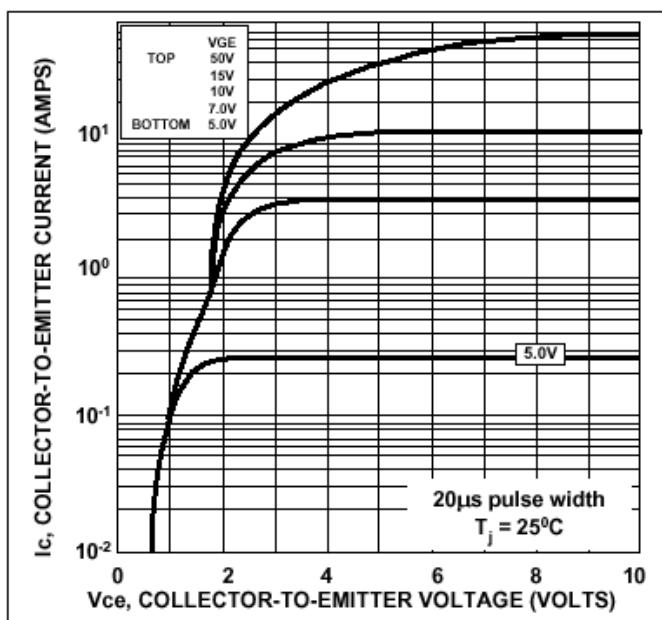

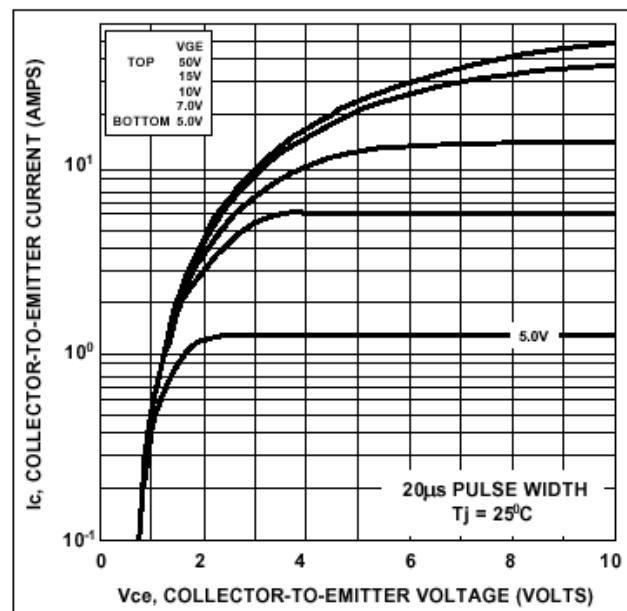

Esto se ve en las dos figuras siguientes que representan las características estáticas, donde para corrientes que son cercanas a su valor de operación impuesta por la carga del circuito, un incremento en la tensión de gate provoca una disminución en la tensión de colector – emisor.

Esto es debido al hecho de que, entre su rango de operación, la ganancia del PNP aumenta con la corriente y un aumento en la tensión del gate provoca un aumento en la corriente del canal, y por consiguiente una disminución en la caída de tensión del PNP. Esto se difiere mucho del comportamiento de un transistor MOSFET de potencia de alta tensión, el cual es ampliamente insensible a la tensión de gate.

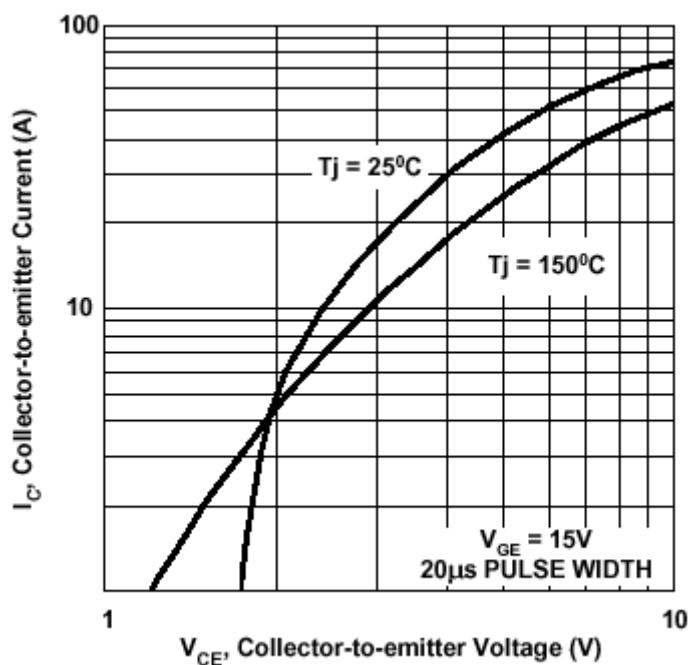

Typical Output Characteristics.  $T_c = 25^\circ\text{C}$

Typical Output Characteristics,  $T_c = 150^\circ\text{C}$

### 5-2. Switchback

La caída de tensión en un dispositivo de conductividad modulada con extinción del tiempo de vida de los portadores minoritarios puede mostrar un comportamiento peculiar conocido como "switchback" (pendiente en zigzag): la caída de tensión a niveles bajos de corriente y temperatura es mas alta de lo esperado, cayendo repentinamente a su valor esperado si la corriente o la temperatura aumentan.

Este comportamiento se le atribuye al tiempo de vida de extinción el cual, facilita la recombinación, retrasando el comienzo de la conductividad modulada.

Un dibujo de este fenómeno puede ser visto en la depresión de la zona de V<sub>ce(sat)</sub> de la figura anterior a una T<sub>C</sub> = 25 °C, al aumentar la temperatura la depresión desaparece porque incrementa el tiempo de vida de las cargas y acelera el comienzo de la modulación de conducción.

Solo los IGBT ultrarrápidos presentan este fenómeno, por los altos valores de tiempos de extinción.

### **5-3. Dependencia con la temperatura**

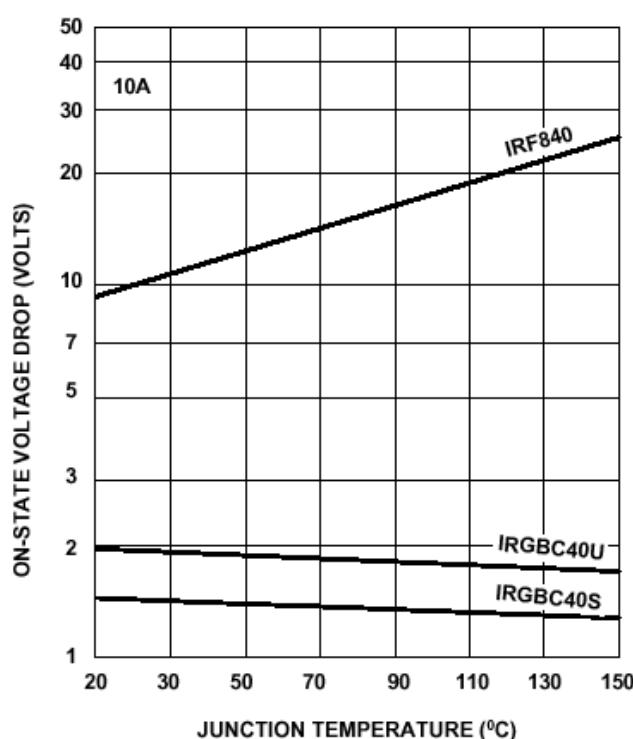

La conductividad modulada causa un notable mejoramiento sobre la caída de tensión colector - emisor, donde puede verse en la siguiente figura, la cual compara al transistor MOSFET IRF840 con un IGBT de las mismas dimensiones.

La dependencia con la temperatura es muy significativa en el MOSFET, pero mínima en el IGBT.

En la siguiente figura se ve que la dependencia de la temperatura en las caídas de tensión son distintas para diferentes niveles de corriente para un mismo IGBT. Esto es porque el elemento diodo de esta pastilla posee un coeficiente de temperatura que es inicialmente negativo volviéndose positivo para altos niveles de corriente. Por otro lado el componente MOSFET de la pastilla tiene coeficiente positivo.

Para reducir la caída de tensión y su coeficiente de temperatura, la modulación de conducción virtualmente elimina su dependencia sobre el rango de tensión. Esto es mostrado en la siguiente tabla, donde muestra la caída de conducción de cuatro diferentes IGBTs comparados con MOSFETs de características similares.

| Rated Voltage                                          | IGBT    | 100 | 300  | 600  | 1200 |

|--------------------------------------------------------|---------|-----|------|------|------|

| Typical Voltage Drop<br>@ 1.7A/mm <sup>2</sup> , 100°C | IGBT    | 1.5 | 2.1  | 2.4  | 3.1  |

|                                                        | HEXFET® | 100 | 250  | 500  | 1000 |

|                                                        | IGBT    | 2.0 | 11.2 | 26.7 | 100  |

Table 1: Dependence of Voltage Drop From Voltage Rating

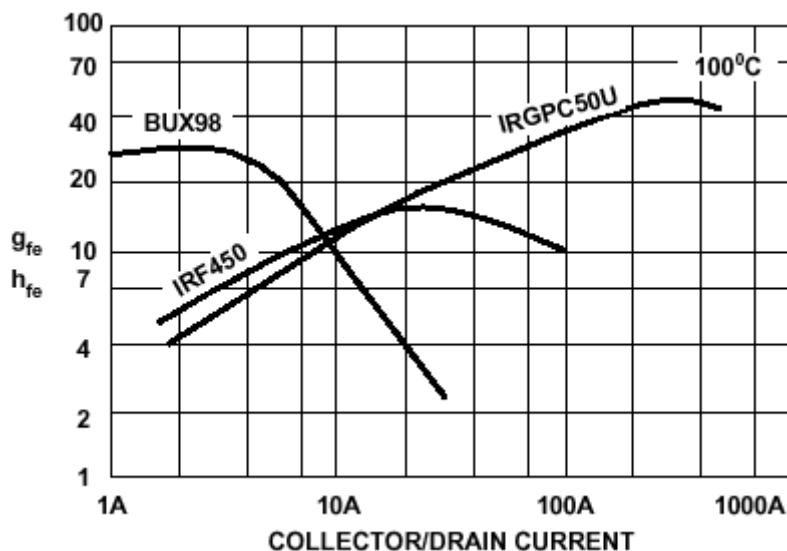

## 6. Transconductancia

La capacidad de manejo de corriente de un semiconductor puede ser limitada por sus constantes termales, o por sus constantes de ganancia / transconductancia.

La figura siguiente muestra la dependencia de la transconductancia de un IGBT IRGPC50U comparado con un MOSFET IRF450 y la ganancia de un transistor BIPOLAR BU98 de aproximadamente las mismas dimensiones.

Se ve en el IGBT como aumenta la transconductancia con el aumento de la corriente, en la zona de la curva donde se achata, el canal del MOSFET entra en saturación que reduce la corriente de base del PNP.

La saturación de la transconductancia ocurre a niveles inferiores de corriente cuando se incrementa la temperatura. La disminución de la transconductancia a valores de corriente muy altos y su adicional disminución con la temperatura ayuda a proteger al IGBT bajo condiciones de corto circuito.

Con una tensión de gate de 15 V, la densidad de corriente de un IGBT estándar de International Rectifier alcanza valores de 10 a 20 A/mm<sup>2</sup> en corto circuito. Esta alta transconductancia es particularmente responsable por sus mejores características de conducción y conmutación.

## 7. Interpretación de la hoja de datos

A fin de comprender mejor el uso y las condiciones de los diferentes términos suministrados en las hojas de datos nos apoyaremos en el transistor de potencia IGBT "IRG4PH50UD" de International Rectifier.

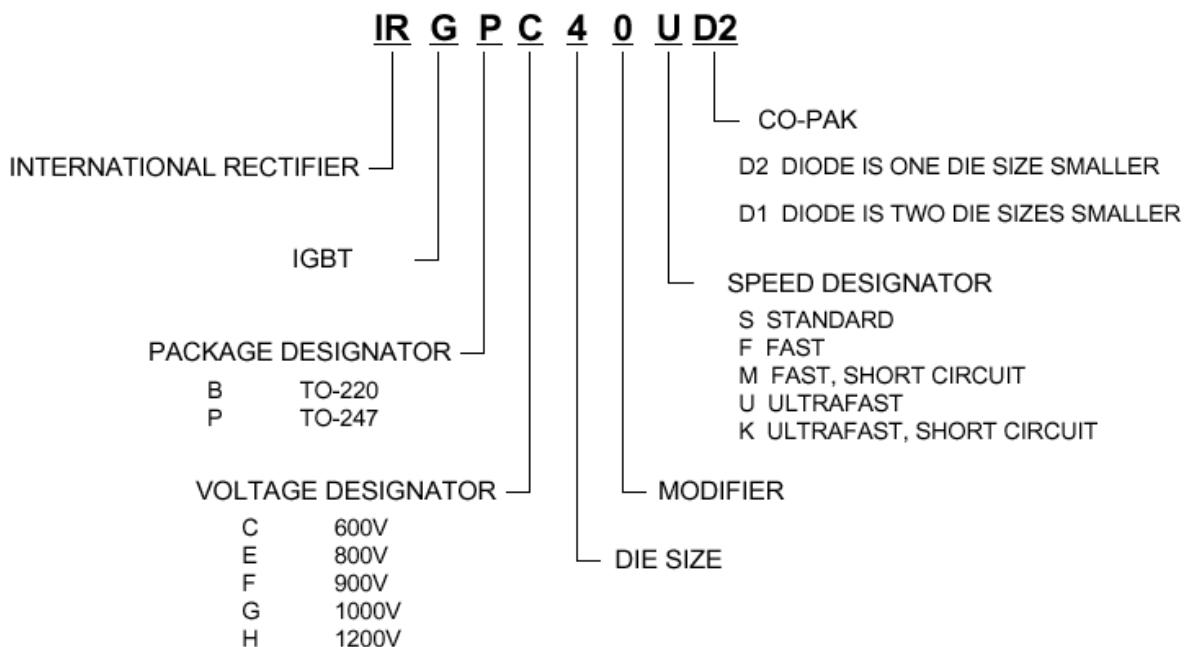

### 7-1. Nomenclatura

Código simplificado para la nomenclatura de los IGBT comerciales.

**Ejercicio)** Determinar la nomenclatura del IGBT “IRG4PH50UD”.

- IR**: International Rectifier.

- G**: Transistor IGBT.

- 4**: Encapsulamiento de cuarta generación.

- P**: Encapsulado industrial estándar TO-247AC

- H**: Vces = 1200V

- 50**: Dimensión de la pastilla y su modificador.

- UD**: Diodo ultra rápido

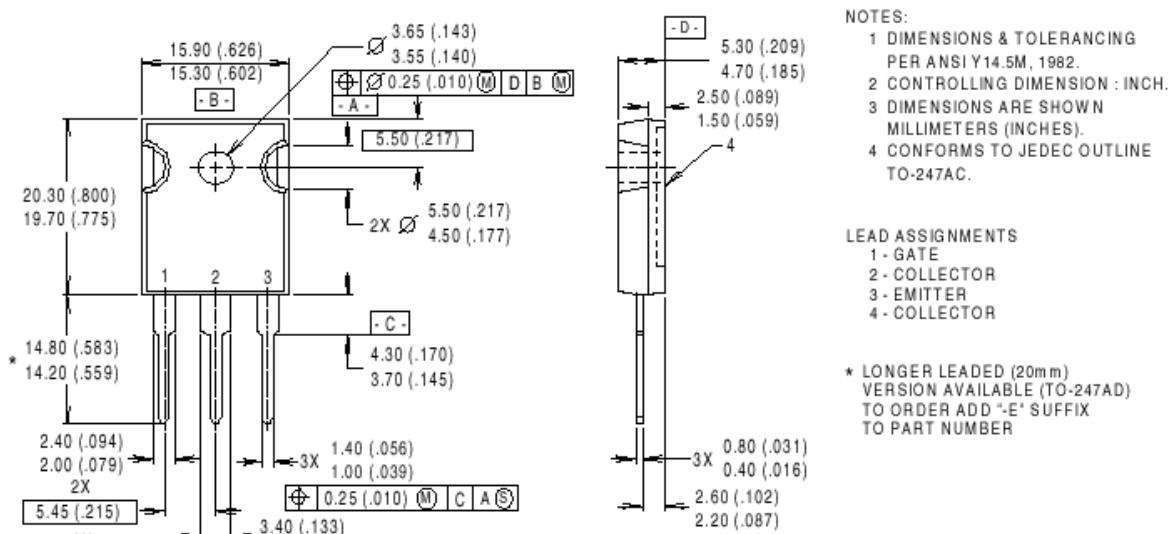

## 7-2. Case Outline – TO-247AC

**CONFORMS TO JEDEC OUTLINE TO-247AC (TO-3P)**

Dimensions in Millimeters and (Inches)

## 7-3. Absolute Maximum Ratings

Las características máximas absolutas de operación del dispositivo son aplicadas bajo ciertas condiciones. Superando estos valores o variando las condiciones operativas de trabajo que garantizan estos ratings, pueden impedir la confiabilidad o funcionalidad y también provocar la destrucción del dispositivo.

### 7-3-1. Tensión de colector – emisor (Vces)

Es la máxima tensión permisible entre el colector y el emisor cuando el gate y el emisor están cortocircuitados. Si este límite es excedido, el dispositivo puede ser destruido debido a la ruptura (breakdown) de la juntura entre el colector y el emisor. El breakdown es garantizado en la tabla de características eléctricas de la hoja de datos.

|                  |                                        |      |   |

|------------------|----------------------------------------|------|---|

| V <sub>CES</sub> | Collector-to-Emitter Breakdown Voltage | 1200 | V |

|------------------|----------------------------------------|------|---|

### 7-3-2. Corriente continua de colector (Ic)

$$I_c @ T_c = 25^\circ C$$

$$I_c @ T_c = 100^\circ C$$

Es la máxima corriente en continua que puede fluir a la temperatura de carcaza especificada, el cálculo de Ic puede ser obtenido de la siguiente formula:

$$I_c = \frac{\Delta T}{\theta_{j-c} \cdot V_{CE(on)} @ I_c}$$

$$\Delta T = T_j(\max) - T_c$$

Vce @ Ic no es conocida porque la Ic no es conocida, se debe hallar mediante varias iteraciones.

Es claro de esta formula que el rating de corriente no tiene significado si no se conocen las temperaturas de juntura y carcaza. En aplicaciones normales la temperatura de carcaza es mucho mayor que 25 °C, este rating no es un valor práctico y solo es informado porque los transistores han sido tradicionalmente especificado de esta forma.

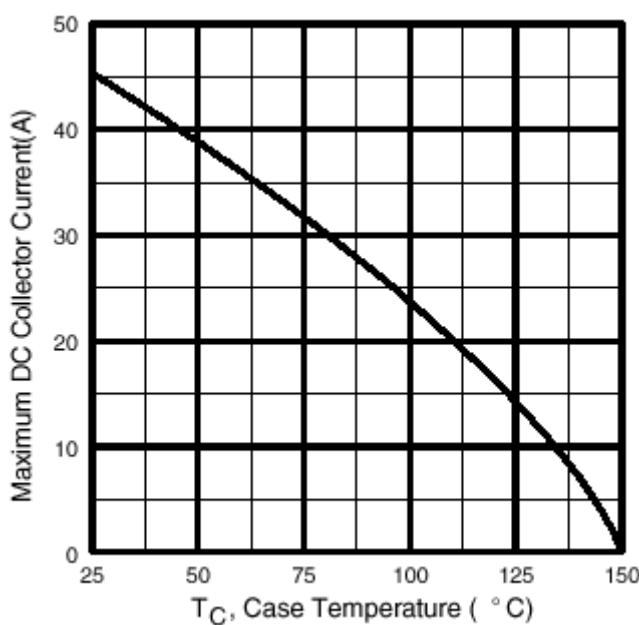

La figura 4 de la hoja de datos del dispositivo especificado nos muestra los cambios de este rating con la temperatura de carcaza, con una temperatura de juntura de 150 °C.

|                 |                              |    |   |

|-----------------|------------------------------|----|---|

| Ic @ Tc = 25°C  | Continuous Collector Current | 45 |   |

| Ic @ Tc = 100°C | Continuous Collector Current | 24 | A |

**Ejercicio)** Hallar el valor máximo de la corriente de colector en continua para una temperatura de carcaza de 75 °C y encontrar su tensión colector – emisor de saturación.

Del gráfico anterior interceptando la línea vertical correspondiente a  $T_C = 75 \text{ }^{\circ}\text{C}$  con la curva hallamos que la  $I_C = 32 \text{ A}$ , de la ecuación encontramos la  $V_{ce(on)}$ :

$$V_{ce(on)} = \frac{T_{jmax} - T_c}{R\theta_{jc} \times I_c} = \frac{150 \text{ }^{\circ}\text{C} - 75 \text{ }^{\circ}\text{C}}{0.64 \text{ }^{\circ}\text{C/W} \times 32 \text{ A}} = 3,66 \text{ V}$$

### 7-3-3. Corriente pulsante de colector ( $I_{cm}$ )

Es la corriente pico que el dispositivo puede fluir por encima de la corriente de continua  $I_c$ , dentro de los límites térmicos. Varía con el ancho del pulso de la corriente, el ciclo de actividad y las condiciones de disipación de calor.

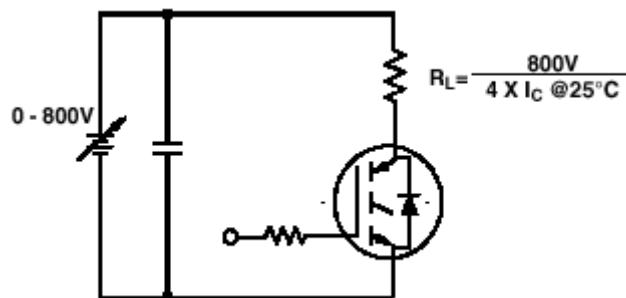

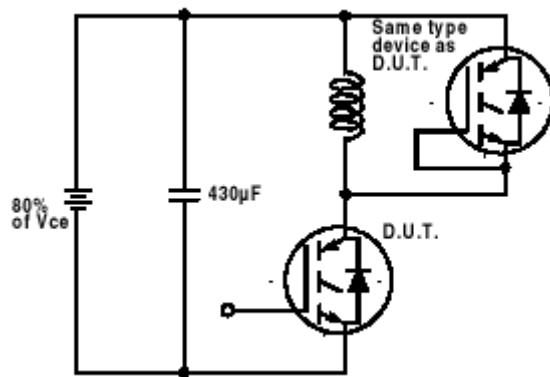

El circuito de prueba es mostrado en la siguiente figura, la cual aparece en la figura 20 de las hojas de datos:

|          |                            |     |

|----------|----------------------------|-----|

| $I_{cm}$ | Pulsed Collector Current ① | 180 |

|----------|----------------------------|-----|

① Repetitive rating:  $V_{GE}=20\text{V}$ ; pulse width limited by maximum junction temperature

**Ejercicio)** Obtener las formas de onda del pulso del gate que permiten esta condición.

EMBED

Equation.3

EMBED Equation.3

EMBED Equation.3

$$180A = 45A \times \frac{150^{\circ}\text{C} - 25^{\circ}\text{C}}{200W \times 0.64^{\circ}\text{C} / W \times Z\theta_{jc}}$$

Despejando obtenemos la respuesta termal:

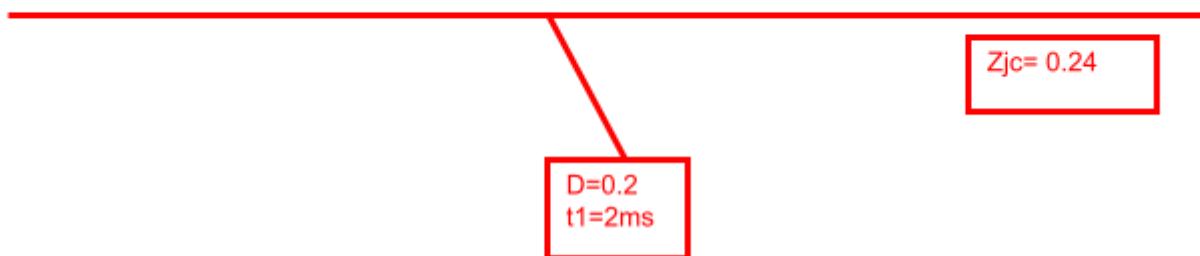

$$Z\theta_{jc} = 0,24$$

De la figura 6 de la hoja de datos obtenemos los diferentes ciclos de actividad y anchos de pulso que cumplan con la condición de  $I_{cm}$ .

EMBED Word.Picture.8

#### 7-3-4. Corriente de carga inductiva con clamping (ILM)

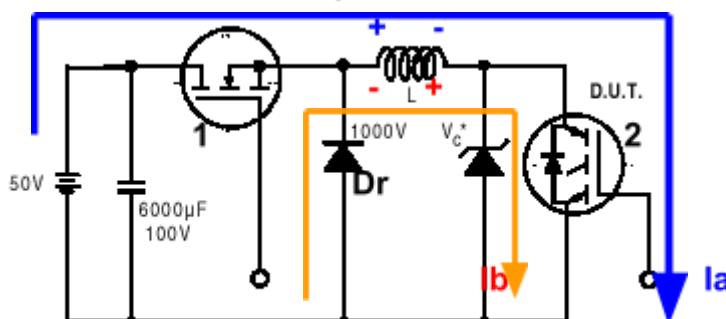

Este rating garantiza que el dispositivo es capaz de apagarse (turn-off) repetitivamente a la corriente especificada con carga inductiva con diodo clamping, como es encontrado en la mayoría de las aplicaciones.

A continuación se muestra el circuito de prueba encontrado en la figura 19 de la hoja de datos, el mismo es especificado a una temperatura de juntura de 150 °C y al 80% de la tensión de trabajo.

|                 |                                  |     |

|-----------------|----------------------------------|-----|

| I <sub>LM</sub> | Clamped Inductive Load Current ② | 180 |

|-----------------|----------------------------------|-----|

②  $V_{CC}=80\%(V_{CES})$ ,  $V_{GE}=20V$ ,  $L=10\mu H$ ,  $R_G=5.0\Omega$  (figure 19)

Cuando ambos transistores están activados, la corriente fluye a través de ambos pasando por la carga inductiva, el sentido de la corriente y la polaridad sobre la carga es indicada sobre la figura anterior como  $I_a$ . En el momento que se corta el transistor 1 el sentido de la corriente se mantiene indicado en la figura como  $I_b$ , la polaridad sobre la carga se invierte activando el diodo  $D_r$ . La corriente se descargará a través de este y el transistor 2. El diodo zener está para limitar el valor de tensión provocado por la energía almacenada en el inductor al momento de desconectarse el transistor 1.

El circuito de prueba expone al IGBT a la corriente pico de recuperación inversa del diodo rueda libre (free-wheeling), que adiciona una componente significativa a las perdidas durante el encendido (turn-on).

Este valor garantiza que el IGBT trabaje en el SOA en conmutación, es decir el dispositivo puede sostener simultáneamente altos valores de corriente y tensión, como se ve en la siguiente figura.

Turn-on with a clamped inductive load and a fast recovery diode.

Turn-on with an ideal diode (zener clamp).

### 7-3-5. Corriente continua y máxima del diodo en directa (IF y IFM)

IF @  $T_c = 100^\circ C$ , es la máxima corriente DC que el diodo puede fluir en directa a la temperatura de carcasa especificada.

IFM, es la máxima corriente que el diodo puede fluir por encima de IF teniendo en cuenta el límite termal de la temperatura máxima de juntura.

|                           |                                  |     |

|---------------------------|----------------------------------|-----|

| $I_F @ T_C = 100^\circ C$ | Diode Continuous Forward Current | 16  |

| $I_{FM}$                  | Diode Maximum Forward Current    | 180 |

### 7-3-6. Tensión gate - emisor (Vge)

La tensión Vge está limitada por el espesor del nivel de oxidación del gate. La ruptura dieléctrica a través del gate es típicamente alrededor de 80 volt, pero para el usuario este valor está limitado a 20 V, para limitar la corriente bajo condiciones de falta y asegurar una buena confiabilidad térmica.

|          |                         |          |   |

|----------|-------------------------|----------|---|

| $V_{GE}$ | Gate-to-Emitter Voltage | $\pm 20$ | V |

|----------|-------------------------|----------|---|

### 7-3-7. Potencia disipada (PD)

$PD @ T_c = 25^\circ C$

$PD @ T_c = 100^\circ C$

Es el valor máximo de disipación de potencia a esa temperatura de carcaza especificada, y se calcula con la siguiente ecuación:

EMBED

Equation.3

|                          |                           |     |   |

|--------------------------|---------------------------|-----|---|

| $PD @ T_c = 25^\circ C$  | Maximum Power Dissipation | 200 | W |

| $PD @ T_c = 100^\circ C$ | Maximum Power Dissipation | 78  |   |

**Ejercicio)** Hallar la potencia disipada para una temperatura de carcaza de  $75^\circ C$ .

$$PD = \frac{150^\circ C - 75^\circ C}{0.64^\circ C/W} = 117,2W$$

### 7-3-8. Temperatura de juntura (Tj) y temperatura de almacenamiento (Tstg)

El rango de operación de la temperatura de juntura está entre los  $-55^\circ C$  y los  $150^\circ C$ , siendo la temperatura máxima de juntura del dispositivo de  $150^\circ C$ .

El rango de temperatura de almacenamiento o transporte del dispositivo está entre los  $-55^\circ C$  y los  $150^\circ C$ .

|           |                                                  |              |            |

|-----------|--------------------------------------------------|--------------|------------|

| $T_j$     | Operating Junction and Storage Temperature Range | -55 to + 150 | $^\circ C$ |

| $T_{STG}$ |                                                  |              |            |

### 7-3-9. Tiempo de sostenimiento de corto circuito (Tsc)

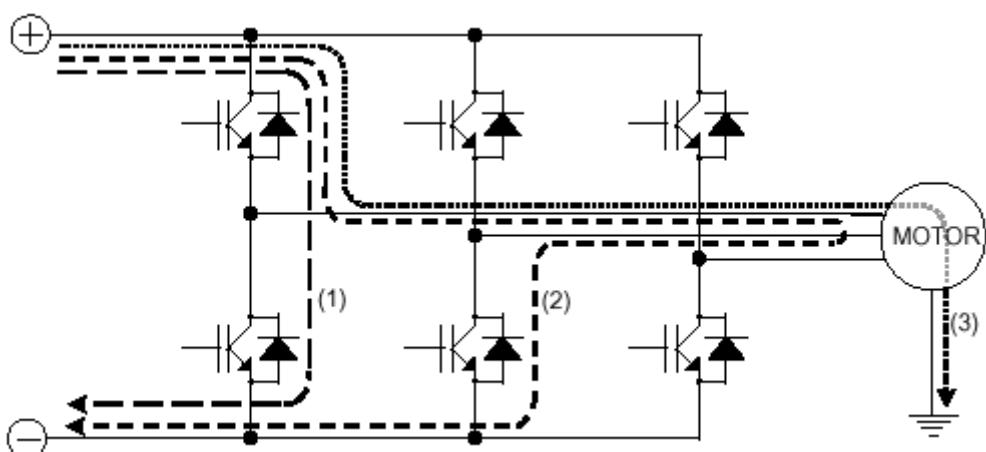

La figura siguiente muestra los modos de cortocircuito que pueden ocurrir en un puente trifásico controlando un motor de alterna.

El camino 1 indica que el cortocircuito se produjo por un error de las señales aplicadas al gate de los transistores, activando al mismo tiempo el par de IGBT's complementarios.

El camino 2 se produce por un corto en el terminal colector debido a una mala secuencia de disparo.

El camino 3 se produce cortocircuitándose a masa debido a un mal funcionamiento del motor.

La corriente durante el periodo de cortocircuito crece varias veces con respecto a la corriente nominal, debido a que los gate siguen recibiendo señal de sus respectivos drivers, si la protección no es funcional en ese tiempo, llevará a la destrucción completa del dispositivo. Normalmente a un sistema detector de sobrecorriente le lleva entre 3 y 7  $\mu$ s volverse activo. El IGBT IRG4PH50K de similares características al estudiado fue diseñado para sostener ese tiempo con un pequeño margen de seguridad.

|          |                              |    |         |

|----------|------------------------------|----|---------|

| $t_{sc}$ | Short Circuit Withstand Time | 10 | $\mu$ s |

|----------|------------------------------|----|---------|

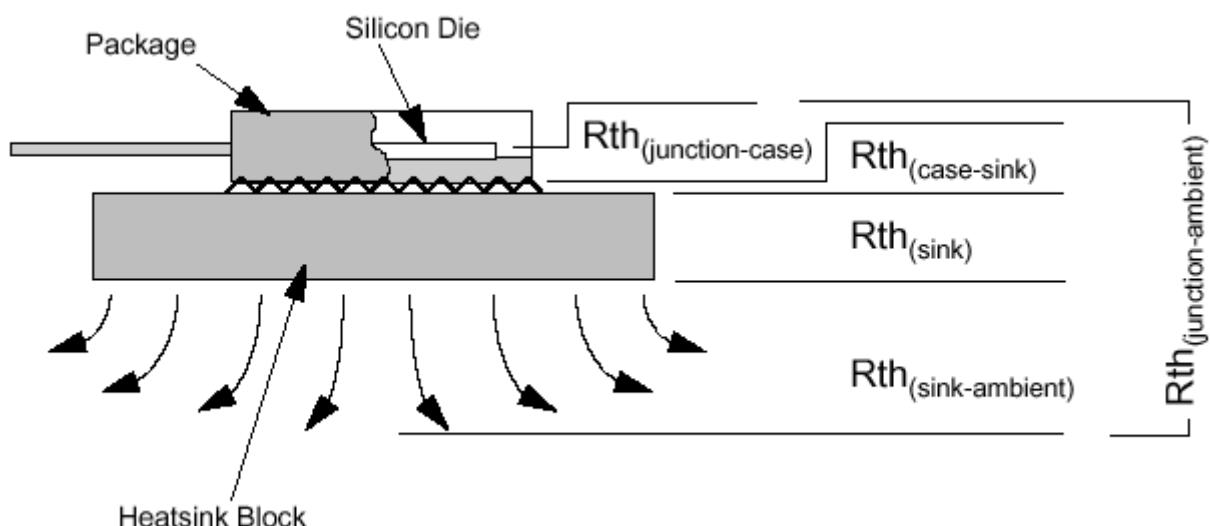

#### 7-4. Thermal Resistance

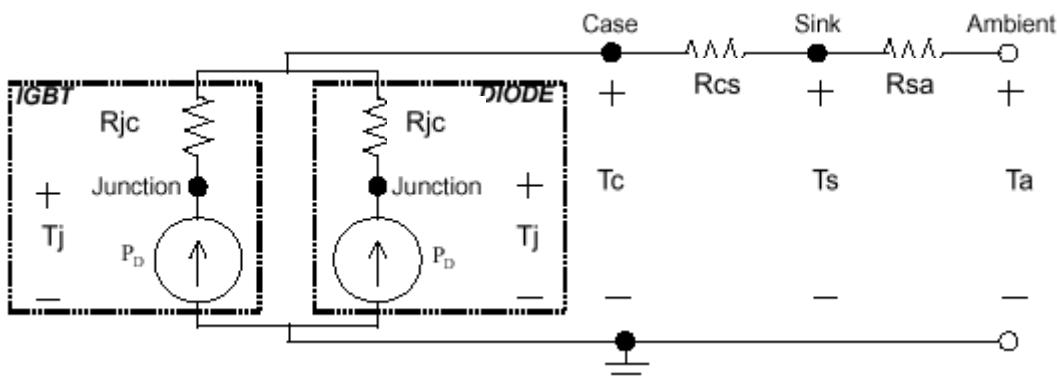

Las perdidas de potencia del dispositivo se tornan en calor e incrementan la temperatura de juntura dentro del chip. Esto degrada las características del dispositivo y acorta su vida, es importante que el calor producido desde la juntura del chip escape al exterior para disminuir la temperatura de juntura. La impedancia termal mide la capacidad del dispositivo de disipar calor en un sistema donde están involucradas varias partes como muestra la figura siguiente.

Un circuito equivalente basado en las resistencias térmicas (co-pack) de un IGBT es mostrado en la figura siguiente.

#### 7-4-1. Resistencia térmica de juntura al ambiente ( $R_{\theta JA}$ )

La resistencia térmica completa de la juntura del chip al ambiente es denotada como  $R_{\theta JA}$  (Resistencia térmica juntura – ambiente) y la siguiente formula sale del circuito equivalente:

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CS} + R_{\theta SA} \quad [\text{°C/W}]$$

#### 7-4-2. Resistencia térmica de juntura a carcaza ( $R_{\theta jc}$ )

Es la resistencia térmica de la juntura del chip al encapsulado metálico exterior. El mismo es determinado por el diseño y los materiales utilizados en la construcción del dispositivo. El diseñador no tiene influencia directa sobre esta componente del sistema.

Este valor es medido con una  $T_c = T_a = 25 \text{ °C}$ , esta es una condición donde utiliza un disipador de calor infinito y se determina con la siguiente formula:

$$R_{\theta JC} = \frac{T_j - T_c}{P_D} \quad [\text{°C/W}]$$

Los productos co-pack vienen especificado con la  $R_{\theta jc}$  del IGBT y del diodo interno.

#### 7-4-3. Resistencia térmica de carcaza a disipador ( $R_{\theta cs}$ )

Es la resistencia térmica de la carcaza del encapsulado al disipador, varía con el encapsulado, el tipo de hoja aislante, grasa siliconada y el método de montaje.

A continuación se detalla los valores de la hoja de datos de las diferentes resistencias térmicas.

|                 | Parameter                                 | Min. | Typ. | Max. | Units |

|-----------------|-------------------------------------------|------|------|------|-------|

| $R_{\theta JC}$ | Junction-to-Case - IGBT                   | —    | —    | 0.64 | °C/W  |

| $R_{\theta JC}$ | Junction-to-Case - Diode                  | —    | —    | 0.83 |       |

| $R_{\theta CS}$ | Case-to-Sink, flat, greased surface       | —    | 0.24 | —    |       |

| $R_{\theta JA}$ | Junction-to-Ambient, typical socket mount | —    | —    | 40   |       |

El diseñador del sistema puede tener una gran influencia sobre  $R_{\theta cs}$ .

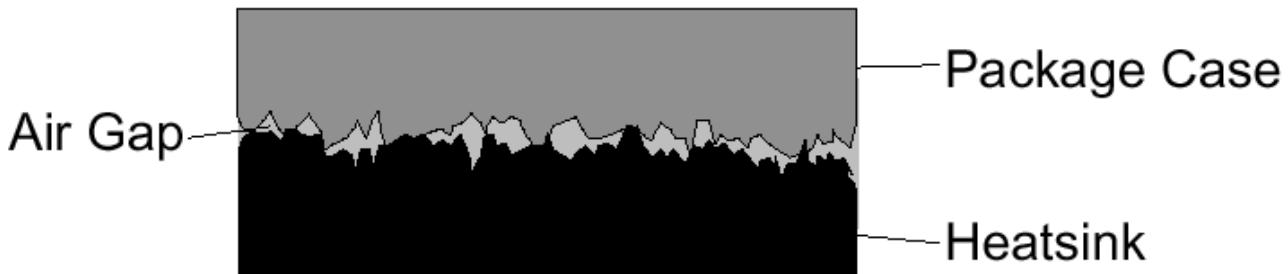

Las superficies de la carcasa y el disipador nunca van a estar perfectamente enfrentadas, permitiendo fluir el aire entre ambas rugosidades, como se ilustra en la siguiente figura.

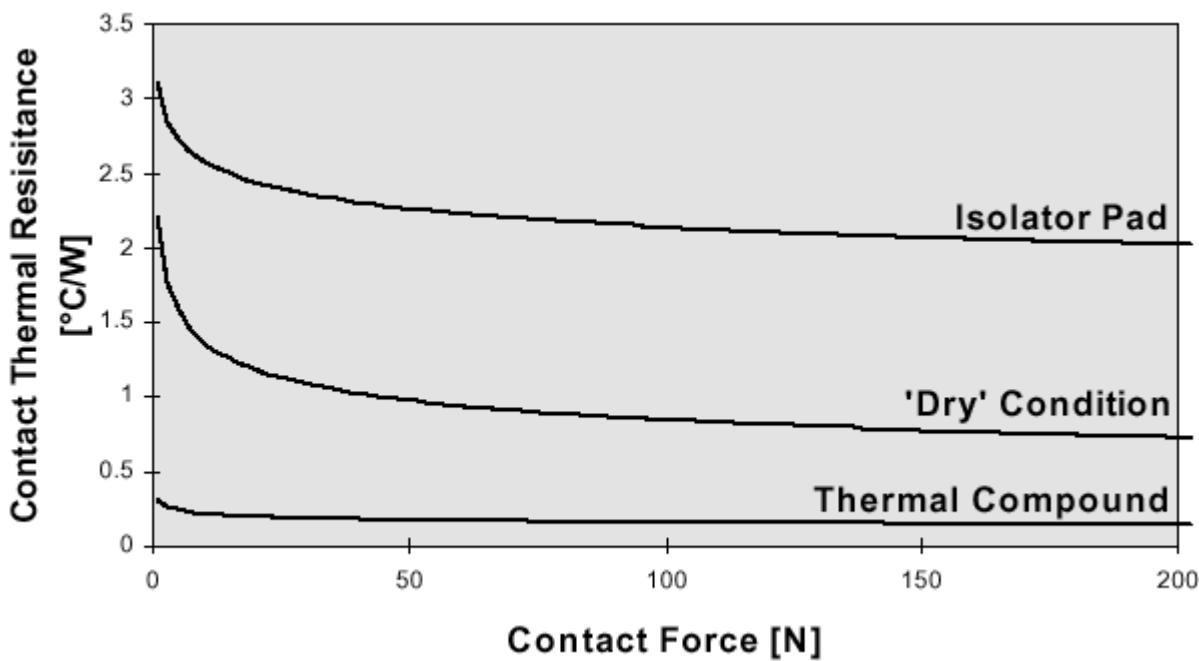

Ya que el aire es un buen aislante térmico, la resistencia térmica de contacto es mucho mayor que si estuvieran perfectamente enfrentadas. Cuando la fuerza de contacto es incrementada, esta resistencia disminuye.

El método más común para superar esto es utilizar un compuesto térmicamente conductivo del calor que llene las imperfecciones de ambas superficies bajando la resistencia térmica de contacto. Un ejemplo de este compuesto puede ser la grasa siliconada que posee algo de aislante eléctrico y un buen material conductor del calor como la alumina.

Como la carcasa del IGBT no viene aislada eléctricamente de su pinouts, en nuestro caso corresponde al colector, hay ocasiones en donde más de un dispositivo, comparte el mismo disipador, entonces, es necesario insertar un material aislante eléctrico entre la carcasa y el disipador.

Este tiene un efecto directo y perjudicial sobre la resistencia térmica de contacto adicionando una resistencia extra. Otra vez la resistencia térmica de contacto depende de la presión de contacto.

El siguiente gráfico compara los tres casos mencionados: sin compuesto (dry condition), con un compuesto (thermal compound) y con una hoja aislante (isolator pad) a diferentes niveles de presión de contacto.

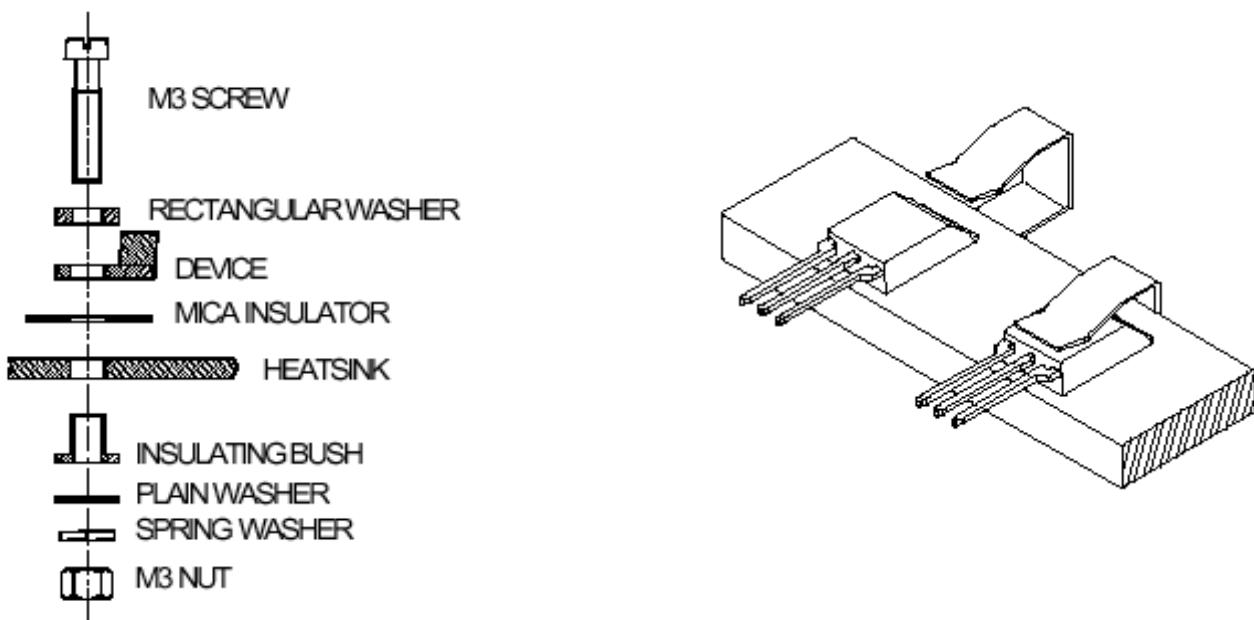

Es importante que los semiconductores de potencia estén correctamente instalados para garantizar su correcta funcionalidad, ya que se pueden producir problemas mecánicos y térmicos. A continuación se muestra unos montajes sugeridos:

#### 7-4-4. Resistencia térmica de disipador al ambiente ( $R_{\theta sa}$ )

Es la resistencia térmica desde el disipador al ambiente y es determinada por la geometría de su estructura, por la superficie de su área, método de enfriamiento y la calidad del disipador. Este dato no aparece en las hojas de datos es dado por el fabricante del disipador, el mismo debe ser calculado.

El diseñador del sistema elegirá el óptimo disipador comparando requerimientos de costo y rendimiento.

**Ejercicio)** La circulación de corriente continua por el dispositivo montado en un disipador es de 12 A y la temperatura ambiente a la que está expuesto el circuito es de 40 °C.

- A- Calcular la Tj.

- B- Calcular la Tc.

- C- Hallar el disipador correspondiente.

La capacidad de remover calor cuando conduce una cantidad fija de corriente, está dada por la ecuación fundamental en la cual no intervienen las perdidas por commutación.

**EMBED

Equation.3**

La  $R_{\theta jc}$  es el valor máximo especificado en la hoja de datos debido a que circula corriente continua.

Excepto para disipadores refrigerados por agua, es muy difícil mantener la temperatura de carcaza por debajo de 90 °C. En la mayoría de los casos prácticos la Tc ronda entre los 90 y los 110 °C. Esto permite un diferencial suficiente entre las temperaturas ambiente y de carcaza para que el disipador pueda manejar la transferencia de calor.

La potencia disipada en conducción también es calculada con la caída de tensión en conducción y la corriente continua de conducción.

**EMBED

Equation.3**

De acuerdo a la figura 2 de la hoja de datos mostrada más abajo (Ic en función de Vce) vemos que la variación de Vce con la temperatura de juntura para una Ic dada es muy poca, por lo tanto para un diseño conservador adoptaremos el valor de  $V_{ce} = 2,8$  V que se interpola con la curva correspondiente a  $T_j = 25$  °C ya que es el peor caso para una  $I_c = 12A$ .

Con este valor obtenido hallamos la potencia disipada y luego la variación de temperatura entre juntura y carcaza.

$$\Delta T = PD \times R_{\theta jc} = 33,6W \times 0,64^{\circ}\text{C}/\text{W} = 21,5^{\circ}\text{C}$$

De acuerdo a la figura 4 de la hoja de datos ( $I_c$  en función de  $T_c$ ) mostrada en el punto 7-3-2, la  $T_c$  máxima para 12 A sería aproximadamente 130 °C.

También habíamos dicho que la  $T_c$  no podía ser menor a 90 °C, entonces, siguiendo con un criterio conservador, adoptamos una  $T_c = 110$  °C, por lo tanto la  $T_j$  será:

$$T_j = T_c + \Delta T = 110^\circ\text{C} + 21,5^\circ\text{C} = 131,5^\circ\text{C}$$

El calculo del disipador ( $R\theta_{sa}$ ), surge de hacer una analogía eléctrica del circuito equivalente termal mencionado anteriormente en el punto 7-4, la misma sería:

$$T_j - T_a = PD \times (R\theta_{jc} + R\theta_{cs} + R\theta_{sa})$$

$$R\theta_{sa} = \frac{T_j - T_a}{PD} - (R\theta_{jc} + R\theta_{cs})$$

Reemplazando los valores, donde la  $R\theta_{cs}$  sale de la hoja de datos, obtenemos:

$$R\theta_{sa} = \frac{131,5^\circ\text{C} - 40^\circ\text{C}}{33,6W} - (0,64^\circ\text{C}/\text{W} + 0,24^\circ\text{C}/\text{W}) = 1,84^\circ\text{C}/\text{W}$$

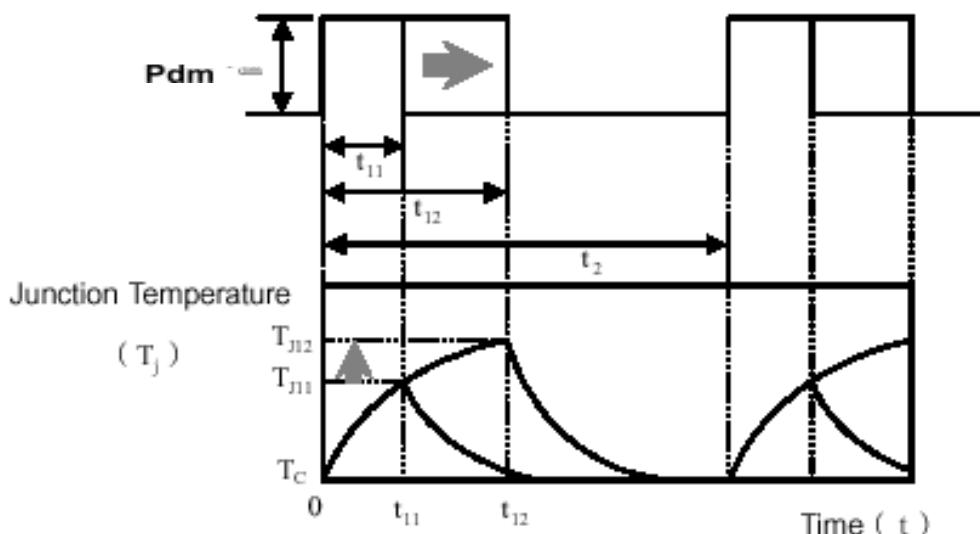

### 7-5. Transient Thermal Impedance (Z<sub>thjc</sub>)

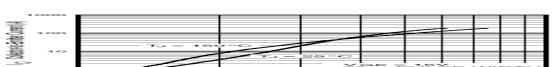

La impedancia térmica de juntura- carcaza sale de la curva de la figura 6 de la hoja de datos, mostrada en el ejercicio del punto 7-3-3, la misma está en función del ancho de un pulso rectangular ( $t_1$ ) bajo diferentes ciclos de actividad (D). Dicho gráfico tiene una escala normalizada en base a la resistencia térmica de juntura – carcaza ( $R\theta_{jc}$ ). De la curva se pueden deducir los siguientes límites:

$$\lim_{t \rightarrow 0} Z_{thJC}(t) = 0 \quad \lim_{t \rightarrow \infty} Z_{thJC}(t) = R_{thJC}$$

La  $Z_{thjc}$  determina el pico de la temperatura de juntura, definida en la siguiente ecuación:

$$T_j = PDM \times (R\theta_{jc} \times Z_{thjc}) + T_c$$

Para determinar el valor absoluto del pico de la temperatura de juntura, es necesario conocer la temperatura de carcaza bajo condiciones de operación de estado estable, porque la inercia térmica del disipador responde solamente al promedio de la disipación de potencia.  $T_c$  es por lo tanto dada por:

$$T_c = T_a + (R\theta_{cs} + R\theta_{sa}) \times P_{av}$$

La ecuación puede ser usada para determinar cuanta más potencia puede ser disipada en un sistema termal conocido o para hallar la temperatura de juntura para un juego de condiciones eléctricas de operación.

La disipación de potencia es normalmente dividida en conducción y conmutación. Las perdidas de conducción se calculan:

$$P_{av} = V_{ce(on)} \times I_c \times D$$

La siguiente figura muestra como incrementa la temperatura de juntura cuando incrementa el ciclo de actividad.

La curva para un pulso simple (Sthjc) determina la impedancia termal para pulsos de potencia repetitivos teniendo un ciclo de actividad constante como muestra la siguiente ecuación:

$$Z_{thjc}(t) = R_{\theta JC} \cdot D + (1 - D) \cdot S_{thjc}(t)$$

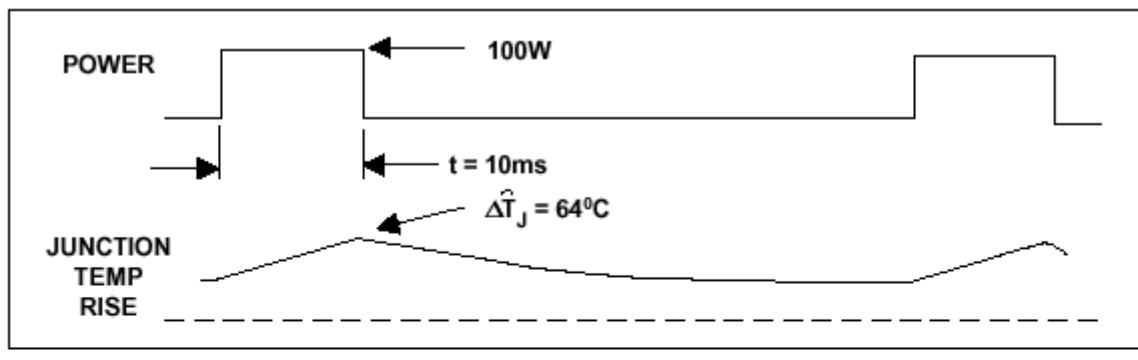

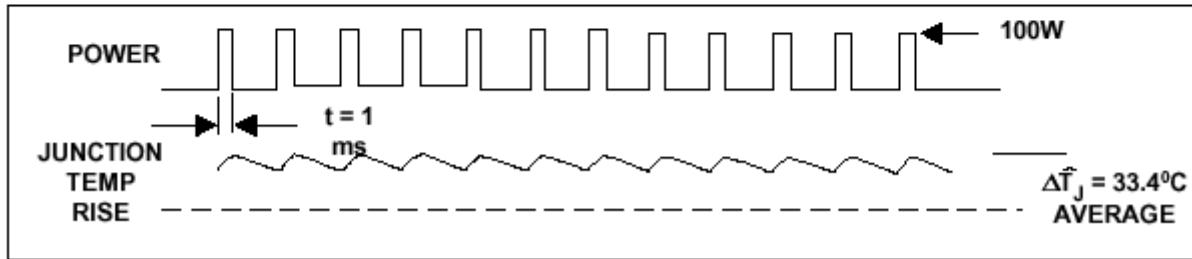

Cuando la frecuencia es muy baja, la curva de respuesta termal transitoria es usada. La razón para esto es ilustrada en las dos figuras siguientes, donde ambas tienen la misma disipación de potencia y ciclo de actividad, pero diferentes frecuencias de operación. La primera presenta fluctuaciones ciclo por ciclo de temperatura de juntura a 20 Hz claramente mayores que a 200 Hz. Cuando la frecuencia incrementa, la temperatura de juntura responde mas al promedio que al pico. Para frecuencias por encima de unos pocos KHz y ciclos de actividad por arriba del 20%, las fluctuaciones se tornan pequeñas y el pico de la temperatura de juntura se iguala al promedio de la disipación de potencia multiplicada solo por la  $R\theta jc$ .

(a)  $t = 10 \text{ ms } D = 0.2$ (b)  $t = 1 \text{ ms } D = 0.2$

**Ejercicio)** En un circuito circula una corriente rectangular repetitiva cuya amplitud es de 50 A. La temperatura ambiente es de 40 °C. Calcular el disipador adecuado.

- A- El ancho del pulso es de 10  $\mu\text{s}$  y el ciclo de actividad es del 1%.

- B- El ancho del pulso es de 500  $\mu\text{s}$  y el ciclo de actividad es del 50%.

EMBED Excel.Sheet.8

De la figura 2 de la hoja de datos interceptando la curva de la  $T_j = 150 \text{ }^{\circ}\text{C}$  que es el peor caso nos da una  $V_{ce(on)} = 3,8 \text{ V}$ .

La potencia por pulso es:  $50 \text{ A} \times 3,8 \text{ V} = 190 \text{ W}$ .

Caso A)

La impedancia térmica transitoria de la figura 6 de la hoja de datos nos da: 0,015.

La diferencia de temperatura entre juntura y carcaza es:

$$\Delta T = PD \times R\theta_{jc} \times Z_{thjc} = 190 \text{ W} \times 0,64 \text{ }^{\circ}\text{C/W} \times 0,015 = 1,8 \text{ }^{\circ}\text{C}$$

La máxima temperatura de carcaza permisible es:

$$T_{cmax} = T_{jmax} - \Delta T = 150 \text{ }^{\circ}\text{C} - 1,8 \text{ }^{\circ}\text{C} = 148,2 \text{ }^{\circ}\text{C}$$

La diferencia de temperatura entre carcaza y el ambiente es:

$$T_c - T_a = 148,2 \text{ } ^\circ\text{C} - 40 \text{ } ^\circ\text{C} = 108,2 \text{ } ^\circ\text{C}$$

La disipación de potencia promedio es:

$$P_{av} = PD \times D = 190 \text{ W} \times 0,01 = 1,9 \text{ W}$$

El disipador sería:

$$R_{\theta sa} = \frac{150 \text{ } ^\circ\text{C} - 40 \text{ } ^\circ\text{C}}{1,9 \text{ W}} - (0,64 \text{ } ^\circ\text{C/W} + 0,24 \text{ } ^\circ\text{C/W}) = 57 \text{ } ^\circ\text{C / W}$$

De acuerdo al resultado obtenido no sería necesario usar disipador.

Caso B)

La impedancia térmica transitoria de la figura 6 de la hoja de datos nos da: 0,35.

La diferencia de temperatura entre juntura y carcaza es:

$$\Delta T = PD \times R_{\theta jc} \times Z_{th jc} = 190 \text{ W} \times 0,64 \text{ } ^\circ\text{C/W} \times 0,35 = 42,6 \text{ } ^\circ\text{C}$$

La máxima temperatura de carcaza permisible es:

$$T_{cmax} = T_{jmax} - \Delta T = 150 \text{ } ^\circ\text{C} - 42,6 \text{ } ^\circ\text{C} = 107,4 \text{ } ^\circ\text{C}$$

La diferencia de temperatura entre carcaza y el ambiente es:

$$T_c - T_a = 107,4 \text{ } ^\circ\text{C} - 40 \text{ } ^\circ\text{C} = 67,4 \text{ } ^\circ\text{C}$$

La disipación de potencia promedio es:

$$P_{av} = PD \times D = 190 \text{ W} \times 0,5 = 95 \text{ W}$$

El disipador sería:

$$R_{\theta sa} = \frac{150 \text{ } ^\circ\text{C} - 40 \text{ } ^\circ\text{C}}{95 \text{ W}} - (0,64 \text{ } ^\circ\text{C/W} + 0,24 \text{ } ^\circ\text{C/W}) = 0,3 \text{ } ^\circ\text{C / W}$$

De acuerdo al resultado obtenido es importante usar disipador.

## 7-6. Electrical Characteristics

### 7-6-1. Tensión de breakdown entre colector y emisor (V(br)ces)

Este parámetro garantiza el límite inferior de la distribución de la tensión breakdown. Es definido en términos de una corriente de fuga y tiene un coeficiente de temperatura positivo listado en la hoja de datos como  $\Delta V(br)ces / \Delta T_j$  esto implica que un dispositivo

con una tensión de breakdown a 25 °C tendrá una tensión diferente a otra temperatura definida por la siguiente ecuación.

$$V(br)ces[Tj] = V(br)ces[Tj=25°C] + \alpha \times (Tj - 25°C)$$

|                                 | Parameter                               | Min. | Typ. | Max. | Units | Conditions                    |

|---------------------------------|-----------------------------------------|------|------|------|-------|-------------------------------|

| $V_{(BR)CES}$                   | Collector-to-Emitter Breakdown Voltage③ | 1200 | —    | —    | V     | $V_{GE} = 0V, I_C = 250\mu A$ |

| $\Delta V_{(BR)CES}/\Delta T_J$ | Temperature Coeff. of Breakdown Voltage | —    | 1.20 | —    | V/°C  | $V_{GE} = 0V, I_C = 1.0mA$    |

③ Pulse width  $\leq 80\mu s$ ; duty factor  $\leq 0.1\%$ .

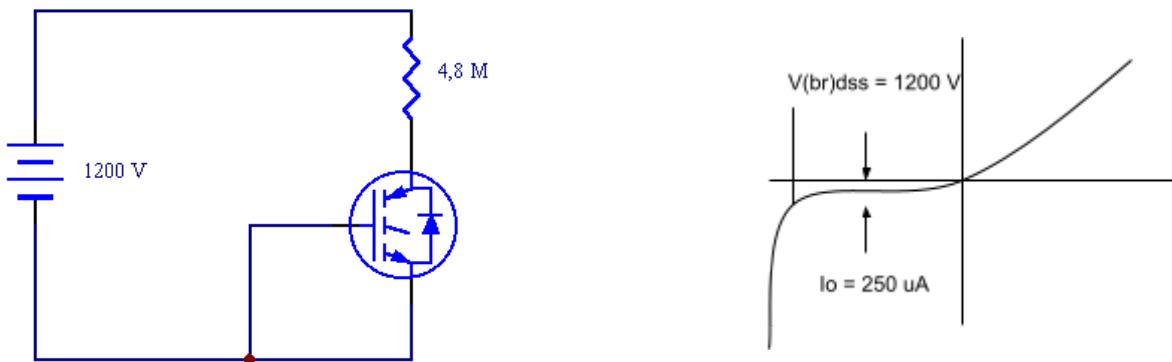

**Ejercicio)** Indicar el circuito y los valores de sus componentes que determinen la tensión de breakdown.

¿La prueba debe realizarse con o sin disipador? Explicar.

Cual sería la tensión de breakdown a una temperatura de -55 °C.

El transistor siempre está apagado por lo tanto el diodo queda polarizado en inversa, superado el valor de 250  $\mu A$  entra en avalancha.

La circulación de corriente genera calor, el aumento de calor provoca un aumento de corriente embalándose térmicamente por lo tanto la prueba debe realizarse con disipador para evacuar el calor evitando así que entre en avalancha.

La tensión de breakdown a -55 °C sería:

$$V(br)ces[Tj = -55°C] = 1200 V + 1.2 V/°C \times (-55°C - 25°C) = 1200 V - 96 V = 1104 V$$

### 7-6-2. Tensión de breakdown entre emisor y colector ( $V(br)ecs$ )

Este parámetro caracteriza la tensión inversa de avalancha de la juntura indeterminada entre colector y base del transistor PNP.

La relevancia de esta especificación y su energía inversa de avalancha asociada puede ser mejor comprendida con la ayuda de la siguiente figura.

Cuando el transistor T2 se apaga, la corriente que circula por la carga es transferida al diodo asociado al transistor complementario, en este caso D1.

La  $di/dt$  desarrollada en la inductancia parásita que está en serie con el diodo genera un pico de tensión inverso a través del IGBT.

Esta tensión es típicamente inferior a los 10 V, aunque tensiones superiores pueden resultar de  $di/dt$  muy altas o por un pobre layout del circuito impreso.

De la hoja de datos del IRG4PH50U de similares características del IGBT estudiado pero sin el diodo interno, vemos el valor máximo de  $V(br)ecs$ .

|               |                                          |    |   |   |   |                           |

|---------------|------------------------------------------|----|---|---|---|---------------------------|

| $V_{(BR)ECS}$ | Emitter-to-Collector Breakdown Voltage ④ | 18 | — | — | V | $V_{GE} = 0V, I_C = 1.0A$ |

|---------------|------------------------------------------|----|---|---|---|---------------------------|

④ Pulse width  $\leq 80\mu s$ ; duty factor  $\leq 0.1\%$ .

### 7-6-3. Tensión de saturación entre colector y emisor ( $V_{ce(on)}$ )

Es un factor importante para determinar las perdidas de conducción del dispositivo, es la caída de tensión cuando la corriente de colector está circulando en su valor requerido por la carga.

Cuando la corriente de colector es baja, tiene características de coeficiente de temperatura negativo y cuando es alta, tiene coeficiente positivo.

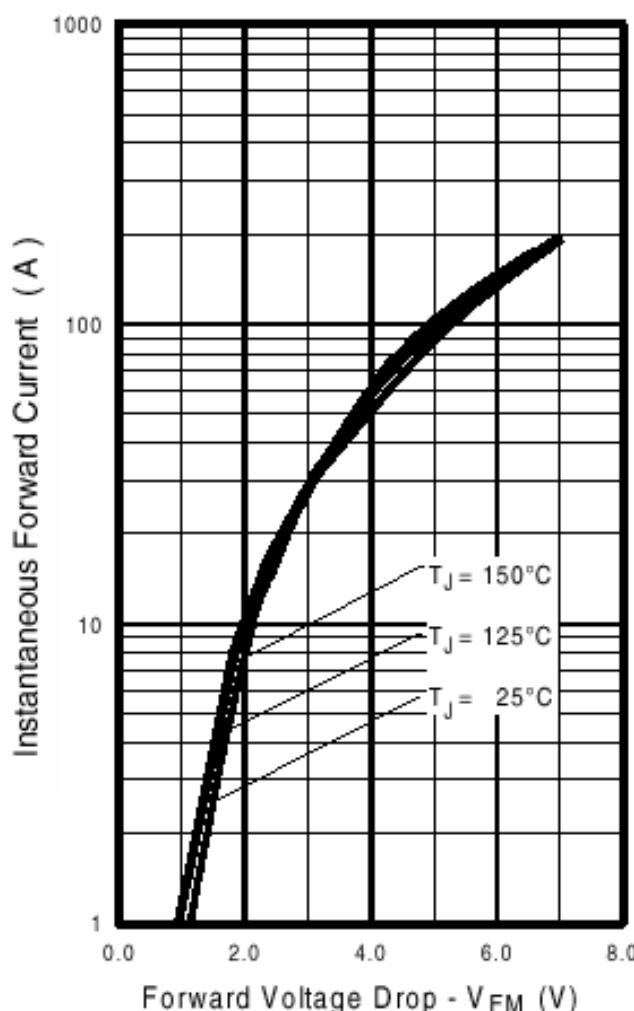

En las hojas de datos vienen dos figuras que proveen una caracterización detallada en temperatura (figura 5) y corriente (figura 2), las mismas se muestran a continuación.

**Ejercicio)** Hallar la  $V_{ce(on)}$  para una  $I_c$  de 10 A y una  $I_c$  de 100 A.

Con la ayuda de la figura 2 de la hoja de datos, usamos siempre para el diseño el peor caso.

Para el caso de una  $I_c = 10$  A se intercepta con la curva de  $T_j = 25$  °C y nos da una  $V_{ce(on)} = 2,6$  V.

Para el caso de una  $I_c = 100$  A se intercepta con la curva de  $T_j = 150$  °C y nos da una  $V_{ce(on)} = 5$  V.

#### 7-6-4. Tensión de umbral entre emisor y gate ( $V_{ge(th)}$ )

Este es el rango de tensión en el gate en el cual la corriente de colector comienza a fluir. La variación en la tensión de threshold con la temperatura también es especificado como  $\Delta V_{ge(th)} / \Delta T_j$ , llevando a una reducción en la tensión a temperaturas altas.

#### 7-6-5. Transconductancia directa ( $g_{fe}$ )

Este parámetro es medido superponiendo una pequeña variación de alterna en la polarización de la tensión del gate a un valor especificado de corriente de colector por ejemplo para  $I_c @ T_c = 100$  °C.  $g_{fe}$  representa la ganancia de la señal medido en la región lineal. La transconductancia aumenta significativamente con el aumento de la corriente.

|          |                            |    |    |   |   |                            |

|----------|----------------------------|----|----|---|---|----------------------------|

| $g_{fe}$ | Forward Transconductance ④ | 23 | 35 | — | S | $V_{CE} = 100V, I_C = 24A$ |

|----------|----------------------------|----|----|---|---|----------------------------|

④ Pulse width 5.0μs, single shot.

#### 7-6-6. Corriente de corte de colector ( $I_{ces}$ )

Es la máxima corriente de fuga con el emisor y el gate cortocircuitados con su máxima tensión colector – emisor aplicada, complementa al punto 7-6-1. Su valor aumenta significativamente con el aumento de la temperatura.

|           |                                     |   |   |      |         |                                                   |

|-----------|-------------------------------------|---|---|------|---------|---------------------------------------------------|

| $I_{ces}$ | Zero Gate Voltage Collector Current | — | — | 250  | $\mu A$ | $V_{GE} = 0V, V_{CE} = 1200V$                     |

|           |                                     | — | — | 6500 |         | $V_{GE} = 0V, V_{CE} = 1200V, T_j = 150^{\circ}C$ |

#### 7-6-7. Corriente de fuga entre gate y emisor ( $I_{ges}$ )

Es la máxima corriente de fuga con el emisor y el colector cortocircuitados con su máxima tensión gate – emisor aplicada.

|                  |                                 |   |   |      |    |                        |

|------------------|---------------------------------|---|---|------|----|------------------------|

| I <sub>GES</sub> | Gate-to-Emitter Leakage Current | — | — | ±100 | nA | V <sub>GE</sub> = ±20V |

|------------------|---------------------------------|---|---|------|----|------------------------|

### 7-6-8. Caída en directa del diodo (VFM)

Es especificada bajo la máxima corriente en continua IF que puede circular por el diodo en directa como se mencionó en el punto 7-3-5. Como se ve en la figura 13 de la hoja de datos que se detalla a continuación, tiene muy poca variación con la temperatura.

|                 |                            |   |     |     |   |                                              |             |

|-----------------|----------------------------|---|-----|-----|---|----------------------------------------------|-------------|

| V <sub>FM</sub> | Diode Forward Voltage Drop | — | 2.5 | 3.5 | V | I <sub>C</sub> = 16A                         | See Fig. 13 |

|                 |                            | — | 2.1 | 3.0 |   | I <sub>C</sub> = 16A, T <sub>J</sub> = 150°C |             |

### 7-7. Switching Characteristics

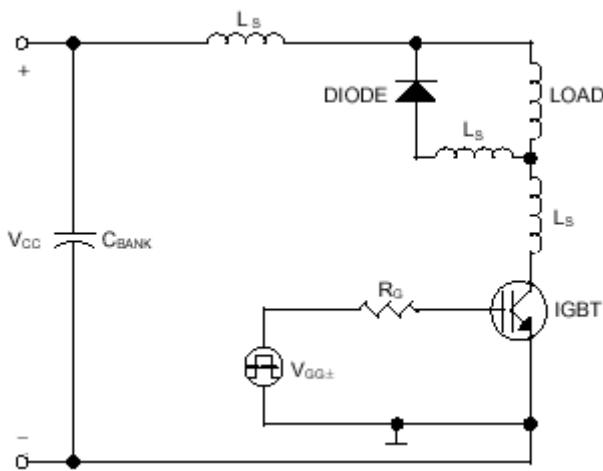

El circuito con carga inductiva con diodo free-wheeling mostrado a continuación es comúnmente encontrado en la electrónica de potencia. Este circuito de prueba nos servirá para testear el comportamiento durante el encendido y el apagado del IGBT. Las formas de onda de conmutación tendrán en cuenta la recuperación inversa del diodo y la inductancia parásita (L<sub>s</sub>).

### 7-7-1. Inductancia interna del emisor (Le)

Esta es la inductancia parásita entre el colector y el emisor medido a una distancia de 5 mm desde el encapsulado. El valor cambia dependiendo de la longitud desde la base del terminal en el chip hasta la unión eléctrica con el cable. Esta inductancia hace mas lento el encendido por una cantidad que es proporcional a la  $di/dt$  de la corriente de colector, tal como lo hace el efecto Miller por una cantidad que es proporcional a la  $dv/dt$  del colector.

|                |                             |   |    |   |    |                           |

|----------------|-----------------------------|---|----|---|----|---------------------------|

| L <sub>E</sub> | Internal Emitter Inductance | — | 13 | — | nH | Measured 5mm from package |

|----------------|-----------------------------|---|----|---|----|---------------------------|

**Ejercicio)** Con una  $dI/dt$  igual a 1000 A/ $\mu$ s. Hallar la tensión desarrollada a través de esta inductancia.

|                             |                        |                                         |     |     |     |                                                              |

|-----------------------------|------------------------|-----------------------------------------|-----|-----|-----|--------------------------------------------------------------|

| EMBE<br>D<br>Equati<br>on.3 | V <sub>GE(th)</sub>    | Gate Threshold Voltage                  | 3.0 | —   | 6.0 | V <sub>CE</sub> = V <sub>GE</sub>   <sub>I = 250A</sub>      |

|                             | ΔV <sub>GE(th)/T</sub> | Temperature Coeff. of Threshold Voltage | —   | .13 | —   | mV/C V <sub>CE</sub> = V <sub>GE</sub>   <sub>I = 250A</sub> |

### 7-7-2. Capacitores interelectródicos del gate

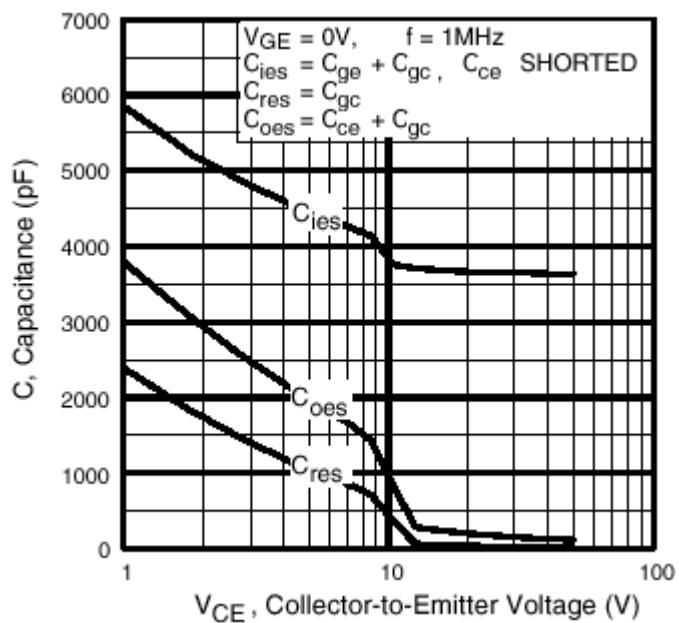

La capacitancia de salida (Coes) tiene una típica dependencia de tensión de una juntura P-N. La capacitancia de transferencia inversa (Cres) también llamada Miller es fuertemente dependiente de la tensión (inversamente proporcional), pero de una manera más compleja que la capacitancia de salida.

La capacitancia de entrada (Cies) la cual es la suma de las capacitancias entre gate – emisor y entre gate - colector, muestra la misma dependencia de la tensión de la capacitancia Miller pero de una manera mas atenuada ya que Cge es mucho más grande e independiente de la tensión.

Como se observa en la figura 7 de la hoja de datos.

**C<sub>gc</sub>****C<sub>ce</sub>****C<sub>ge</sub>**

|           |                              |   |      |   |    |                |            |

|-----------|------------------------------|---|------|---|----|----------------|------------|

| $C_{ies}$ | Input Capacitance            | — | 3600 | — | pF | $V_{GE} = 0V$  | See Fig. 7 |

| $C_{oes}$ | Output Capacitance           | — | 160  | — |    | $V_{CC} = 30V$ |            |

| $C_{res}$ | Reverse Transfer Capacitance | — | 31   | — |    | $f = 1.0MHz$   |            |

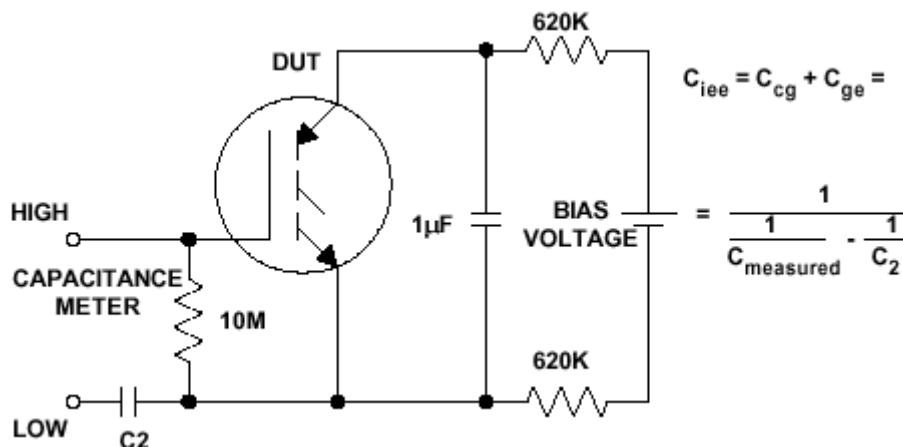

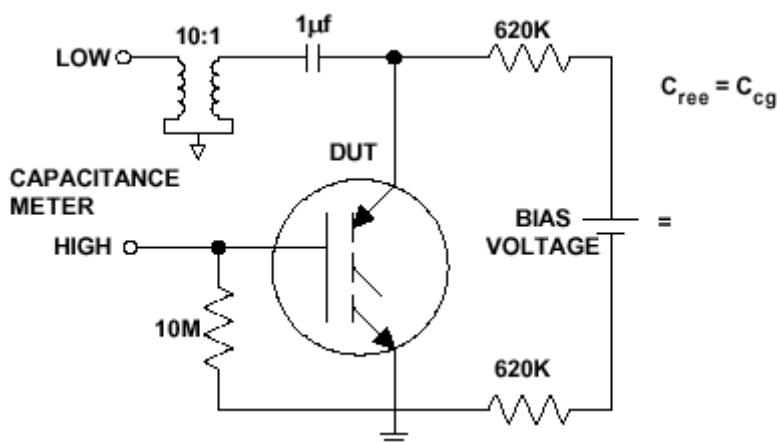

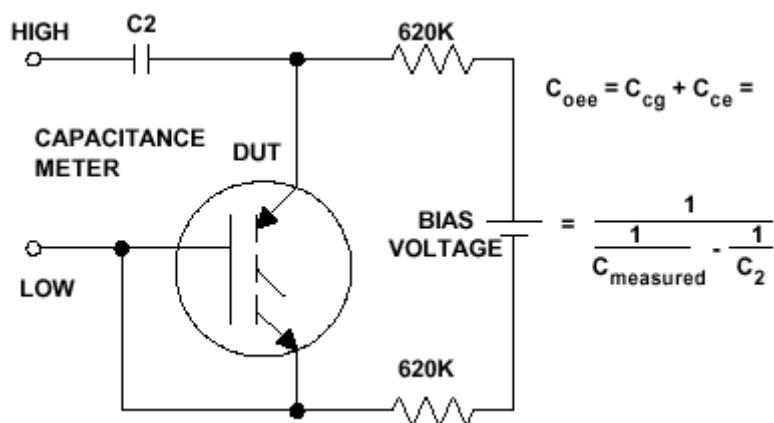

Los circuitos de prueba se muestran a continuación, donde el IGBT es polarizado con 30 V entre colector y emisor. Dos de sus terminales son cortocircuitados en alterna con un capacitor de valor grande. La capacitancia es medida entre estos dos terminales y el tercero.

### 7-7-3. Carga del gate

Los diseñadores no familiarizados comienzan a diseñar el circuito driver basados en los valores de capacitancia de entrada listados en las hojas de datos.

El capacitor entre el gate y el emisor (C<sub>ge</sub>) es afectado en función de la tensión aplicada, pero el capacitor entre el gate y el colector (C<sub>gc</sub>) es mucho más significativo y más difícil de ser tratado porque es una función no lineal afectada por la tensión.

El efecto provocado por este ultimo capacitor interelectrónico es llamado efecto Miller, un fenómeno por el cual un camino de realimentación existe entre la entrada y la salida de un dispositivo, esto afecta la capacitancia dinámica total de entrada generalmente mayor que la suma de los valores estáticos.

El Cgc aunque es un valor más pequeño en valor estático que la Cge, tendrá una excursión de tensión 20 veces mas que este último, por lo tanto el capacitor Miller requerirá mas carga que el capacitor de entrada.

Para evitar estos inconvenientes el fabricante especifica el valor de carga de gate definido como el valor que debe ser aplicado para lograr una completa conmutación durante el encendido.

La carga del gate es el producto de la corriente de entrada ( $I_g$ ) y el tiempo de conmutación ( $t_{sw}$ ), este simple calculo inmediatamente le dice al diseñador cual es la cantidad de corriente necesaria que el driver necesita entregar para lograr el tiempo de conmutación requerido por la etapa de potencia.

El circuito de prueba se logra aplicando una corriente constante al gate del dispositivo, para que la escala de tiempo horizontal sea directamente proporcional a la carga aplicada al gate con un factor de escala adecuado.

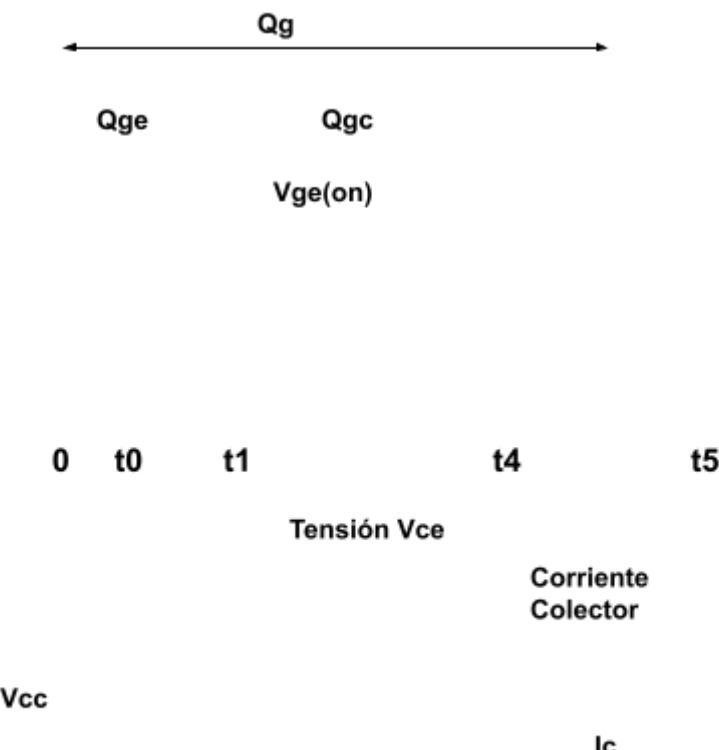

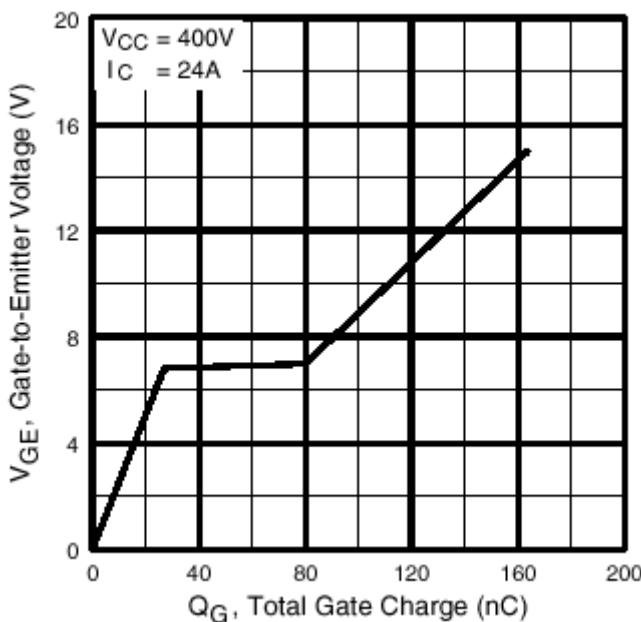

El oscilograma obtenido de la figura 8 de la hoja de datos muestra la tensión de gate versus la carga.

|          | Parameter                         | Min. | Typ. | Max. | Units | Conditions                   |

|----------|-----------------------------------|------|------|------|-------|------------------------------|

| $Q_g$    | Total Gate Charge (turn-on)       | —    | 160  | 250  | nC    | $I_C = 24A$                  |

| $Q_{ge}$ | Gate - Emitter Charge (turn-on)   | —    | 27   | 40   |       | $V_{CC} = 400V$              |

| $Q_{gc}$ | Gate - Collector Charge (turn-on) | —    | 53   | 80   |       | See Fig. 8<br>$V_{GE} = 15V$ |

#### 7-7-4. Potencia promedio entregada por el driver

El dato de la carga del gate lleva al diseñador rápidamente a determinar la potencia promedio del driver.

$$Q_g = I_g \times T_{sw}$$

$$P_{av} = Q_g \times V_g \times f$$

T<sub>sw</sub> = tiempo de conmutación correspondiente a t<sub>5</sub> del gráfico anterior que muestra de una manera simplificada la conmutación durante el encendido.

f = frecuencia de trabajo.

**Ejercicio)** Definir la corriente y la potencia necesaria para obtener una conmutación en el encendido con una T<sub>sw</sub> = 2 μs, para una frecuencia de trabajo 10 KHz.

$$I_g = Q_g / T_{sw} = 250 \text{ nC} / 2 \mu\text{s} = 125 \text{ mA}$$

$$P_{av} = Q_g \times V_g \times f = 250 \text{ nC} \times 15 \text{ V} \times 10 \text{ KHz} = 37,5 \text{ mW}$$

Si fuera necesario colocar un resistor en serie al gate, podemos decir que la V<sub>ge(on)</sub> es de aproximadamente 7 V, entonces:

$$R_g = V_g - V_{ge(on)} / I_g = 15 \text{ V} - 7 \text{ V} / 125 \text{ mA} = 64 \Omega$$

Si fuera necesario mejorar el tiempo de encendido, por ejemplo T<sub>sw</sub> = 200 ns, el driver debe entregar una corriente de 1,25 A.

#### 7-7-5. Resistencia en serie al gate (R<sub>g</sub>)

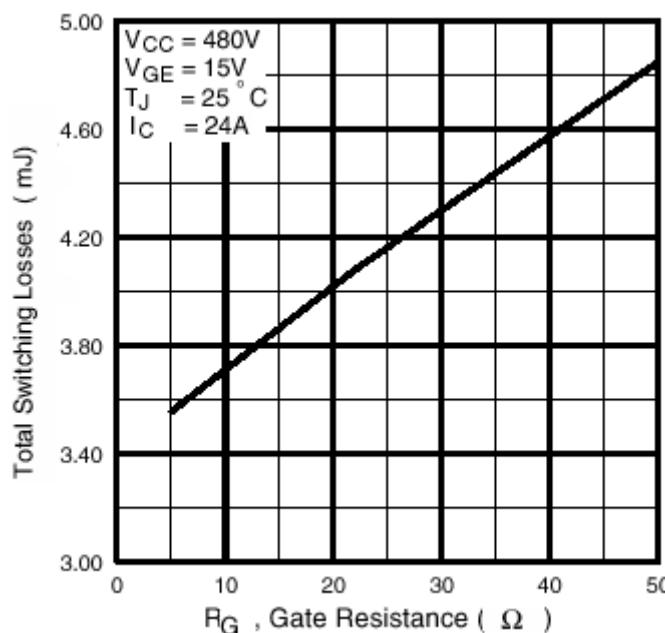

El valor de la resistencia de gate (R<sub>g</sub>) tiene un significativo impacto sobre el funcionamiento dinámico del IGBT. Valores pequeños de R<sub>g</sub> cargan y descargan la capacitancia de entrada más rápido reduciendo los tiempos de conmutación y las

perdidas de conmutación, mejorando la inmunidad a la  $dV/dt$  en el encendido como se ve en figura siguiente que sale de la figura 9 de la hoja de datos.

Sin embargo, una pequeña  $R_g$  puede llevar a oscilaciones entre la capacitancia de entrada y la inductancia parásita de los terminales. Para minimizar este efecto se recomienda conectar entre el gate y el emisor cables retorcidos (twisted wires) o pistas paralelas en un circuito impreso.

Un aumento en la impedancia del driver prolonga el efecto Miller y causa un retardo en la caída de la corriente, como se aprecia en la figura siguiente.

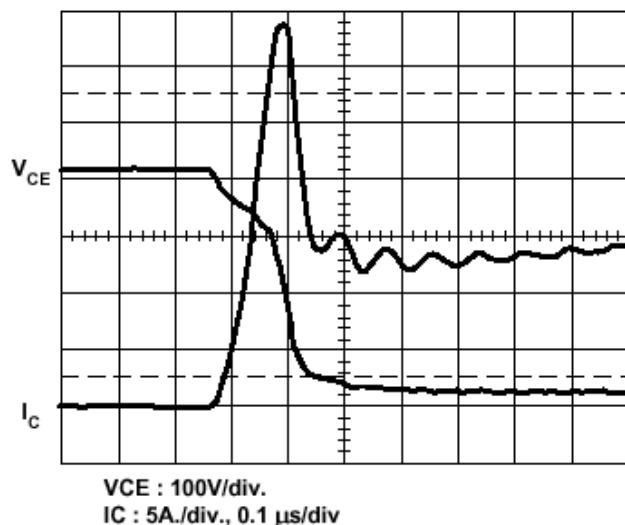

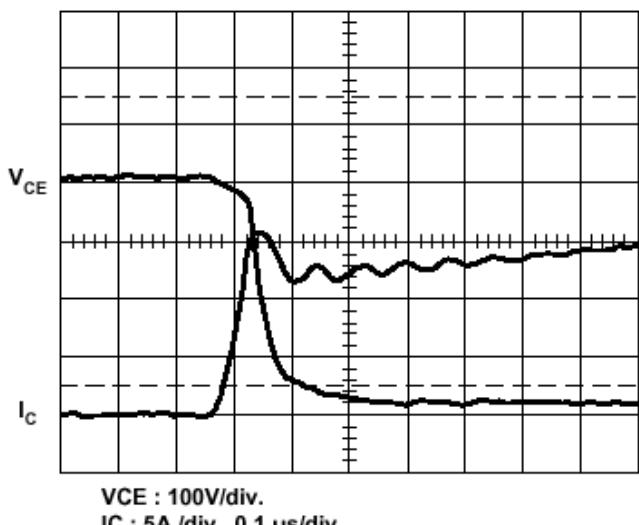

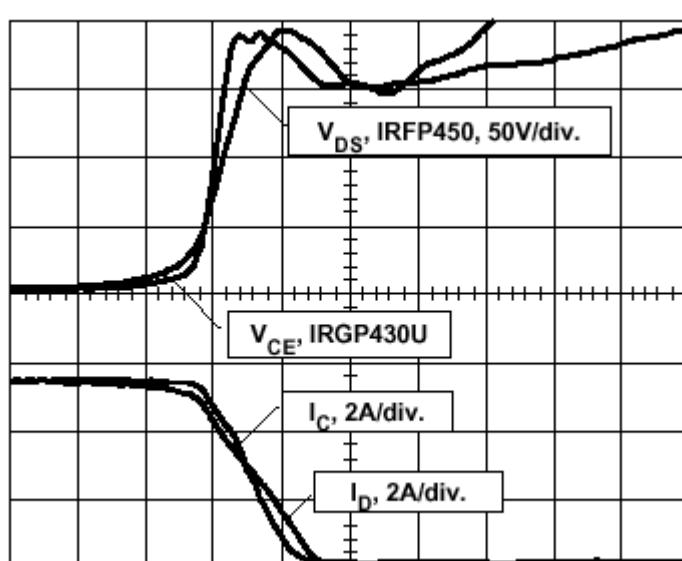

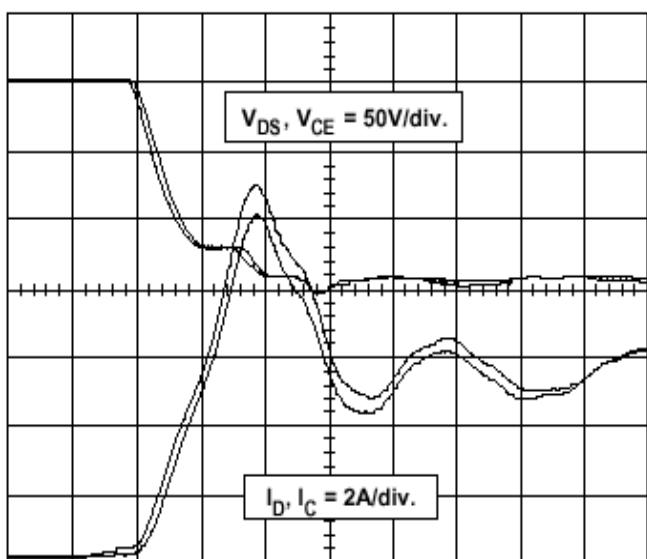

Un valor grande de  $R_g$  hace más lenta la velocidad en el encendido ayudando a reducir el pico de corriente debido a la recuperación inversa del diodo, pero tiene un pequeño efecto en el apagado. A diferencia del MOSFET, la velocidad del apagado del IGBT no puede ser controlada con un resistor en serie en el gate. En las siguientes formas de onda de encendido y apagado respectivamente compara un MOSFET con un IGBT, ambos

comutando 5,5 A a 160 V. Una  $R_g$  de 10 ohm fue usada para el MOSFET y una de 33 ohm para el IGBT. Las formas de onda muestran la misma velocidad de encendido y el rápido apagado del IGBT.

#### 7-7-6. Análisis de la transición durante el encendido y el apagado

## Turn-on

## Turn-off

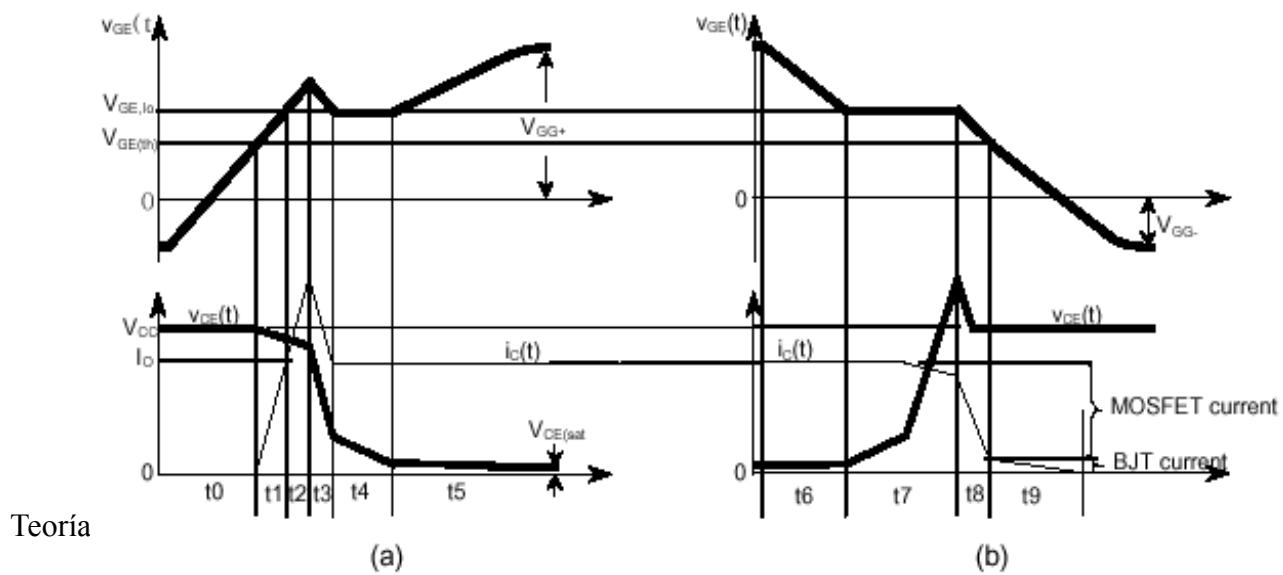

Antes de t0 el dispositivo bajo prueba (DUT) soporta la tensión completa de la fuente aplicada al circuito (Vcc) y la tensión de gate y la corriente de colector están en cero.

Durante la sección t0 la capacitancia de entrada ( $C_{ge} + C_{gc}$ ) comienza a cargarse y la tensión  $V_{ge}$  se incrementa no en forma lineal como se ve en la forma de onda sino exponencialmente con una constante de tiempo determinada por  $R_g(C_{ge} + C_{gc})$ . No fluye corriente en el colector hasta que el gate no alcance la tensión de umbral (threshold).

Durante la sección t1,  $C_{ge}$  continua cargándose y la corriente de colector se incrementa proporcionalmente a medida que la tensión  $V_{ge}$  continua subiendo como lo hacía durante t0. Durante esta condición el diodo freewheeling permanece en conducción, la caída de tensión en él es baja y la caída de tensión a través del DUT continua siendo Vcc.

Durante las secciones t1 y t2, la  $V_{ce}$  aparece levemente inferior a Vcc, esto es debido a la tensión inducida en  $L_s$  durante el incremento de  $I_c$ , siendo su magnitud igual a:

$$V_{Ls} = L_s \times dI_c/dt.$$

Durante las secciones t2 y t3, la corriente de colector alcanza la lo impuesta por la carga, la tensión  $V_{ce}$  comienza a caer. La corriente del diodo, la cual ya comenzó a decrecer desde la sección t1 no cae inmediatamente a cero, debido a la recuperación inversa de la corriente del diodo donde fluye en dirección inversa. Esta corriente es adicionada a  $I_c$  tomando la misma forma de onda, al mismo tiempo la tensión a través del diodo comienza a crecer.

Durante la sección t3,  $C_{gc}$  se descarga absorbiendo la corriente del driver y la descarga de corriente proveniente de  $C_{ge}$ , al final de esta sección la recuperación inversa del diodo se detiene.

Durante la sección t4, como la tensión de gate está relacionada con la corriente de colector a través de su característica de transferencia, permanece constante debido a que la  $I_c$  también permanece constante, por lo tanto la  $C_{ge}$  no consumirá mas carga.

Como la caída de tensión  $V_{ce}$  es relativamente grande es aquí el porque la carga de  $C_{gc}$  es mayor que para  $C_{ge}$ .

Durante la sección t5, la  $V_{ce}$  cae a su valor de saturación. Ahora la tensión del gate no está mas relacionada por su característica de transferencia con la  $I_c$ , y es libre de incrementar su carga hasta llegar a la tensión de gate ( $V_{gg}$ ) aplicada al circuito driver donde típicamente es del orden de los 15 V.

La carga total consumida al final del tiempo t4, es la necesaria para conmutar a la tensión Vcc y a la corriente  $I_c$  dadas. La carga adicional consumida después del tiempo t4 no representa carga de conmutación, es simplemente carga en exceso que será entregada por el driver a causa de que la amplitud aplicada al gate normalmente será mayor que la  $V_{ge(on)}$ .

Durante la sección t6, esta es la parte que incluye el mayor retardo de apagado. La  $V_{ge}$  cae desde su amplitud máxima  $V_{gg}$  hasta  $V_{ge(on)}$ . En este tiempo no hay cambios en los valores de  $V_{ce}$  o  $I_c$ .

Durante la sección t7, la tensión Vce comienza a incrementarse, cuya tasa de incremento puede controlarse con el resistor en serie Rg.

Durante la sección t8, Vce se mantiene en el valor de Vcc y la corriente de colector comienza a decrecer, esta pendiente de caída también puede controlarse con Rg. Al igual que durante el periodo de encendido, hay una sobretensión ( $V_{LS} = dIc/dt \times L_s$ ) que es provocada por las inductancias parásitas de los terminales, dicho efecto es adicionado a la tensión Vce. La corriente del MOSFET interno desaparece en esta sección, la cual es la primera de las dos secciones antes de que Ic caiga a cero.

Durante la sección t9, la corriente del PNP interno desaparece y esta corriente es comúnmente llamada corriente 'tail'. Dicha corriente no es controlada por Rg. La misma existe debido a la recombinación de portadores minoritarios (lagunas) que han sido inyectadas dentro de la región drift N- durante el encendido. Debido a la existencia de esta región, las características de conmutación son inferiores comparadas con un transistor de potencia MOSFET.

Del gráfico podemos deducir las siguientes ecuaciones:

Durante el tiempo t0 a t1:

$$V_{ge(on)} \times C_{ge} = I_g \times t_1 = Q_{ge}$$

Durante el tiempo t1 a t4:

$$[V_{CC} - V_{ce(on)}] \times C_{gc} = I_g \times (t_4 - t_1) = Q_{gc}$$

$$\frac{dV_{cg}}{dt} = \frac{dV_{ce}}{dt} = \frac{I_g}{C_{gc}} = \frac{V_{gg} - V_{ge(on)}}{R_g \times C_{gc}}$$

Durante la sección t7:

$$\frac{dV_{ce}}{dt} = \frac{V_{ge(on)}}{R_g \times C_{res}}$$

Durante la sección t8:

$$\frac{dI_c}{dt} = g_{fe} \times \frac{V_{ge(on)}}{R_g \times C_{ies}}$$

A continuación se aprecia como actúa la corriente del driver aplicada al gate del IGBT.

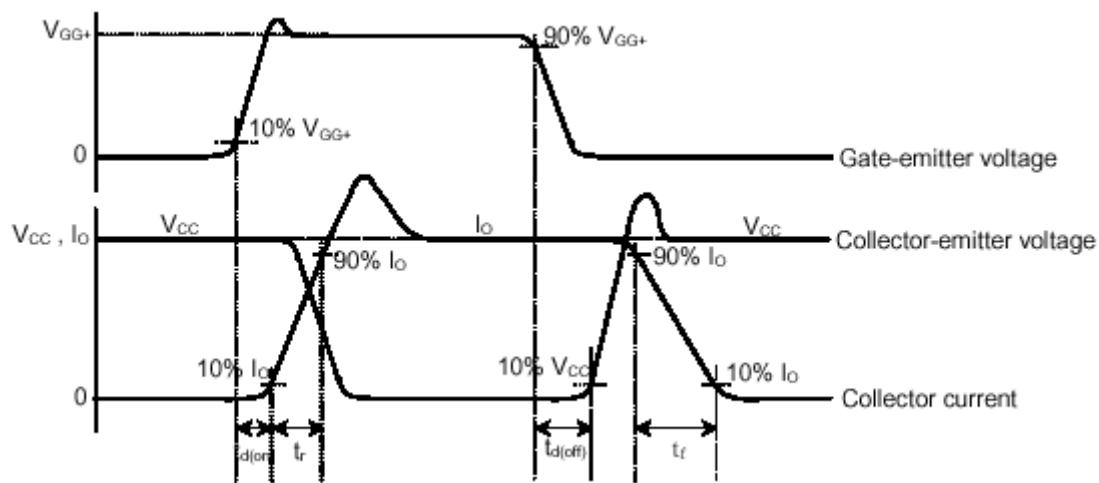

### 7-7-7. Tiempos de conmutación

Los tiempos de conmutación son divididos en 4 secciones, ellos son especificados para temperaturas de juntura de 25 y 150 °C bajo condiciones de carga inductiva. El circuito de prueba que se ve en la figura 18a de la hoja de datos es el siguiente.

#### **td(on) (Turn-On Delay Time)**

El tiempo que le toma a la corriente de colector alcanzar el 10 % de la corriente de carga ( $I_o$ ) desde que el pulso del gate fue inyectado (10 % de  $V_{gg}$ ).

#### **tr (Rise Time)**

El tiempo que le toma a la corriente de colector alcanzar el 90 % de lo desde su 10 %. Cualquier variación en la  $I_c$  después de este punto no es considerada.

### **td(off) (Turn-Off Delay Time)**

El tiempo que le toma a la tensión colector –emisor alcanzar el 10 % de  $V_{cc}$  desde que el pulso del gate fue removido (90 % de  $V_{gg}$ ).

### **tf(Fall Time)**

El tiempo que le toma a la corriente de colector alcanzar el 10 % de lo desde su 90 %. Se ignora la sección donde la tensión de colector tiene una sobretensión y tampoco la corriente de tail, donde es menor al 10 % de lo.

Los tiempos de conmutación proveen una referencia de diseño muy ventajosa para establecer el tiempo muerto (deadtime) apropiado entre el apagado y el subsiguiente encendido del dispositivo complementario en una configuración semipuente y además el ancho de pulso mínimo y máximo. Ellos proveen una indicación poco confiable para hallar las perdidas de conmutación, debido a que la corriente tail es una parte significativa de la energía durante el apagado, la caída de tensión tampoco está caracterizada apropiadamente.

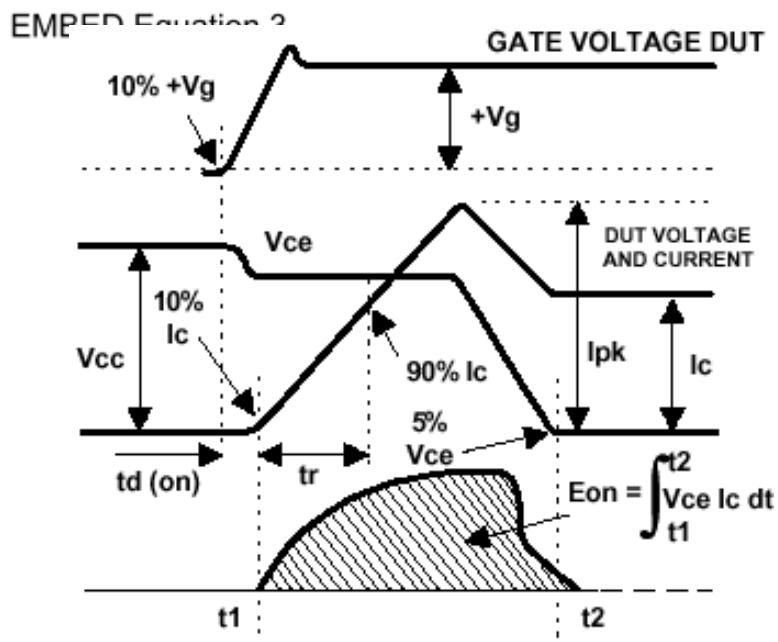

### **7-7-8. Energía de conmutación**

No es suficiente para calcular las perdidas de conmutación solamente con los tiempos de conmutación, ya que hay regiones que no son tenidas en cuenta. Las especificaciones de energía de conmutación son indicadas para compensar esas regiones.

La  $E_{off}$  permitirá a los diseñadores compensar la región donde la tensión colector – emisor tiene una sobretensión y la corriente tail del colector está fuera del tiempo de caída ( $t_f$ ) durante el apagado.

La  $E_{on}$  compensará la región donde la tensión colector – emisor cae durante el encendido.

Se trabaja con el 5 % porque es un compromiso razonable entre la resolución del instrumental y la necesidad de tener en cuenta la quasi saturación que puede ocurrir en algunos dispositivos.

### Eon (Turn-Switching Loss)

Es la cantidad total de energía durante el encendido bajo una carga inductiva, incluye las perdidas introducidas por la recuperación inversa del diodo. En la práctica es medido desde el 5 % de la corriente de colector cuando comienza a subir hasta el 5 % de la tensión colector – emisor antes de caer a cero, para excluir cualquier perdida por conducción.

### Eoff (Turn-Off Switching Loss)

Es la cantidad de energía total durante el apagado bajo una carga inductiva. En la práctica es medido desde el 5 % de la tensión colector – emisor cuando comienza a subir hasta el 5 % de la corriente de colector antes de caer a cero adicionándole 5  $\mu s$ .

EMBED Equation.3

### Ets (Total Switching Loss)

Solo incluye las perdidas de energía en la región de conmutación y es expresada como la suma de  $E_{on}$  y  $E_{off}$ .

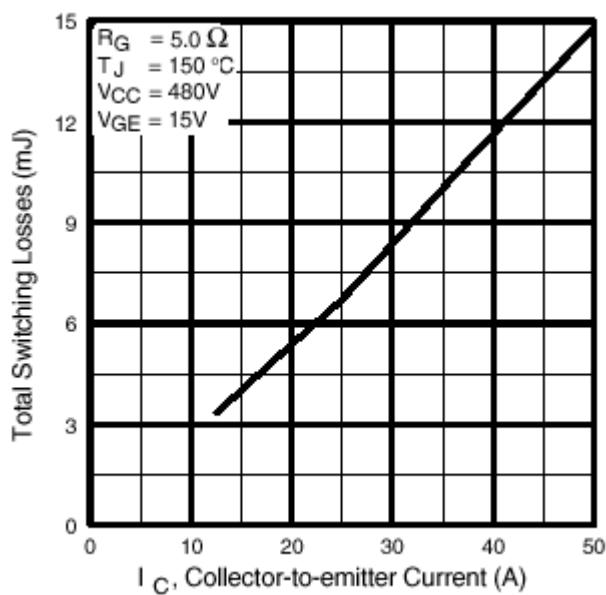

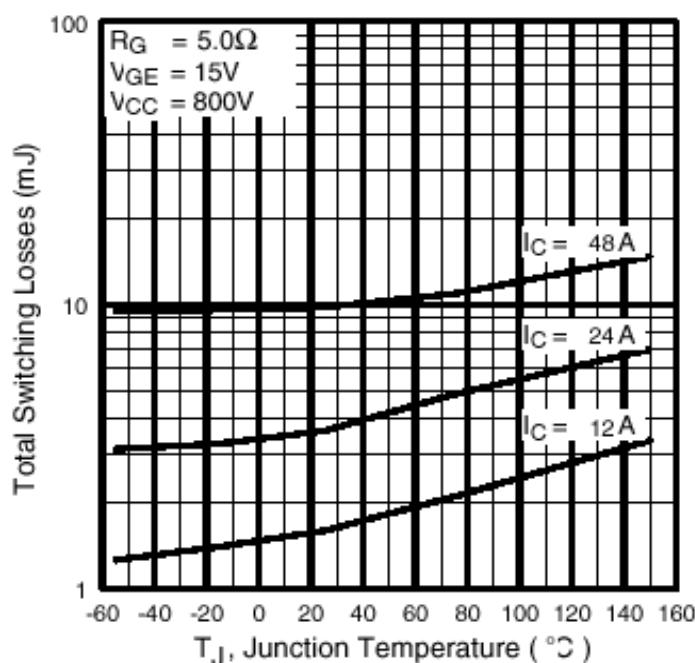

Generalmente crece con el incremento de la resistencia de gate ( $R_g$ ), la temperatura de juntura ( $T_j$ ) y la corriente de colector ( $I_c$ ).

Las mismas se encuentran en las hojas de datos respectivamente como las figuras 9, 10 y 11.

La primera fue mostrada en el punto 7-7-5.

|              |                         |   |      |     |    |                                                                                |

|--------------|-------------------------|---|------|-----|----|--------------------------------------------------------------------------------|

| $t_{d(on)}$  | Turn-On Delay Time      | — | 47   | —   | ns | $T_J = 25^\circ\text{C}$                                                       |

| $t_r$        | Rise Time               | — | 24   | —   |    | $I_C = 24\text{A}, V_{CC} = 800\text{V}$                                       |

| $t_{d(off)}$ | Turn-Off Delay Time     | — | 110  | 170 |    | $V_{GE} = 15\text{V}, R_G = 5.0\Omega$                                         |

| $t_f$        | Fall Time               | — | 180  | 260 |    | Energy losses include "tail" and diode reverse recovery.<br>See Fig. 9, 10, 18 |

| $E_{on}$     | Turn-On Switching Loss  | — | 2.10 | —   | mJ | $T_J = 150^\circ\text{C}$ , See Fig. 11, 18                                    |

| $E_{off}$    | Turn-Off Switching Loss | — | 1.50 | —   |    | $I_C = 24\text{A}, V_{CC} = 800\text{V}$                                       |

| $E_{ts}$     | Total Switching Loss    | — | 3.60 | 4.6 |    | $V_{GE} = 15\text{V}, R_G = 5.0\Omega$                                         |

| $t_{d(on)}$  | Turn-On Delay Time      | — | 46   | —   |    | Energy losses include "tail" and diode reverse recovery.                       |

| $t_r$        | Rise Time               | — | 27   | —   | ns | See Fig. 11, 18                                                                |

| $t_{d(off)}$ | Turn-Off Delay Time     | — | 240  | —   |    | $I_C = 24\text{A}, V_{CC} = 800\text{V}$                                       |

| $t_f$        | Fall Time               | — | 330  | —   |    | $V_{GE} = 15\text{V}, R_G = 5.0\Omega$                                         |

| $E_{ts}$     | Total Switching Loss    | — | 6.38 | —   | mJ | Energy losses include "tail" and diode reverse recovery.                       |

### 7-7-9. Características del diodo

La construcción física de un IGBT a diferencia del MOSFET no presenta un diodo parásito, por lo tanto el mismo es incorporado entre el colector y el emisor en antiparalelo cuyas ventajas serán utilizadas en diversas aplicaciones.

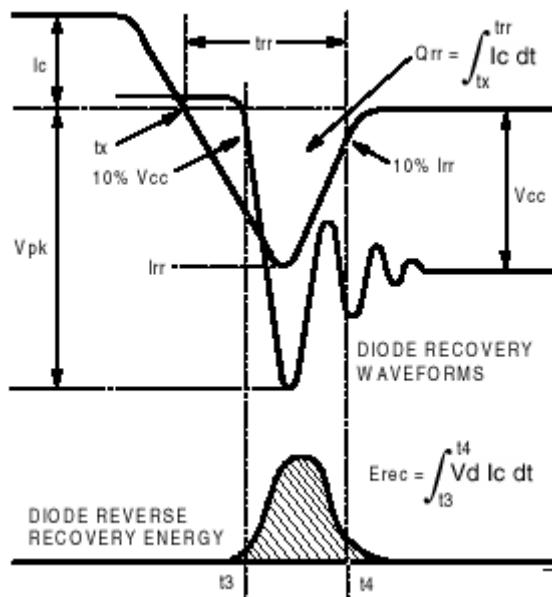

Para entender sus características utilizaremos la siguiente figura que se puede hallar en la figura 18d de la hoja de datos.

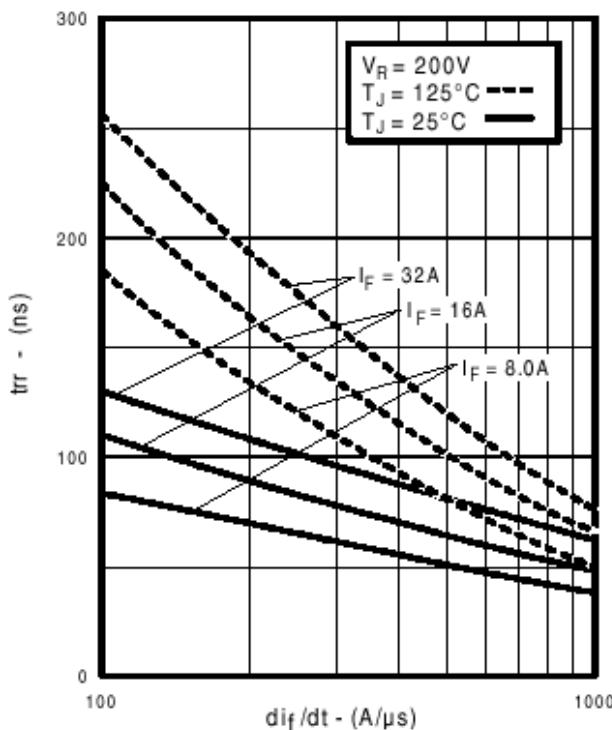

#### trr (Tiempo de recuperación inversa del diodo)

Es el tiempo necesario para que las cargas almacenadas en la zona de la juntura del diodo sean removidas cuando el dispositivo se está apagando. El tiempo es medido a partir de que la corriente cayo a cero hasta el 10 % antes de volver a cero. Depende de la caída de la  $dif/dt$ , cuanto más abrupta sea esta, mas corto será el tiempo trr.

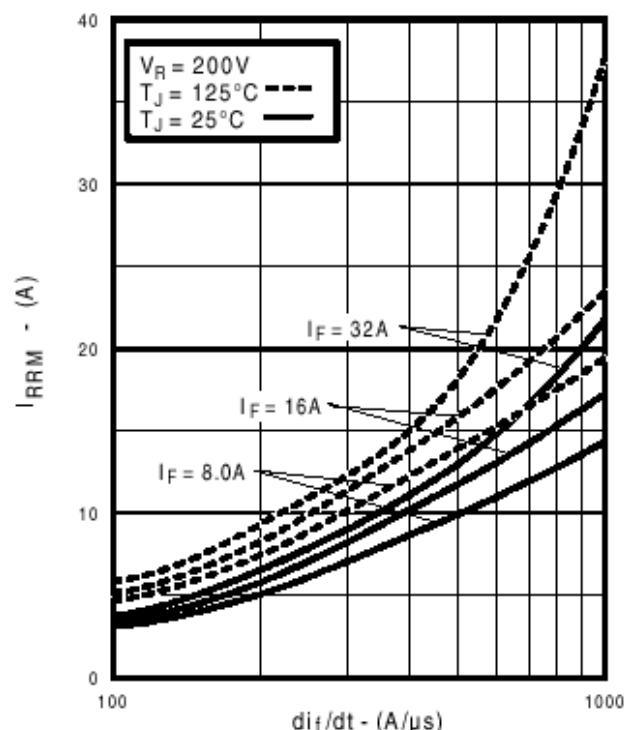

#### Irr (Corriente de recuperación inversa del diodo)

Es la corriente pico de recuperación, la cual depende de la caída de la  $dif/dt$ . Una pendiente abrupta hará que la Irr sea mayor comparada con una pendiente lenta.

A continuación vemos las figuras 14 y 15 de las hojas de datos donde respectivamente el trr y la Irr varían apreciablemente con la dif/dt y también su variación con la temperatura de juntura.

Con una pendiente suave el tiempo trr se hace mucho mayor a temperaturas de juntura elevadas, en cambio con una pendiente abrupta, la que se hace mucho mayor es la corriente pico Irr con la elevación de Tj.

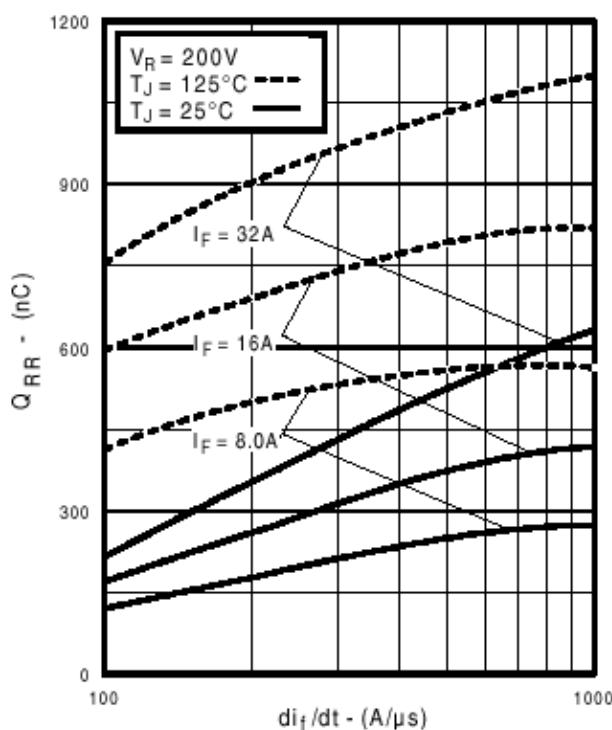

### **Qrr (Carga de recuperación inversa del diodo)**

Las cargas almacenadas durante el periodo de recuperación es el área encerrada por Irr y trr. Donde se puede deducir la siguiente formula:

$$Qrr = 0,5 \times Irr \times trr$$

Cuando la frecuencia de conmutación incrementa, la dif/dt del apagado también lo hace. Esto causa un incremento en la corriente pico Irr, aumentando las perdidas de potencia y adicionando mas ruido al circuito.

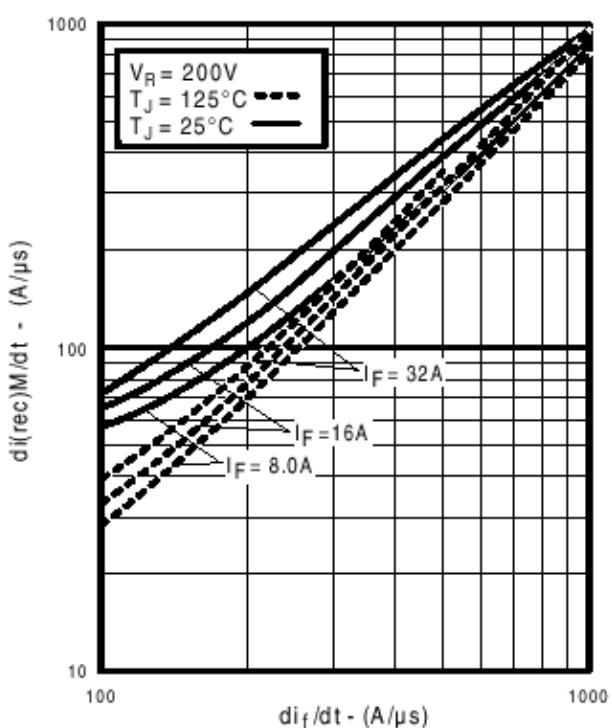

### **di(rec)M/dt (Tasa pico de crecimiento de recuperación del diodo)**

La misma define la pendiente de subida una vez que la corriente de caída llegó a Irr y retorna a cero

A continuación veremos las figuras 16 y 17 de las hojas de datos que comparan estas ultimas características con la dif/dt.

En la figura 17 se aprecia que las curvas son casi lineales al igual que con la variación de la temperatura de juntura, la cual prácticamente no varia.

|                  |                                                     |   |     |      |            |                           |          |                                                     |

|------------------|-----------------------------------------------------|---|-----|------|------------|---------------------------|----------|-----------------------------------------------------|

| $t_{rr}$         | Diode Reverse Recovery Time                         | — | 90  | 135  | ns         | $T_J = 25^\circ\text{C}$  | See Fig. | $I_F = 16A$<br>$V_R = 200V$<br>$di/dt = 200A/\mu s$ |

|                  |                                                     | — | 164 | 245  |            | $T_J = 125^\circ\text{C}$ | 14       |                                                     |

| $I_{rr}$         | Diode Peak Reverse Recovery Current                 | — | 5.8 | 10   | A          | $T_J = 25^\circ\text{C}$  | See Fig. |                                                     |

|                  |                                                     | — | 8.3 | 15   |            | $T_J = 125^\circ\text{C}$ | 15       |                                                     |

| $Q_{rr}$         | Diode Reverse Recovery Charge                       | — | 260 | 675  | nC         | $T_J = 25^\circ\text{C}$  | See Fig. |                                                     |

|                  |                                                     | — | 680 | 1838 |            | $T_J = 125^\circ\text{C}$ | 16       |                                                     |

| $di_{(rec)}M/dt$ | Diode Peak Rate of Fall of Recovery<br>During $t_b$ | — | 120 | —    | A/ $\mu$ s | $T_J = 25^\circ\text{C}$  | See Fig. |                                                     |

|                  |                                                     | — | 76  | —    |            | $T_J = 125^\circ\text{C}$ | 17       |                                                     |

## 8. Referencias

Internacional Rectifier

STMicroelectronics

Fairchild Semiconductor

Concept

Unitrode

Hitachi

Onsemi